本应用笔记描述了意法半导体开发的首款指令缓存(ICACHE)和数据缓存(DCACHE)。

在 Arm Cortex-M33 处理器的 AHB 总线中引入的 ICACHE 和 DCACHE 嵌入到下表中列出的 STM32 微控制器(MCU)中。

这些缓存使用户从内部和外部存储器提取指令和数据时或在用于外部存储器的数据流量时提高应用性能并降低功耗。本文档提供了典型示例,以强调 ICACHE 和 DCACHE 功能,并便于配置

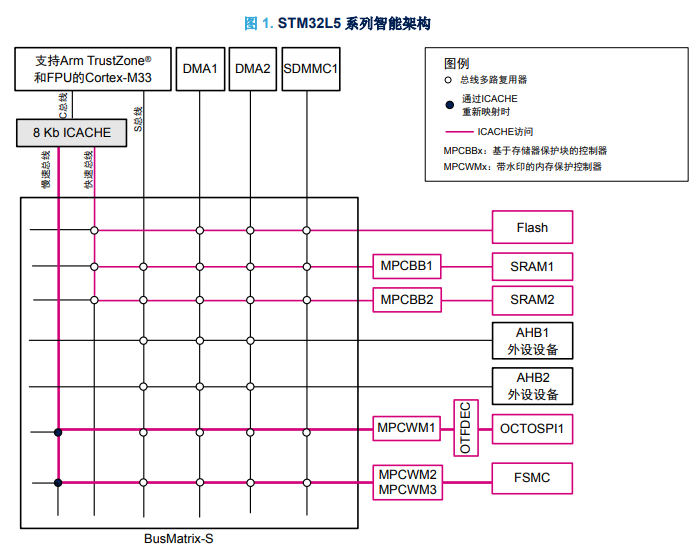

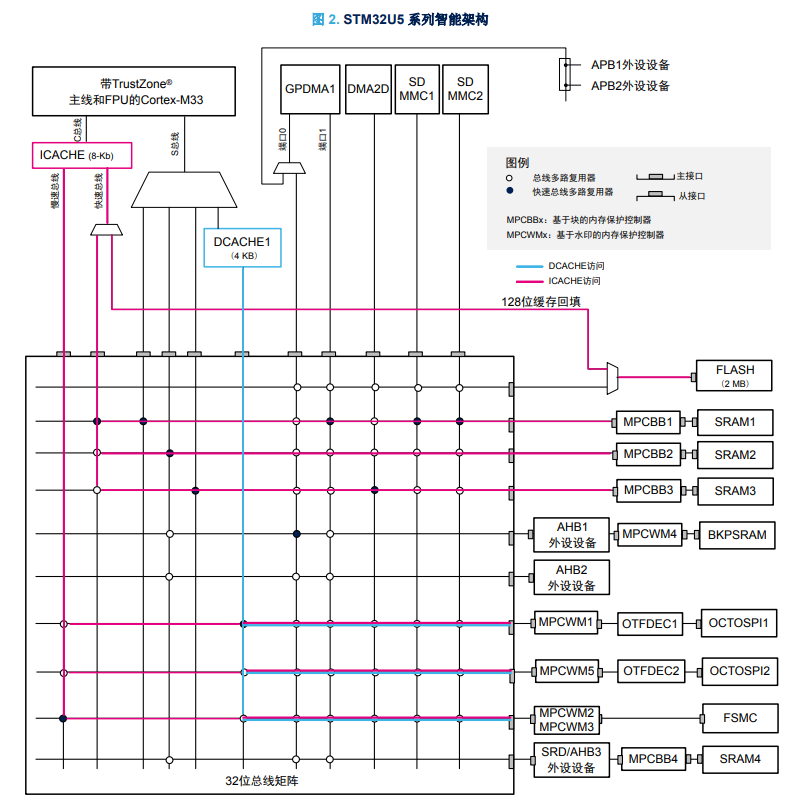

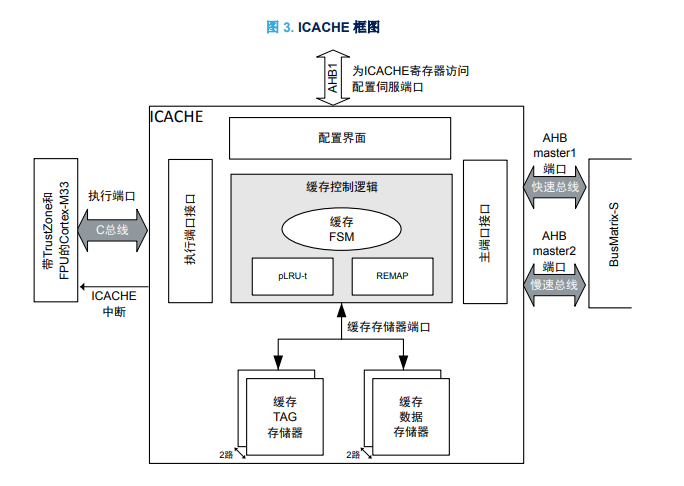

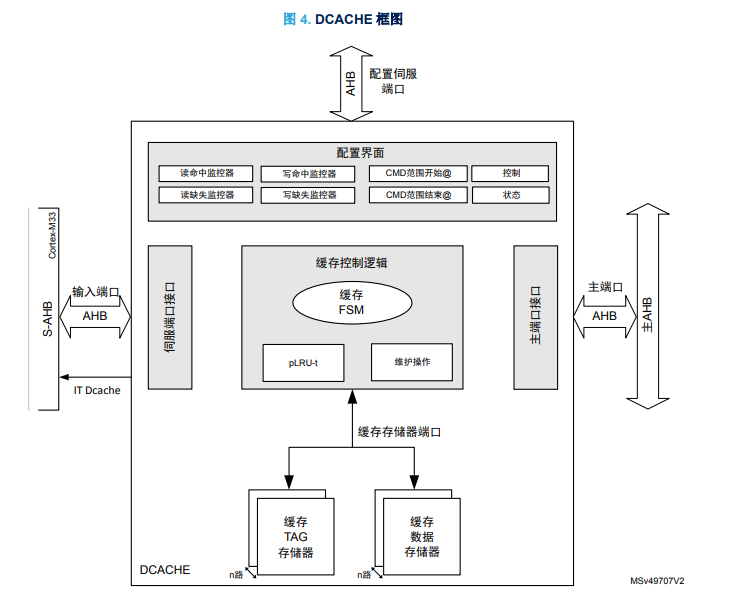

1.ICACHE 和 DCACHE 概述 本节概述了嵌入在基于 STM32 Arm Cortex内核的微控制器中的 ICACHE 和 DCACHE 接口。详细介绍了 ICACHE 和 DCACHE 框图架构以及在系统架构中的集成。 1.1 STM32L5 系列智能架构 此架构基于总线矩阵,允许多个主设备(Cortex-M33、DMA1/2 和 SDMMC1)访问多个从设备(如Flash 存储器、SRAM1/2、OCTOSPI1 或 FSMC)。 下图描述了 STM32L5 系列智能架构。 由于将 8-Kb 的 ICACHE 接口引入其 C-AHB 总线,通过快速总线从内部存储器(Flash 存储器、SRAM1 或SRAM2)或通过慢速总线从外部存储器(OCTOSPI1 或 FSMC)提取代码或数据时,Cortex-M33 的性能有所提升。 1.2 STM32U5 系列智能架构 此架构基于总线矩阵,允许多个主设备(Cortex-M33、GPDMA1、DMA2D 和SDMMC1/2)访问多个从设备(如 Flash 存储器、SRAM1/2/3/4、BKPSRAM、OCTOSPI1/2 或 FSMC)。 下图描述了 STM32U5 系列智能架构。 其 C-AHB 总线引入了 8-Kb 的 ICACHE 接口,通过快速总线从内部存储器(Flash 存储器、SRAM1、SRAM2 或SRAM3)或通过慢速总线从外部存储器(OCTOSPI1、OCTOSPI2 或 FSMC)提取代码或数据时,Cortex-M33 的性能有所提升。其 S-AHB 总线引入了 4-Kb 的 DCACHE 接口,提高了外部存储器(OCTOSPI1、OCTOSPI2 或 FSMC)的数据流量。 1.2 ICACHE 框图 ICACHE 框图如下图所示: ICACHE 存储器包括: • 具有以下元素的 TAG 存储器: – 指示将哪些数据包含在缓存数据存储器中的地址标签 – 有效位 • 数据存储器,包含缓存的数据 1.4DCACHE 框图 DCACHE 框图如下图所示。 DCACHE 存储器包括: • 具有以下元素的 TAG 存储器: – 指示将哪些数据包含在缓存数据存储器中的地址标签 – 有效位 特权位 – dirty 位 • 数据存储器,包含缓存的数据