先进封装时代,那些传统OSAT封测厂怎么办?

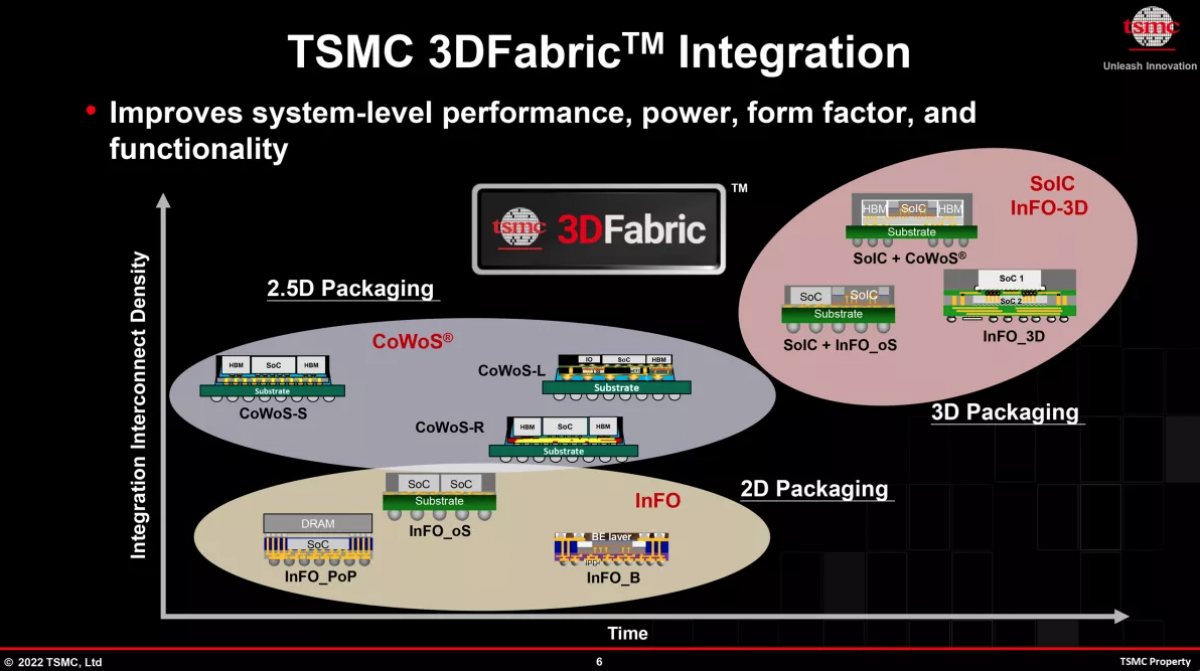

最近,台积电准备将CoWoS封装技术的产能从每月8000片wafer,提升到今年底的11000 WPM;而到2024年底则要到20000WPM。英伟达将占据其中一半的产能,据说AMD也在寻求额外的CoWoS产能。数据中心的通用加速GPU应当是个中主力,包括最近热度颇高的AMD Instinct MI300和英伟达H100。

前不久台积电刚刚开启了先进后道Fab 6工厂(Advanced Backend Fab 6),针对前道3D堆叠SoIC技术(包括CoW和WoW)和后道3D封装技术(InFO和CoWoS)做产能扩充。这家工厂的部分能力和产能对于多chiplet封装与测试很重要。

目前台积电CoWoS(Chip-on-Wafer-on-Substrate)先进封装技术最大的客户就是英伟达和AMD,两者占到CoWoS产能的大约七八成,随后是博通(Broadcom)大约有10%的占比;其余产能由大约20家fabless芯片设计企业共享。先进封装技术是需要特别的生产设备的,据说关键设备的交期已经达到3-6个月,则台积电扩充CoWoS技术的产能也可能受到了一定的限制。

已经谈到过,先进封装技术的本质,是缓解原本芯片制造前道(front-end)流程的瓶颈——也就是器件微缩不再那么容易;转而借助后道(back-end)流程上的创新,来持续摩尔定律的辉煌。这个过程实际是某种程度发生了价值重心的变迁的。

原来基本由OSAT(outsourced semiconductor assembly and test companies)传统封测企业做封装的模型发生了很大变化,因为先进封装要求复杂技术和先进工艺,传统OSAT的参与度如何是个问题。

而在即将发布的今年7月刊封面故事里,我们还将提到chiplet和先进封装技术,对于芯片设计流程和价值链的变革:上游IP供应商的角色可能发生变化。这些都是新技术给行业带来的颠覆,而且是在潜移默化中发生的。

借着即将与先进封装上游设备制造商探讨相关技术与行业革新的机会,我们先来概括性地谈谈先进封装技术在行业中的发展情况。恰好。这些数据将更有利于我们理解其发展阶段。

不同封装技术的市场价值

对于先进封装技术感兴趣的读者,仍然建议阅读《电子工程专辑》去年的封面故事文章,其中对不同的先进封装技术做了比较详尽的解读。从广义上来看,“先进封装”的本质,在于以显著更高密度的I/O来进行封装——具体接触点间距密集到何种程度算是“先进”,似乎并没有明确标准。而部分狭义的“先进封装”定义,只在2.5D/3D封装方案。

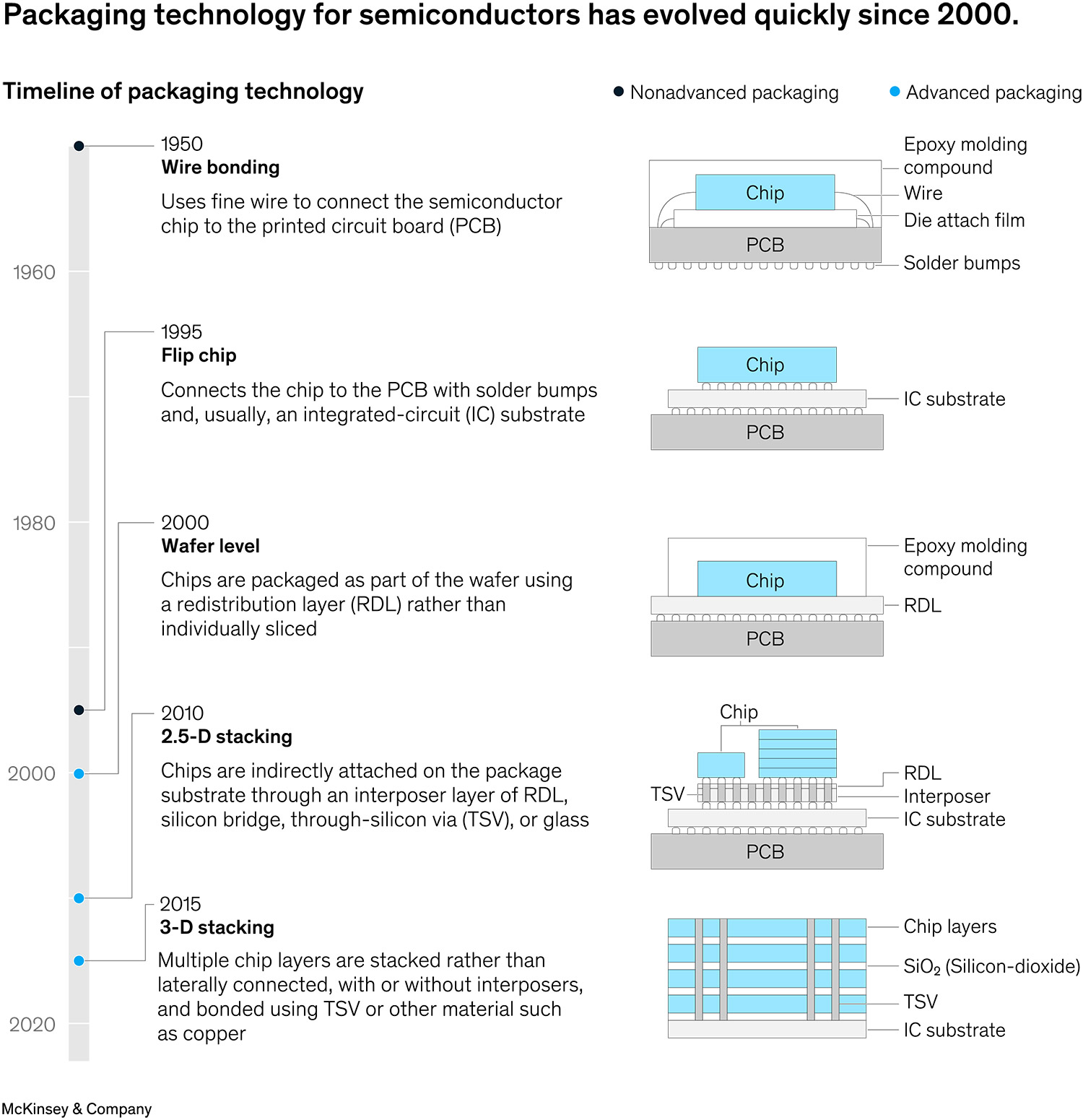

现在普遍的认知是2.5D、3D封装必然属于先进封装范畴,另外技术文章里经常提到的扇出型(Fan-out)封装也属于先进封装——我们这次参与SEMICON China的很多厂商都准备跃跃欲试地聊fan-out技术。这里我们再借助麦肯锡的图,做个简单的解释。

来源:

来源:

“封装”也就是产品做好了以后,要包装起来。对于芯片而言,不光是密封确保内部die的可靠性,在die或者理解为一片硅造出来以后,要用某种方法令其与外部世界互通,包括供电、信号互联。早年用引线键合(wire bonding)方案来达成内部芯片与外部PCB的互联,需要用到焊球、金属线——这是一种很直观的封装方式。

麦肯锡的数据是,预计到2031年,引线键合市场价值会达到160亿美元,从现在到2031年的CAGR(年复合增长率)为2.9%。

后来发展出了芯片倒装(flip chip)技术,就是在die造好之后,翻个面——即原本在底下的晶体管到了上面,而原本在上的金属互联层在下方——通过所谓的bump凸起连接到封装基板上。某些企业会将bump间距较小的封装也称作“先进封装”。实际上芯片倒装也是后续诸多先进封装技术的基础,它实现了更小的间距、更高的I/O密度。

倒装工艺在电脑、手机的CPU、SoC等芯片上很常见。麦肯锡数据为当前芯片倒装市场价值在270亿美元,2030年会达到450亿美元。

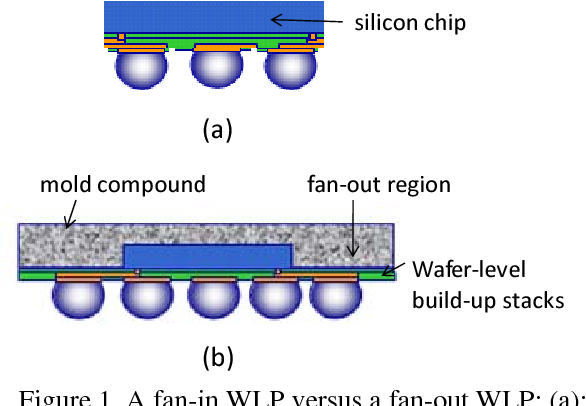

此后出现的WLP(wafer-level packaging,或WLCSP)晶圆级封装,顾名思义是在晶圆级(而不是在切割之后单独的die级)就进行电气连接布局。WLP相比更早期倒装方案的差异,在于die和PCB之间的substrate,换成了RDL(redistribution layer,重新分布层),可达成更小的封装、更好的导热性。

来源:Fan, Xuejun. “Wafer level packaging (WLP): Fan-in, fan-out and three-dimensional integration.” 2010 11th International Thermal, Mechanical & Multi-Physics Simulation, and Experiments in Microelectronics and Microsystems (EuroSimE) (2010): 1-7.

WLP有两种形式,fan-in和fan-out(如上图)。麦肯锡在文章中说,fan-in的WLP封装通常用于低端手机之类的应用,RDL层路径通往die中央。而在fan-out扇出型封装方案里,RDL层的边界超出die范围之外,其I/O的整体路径从die引出,到RDL层扩散开去,RDL层扩展到die以外的部分叫“fan-out区域”,所以叫“扇出型”。

典型方案如台积电的InFO(Integrated Fan-Out)晶圆级封装。此前JCET做过一个Fan-In和Fan-Out WLP封装工艺流程的动画视频,。其实Fan-Out虽然叫WLP晶圆级封装,但在流程上首先还是要把做好的die从wafer上切下来;但切下来的这些die还要再放到新的载体wafer上再做后续操作…具体的就不展开了。

麦肯锡数据,fan-out型WLP封装市场价值大约为15亿美元。汽车、移动、网络设备和HPC高性能应用是此类高级封装方案的常客。目前最大的WLP技术供应商就是台积电。

2.5D封装是在此基础上,将更多片的die借助某个中介(比如硅中介silicon interposer)连起来,集成到同一个封装内。现在比较知名的2.5D封装技术典型如采用硅中介的CoWoS-S(台积电);用硅桥(silicon bridge)的CoWoS-L(台积电)和EMIB(Intel);RDL层本身也可以作为中介层,CoWoS-R就是其中代表。

麦肯锡还提到下一代中介层材料的glass(玻璃?),据说可在高频带宽的前提下达成低成本和低功率损耗。

而3D堆叠自然就是将die在垂直方向叠起来,除了用microbump和TSV的堆叠方案之外,还有hybrid bonding混合键合,此前我们也不止一次撰文探讨过了。

几类市场参与者扮演的不同角色

对于领先的IDM和foundry厂而言,先进封装也成为重要的卖点。,2022年年度营收中7%来自先进封装。虽然台积电预期今年的先进封装占比仍然会在6-7%之间,未来的增长潜力还是相当大的。

我们现在听到先进封装,大约首先冒出来的名字就是台积电、Intel、三星、日月光等。实际上这些技术的投入,也不是一朝一夕的。而其他市场参与者要追赶就显得很困难。加上这些技术要求相当的产品经验,没有量的积累也很难起得来,就进一步加剧了技术差距。

比如2.5D和3D封装,需要掌握的技术基础就是interposer中介层和hybrid bonding混合键合技术能力。Interposer需要对应的材料与生产制造技术方法;而hybrid bonding则涵盖CMP(化学机械平台化)、极高的互联精度,在设备和know-how方面都是需要积累的。此前我们采访Intel,Intel就提到。

另外值得一提的是,先进封装的封装设计需要在最初架构阶段就做考量——尤其如果加入chiplet,则设计不同阶段的整体“左移”都对各环节参与者提出了新的要求,如此才能从整个系统的角度确保设计的可靠与高效。这同时意味着芯片设计客户对相应的先进封装技术供应商有着更高的粘性。

麦肯锡在报告中提到,对于foundry厂而言,要获得高价值的fabless客户,就需要协同开发先进封装解决方案:在芯片架构设计阶段和最初针对设计验证的shuttle run时,就可能需要协同开发。麦肯锡表示,由于高性能芯片以及封装导致的芯片设计复杂度提升,这样的合作会变得越来越重要。

所以对于非头部,但掌握一定先进封装技术的foundry厂(被麦肯锡称作fast followers)来说,将自己摆在,从设计阶段就针对先进封装帮助客户生产产品的位置,会很重要。除此之外,还需要寻求design house的帮助,从IP开发到设计和制造,design house都将扮演重要角色,包括RTL设计、所需的功能高层级描述,以及逻辑测试和布局布线。还有就是要具备一站式交付能力。

在先进封装技术的问题上,主要的参与者很显然囊括有三个角色:逻辑与存储芯片IDM、具备先进或成熟工艺的foundry厂、OSAT。事实上,比较符合直觉的情况是:更早部署先进封装技术,而且已经处在领跑位置的参与者(典型如台积电、Intel,恰好对应了前两个角色;另外还有这里没怎么谈的是应用3D堆叠先进技术的存储器制造商),必然是战局里的赢家,即便初期产能受限,可能会成为其阻碍。

而更多拥有部分先进封装技术能力的跟随者,也能获得市场,只不过在高端解决方案上并不会那么容易就获得稳定的客源,或者全面掌控设计/制造能力。所以寻求协同合作会很重要。

但其实更多人关心的或许是传统做后道的OSAT封测厂在此扮演什么角色,至少麦肯锡认为,在高端的先进封装市场,OSAT以及技术水平处在较低级别的foundry和IDM,这些角色的发挥空间会很有限。与其直接参与竞争,不如提供对应的低端解决方案或者寻求在某些价值链上做个合作者。即便个别比较领先的OSAT在大量投入以后能够做fan-out扇出型封装方案,2.5D、3D堆栈能力仍然是滞后的。

这其中的合作可以是,和头部有能力做TSV、RDL光刻、hybrid bonding等核心技术的玩家合作,OSAT还是可以继续提供中道到后道的服务和工作,如wafer薄化、bump制造等。

另外如本文第一部分提到的,持续到2030年,传统封装技术仍然是要做的,包括引线键合这种已经存在了几十年的技术。况且并不是什么芯片都得用先进封装——就像现在,先进封装的市场价值仍然没那么高;芯片如果没有量自然也无法承担先进封装现如今的成本。

但显然要在先进封装技术时代分得一杯羹是需要投入的,无论是做先进封装技术本身,还是将其纳入企业未来的发展策略,令自身化作其中的某个环节。不过我们认为,chiplet、异构集成和先进封装的发展,未来可能呈现出新的市场格局;这是技术对于产业链、价值链的变革,未来的不确定性还很大;观察芯片设计上游的新动向,制定新的发展策略,对于制造和封测参与者都十分关键。

先进封装的未来价值

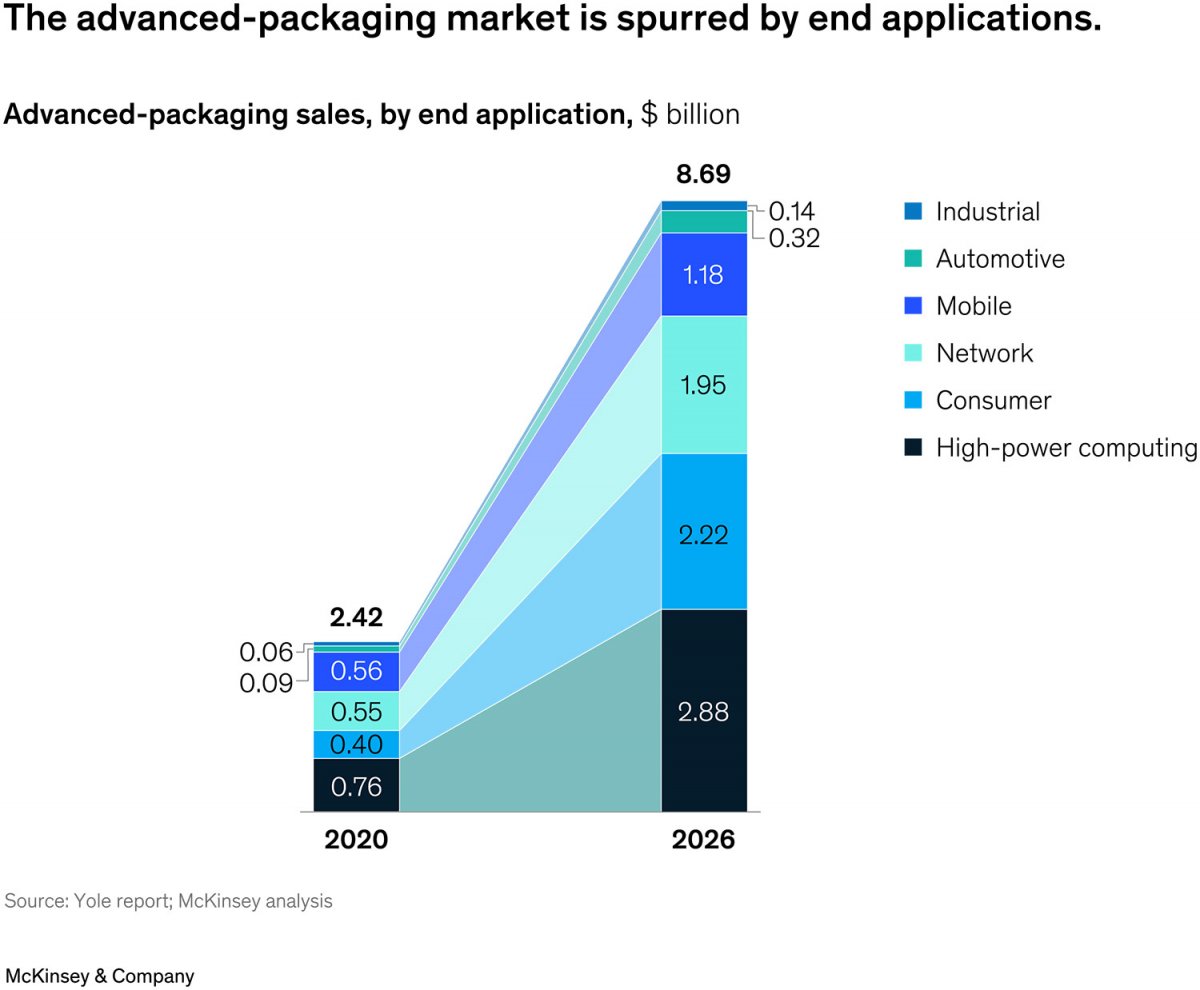

最后给张图,是麦肯锡预测的2026年先进封装在不同应用领域的市场价值变化。其中HPC、网络通信应用主要是来自AI芯片、边缘计算,以及消费电子设备中的网络芯片。毕竟扇出型封装能够给到对应的小尺寸和并不算高的成本。

2.5D封装应用主要来自HPC应用,以数据中心为主。其实Intel最近改变桌面CPU的系列产品命名,将Meteor Lake称作“英特尔酷睿Ultra”第1代处理器,就可以看做PC行业步入2.5D/3D先进封装的标志,不止是数据中心,只不过数据中心服务器芯片仍将是先进封装技术打头阵的先锋——国产的某些GPU、AI芯片都已经开始应用此类方案。

而3D堆叠,存储以及各类加速计算芯片的应用已经进入加速期,毕竟连民用市场的CPU都开始用3D V-Cache了,数据中心GPU上的HBM内存,以及某些大规模AI芯片把电源相关的部分和计算die做堆叠()都不是新鲜事了。这是市场进化的必然。

至于未来产业链的整体变迁,到2026年还可以再做观察。在这个过程里,会有好几类市场参与者都需要对自己的角色做重新审视与定位。

本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。