FPGA亚稳态和毛刺小结

1首先介绍一下建立时间和保持时间的基本概念:

1.1建立时间和保持时间:

图1.1

tsh:建立时间,th:保持时间

建立时间:是指时钟触发器上升沿到来之前,数据稳定不变的时间。如果建立时间不够,则数据不能在这个时钟进入触发器。

保持时间:是指时钟触发器上升沿到来之后,数据保持不变的时间。如果保持时间不够,则数据同样不能被打入触发器。

由于PCB走线时,存在分布电感和电容,所以几纳秒的毛刺将被自然滤除,而在PLD内部决无分布电感和电容,所以在PLD/FPGA设计中,竞争和冒险问题将变的较为突出。

2关于毛刺的基本概念:

信号在FPGA内通过连线和逻辑单元时,都会产生延时。延时产生的原因:①:连线的长短和逻辑单元的数目 ,②:受器件的制造工艺、工作电压、温度等条件的影响, 所 以在信号变化的瞬间,组合逻辑的输出有先后顺序,往往会产生一些尖峰的信号,这些信号称为毛刺。如果有毛刺,该电路称为冒险电路。只由内部电路决定。

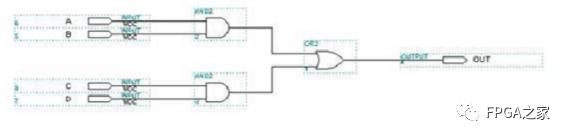

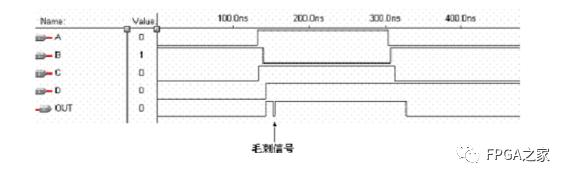

看下面的例子:

我们可以看到,A,B,C,D四个输入信号,最后导致输出出现毛刺。原因是A,B,C,D信号输入不是同时发生。(即使同时发生,它们各自由于连线和逻辑单元的原因,到达门电路的时间也不同。)所以可以说,只要输入信号同时发生变化,由于走线的原因,必将产生毛刺。所以我们不能直接将其输出,要进行一些措施。

方法一:格雷码代替二进制计数器,由于格雷码每次只有一位进行变化,不满足产生毛刺的条件。所以可以减小错误

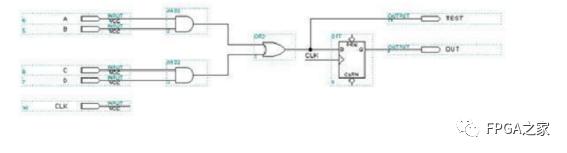

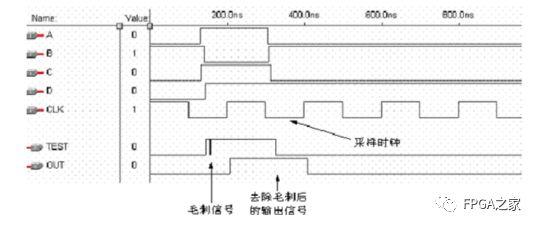

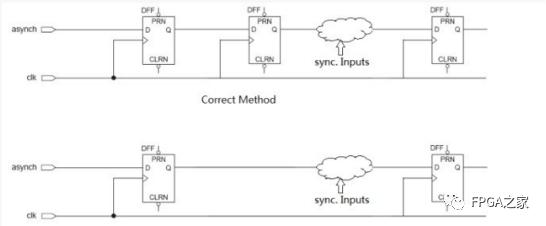

方法二:另一种更常见的方法是利用D触发器的D输入端对毛刺信号不敏感的特点,在输出信号的保持时间内,用触发器读取组合逻辑的输出信号,这种方法类似于将异步电路转化为同步电路。如图:

由于异步输入不是总能满足所馈送的触发器满足建立时间和保持时间,所以常常会产生亚稳态。

3关于亚稳态知识的基本概念

图1.2:采用一个时钟同步下的模型

其中:tco为触发器数据输出延时;Tdelay=Tcomb 为经过组合逻辑的延时 ;Tsetup(tsu)为建立时间;Tpd为时钟延时,一般时钟延时可以忽略。

1.1亚稳态的特点:

①增加触发器进入稳态的时间:

如图 ,如果满足正常建立时间和保持时间,则Tco为触发器的延时。如果违反触发器的时序要求:则会在延时后出现亚稳态时间tR。

②:可能输出毛刺,震荡,或中间电平

经过一段时间后,亚稳态会处于稳定状态,有可能是高电平,也有可能是低电平。与数据无关,与电路有关。且在亚稳态状态时,会出现毛刺,震荡或者输出中间电平。

如例:

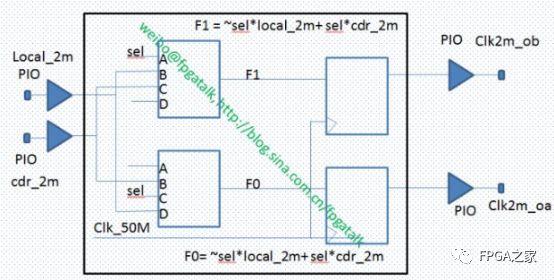

F1 <= local_2m输入,F0 <= local_2m输入,local_2m和cdr_2m都是2MHz的方波信号,被一个50MHz的异步时钟作同步化处理。Verilog代码为:

always @(posedge clk_50m)

if(sel==1)begin

clk2m_oa <= cdr_2m ;

clk2m_ob <= cdr_2m ;

end

else begin

clk2m_oa <= local_2m ;

clk2m_ob <= local_2m ;

end

分析出现亚稳态的原因:首先,2MHZ被50MHZ处理,一定会出现亚稳态,在震荡期间出现高电平,然后为低电平。这个毛刺产生的原因是因为门电路的原因。

③:亚稳态返回到哪一个稳定态是不可预测的,而且和输入数据无关。

1.2亚稳态的危害:

目前FPGA都是基于同步设计的思想,一个良好的子模块设计都是基于同一时钟下设计的。当不同时钟域进行通信时,就可能产生亚稳态。(如异步FIFO)

①:理论上如果亚稳态一个周期内不能正确恢复成稳定状态,则目的寄存器也会发生亚稳态,这就是亚稳态的传播。

②:亚稳态的毛刺直接输出可能会导致系统错误,如送错中断。

③:采样到错误的电平,导致功能错误。在状态机内,如果状态机的正常功能状态为 2.4.6.8,由于产生产生亚稳态导致状态机进入1.3.5.7的状态,会使状态机挂死在非法状态。

④:在异步读取RAM时,读写时钟不一致,如果出现亚稳态,会导致数据读错,(或者漏读,或者漏写)。

1.3亚稳态的处理:

一般来说,只要是异步信号同步化,都会产生亚稳态,只要等待一定的时间,都能恢复成稳定状态,等待的时间取决于MTBF和期间本身。

MTBF (平均无故障时间)与可靠性如果一个设计中包含同步组件,无论是否愿意它都会出现亚稳态。亚稳态无法彻底消除,因此我们所做的就是计算错误概率以及在时间上来描述它。让我们来看一下,假设这里有一个物理系统亚稳态错误发生的概率为 1/1000。换句话说,每一千次采样就会因为亚稳态发生一次错误。这也意味着,每一千次,输出就会在下一个时钟沿到来时,无法变化。如果时钟频率为 1KHz,那么每秒都会有一次错误出现,MTBF 值就为 1 秒。当然,这个假设过于简单;MTBF 是一种故障概率的统计度量,并且需要更为复杂、经验化、实验化的数据来计算。对于触发器来说,这种关系依赖于电路自身的物理常数和时钟频率,记住亚稳态本身与时钟没有任何关系,但是它和 MTBF 相关。自然的,我们会说一个可靠性好的电路具有很高的 MTBF 值。

①:经典的处理方法为多拍

异步信号经过第一个寄存器,如果发生了亚稳态,2nS(假设MTBF=1000Y)左右返回到稳定态,如果时钟周期大于2ns(时钟频率小于500MHz), 那么显然第二个寄存器就没有亚稳态发生了。此时亚稳态的唯一影响就是不能在最准确的时刻识别到异步信号,有可能早一拍,或者晚一拍识别。

多说一点,为了处理亚稳态,识别异步信号需要的时间就较长(2拍或者更多),这就是目前流行的同步设计的代价。

②: 降低亚稳态带来的危害。

一个良好的设计必须有好的容错能力,让设计对亚稳态不敏感。如果亚稳态出现,至少要有能力恢复。

1.状态机如果有异步信号输入,一定要多拍处理异步信号,并且使用安全状态机,任何情况下不可以让状态机挂死在非法状态。

2.异步接口不可能做到准确地定时,在预算精度时,必须容忍+/-1拍的延时。

3.异步FIFO两个时钟域的地址交互时,使用格雷码计数器并多拍处理, 可减低对亚稳态的敏感.

4.能用低的频率实现的功能,不要用高的频率。频域较高时,要用三拍或者更多的触发器来降低亚稳态的危害。

5.较陡的信号边沿(包括数据和时钟)有利于降低发生亚稳态的概率。

本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。