一般网卡驱动程序厂商会给我们提供一份模板驱动,我们的工作就是需要根据自己的需要更改这个模板驱动

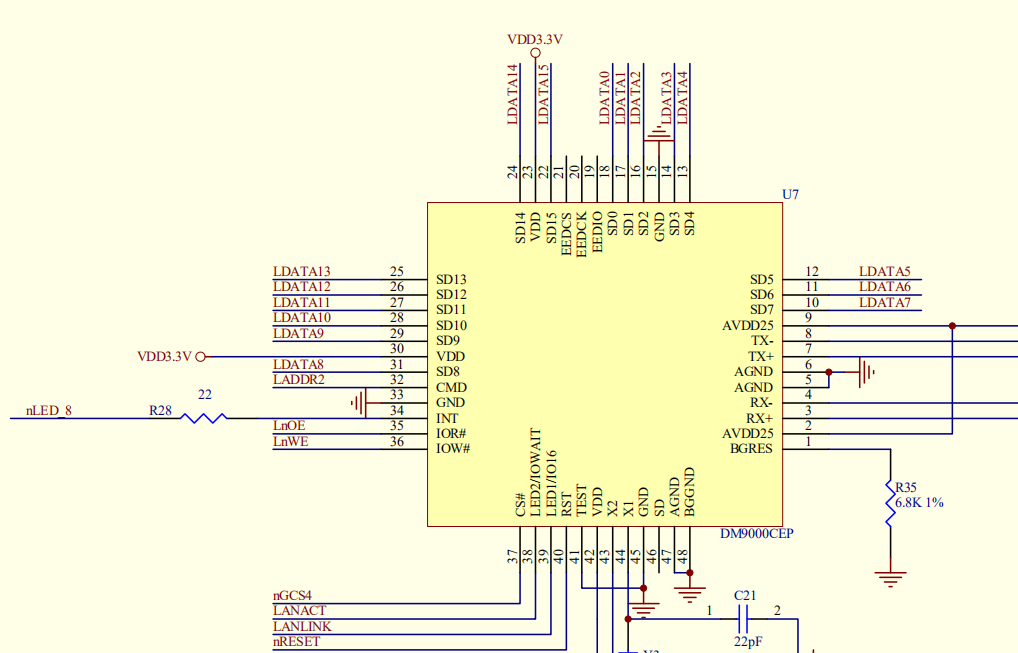

1、DM9000C的硬件连接

硬件连接图如下所示:它接在S3C2440的BANK4内存控制器上,它只占用8个字节的长度,并且是16bit的位宽。

下面介绍一下DM9000C的主要引脚的功能:SD0-SD15位16bit的数据引脚接口;IOR为读使能信号,低电平有效;IOW为写使能信号,低电平有效;CS为片选信号,低电平有效;CMD为数据与索引选择信号,高电平表数据,低电平表索引,它连接到S3C2440的LADDR2地址引脚;INT表示中断引脚数据发送成功或接收到数据可以产生中断,高电平有效,所以对于S3C2440来说需要设置上升沿触发来触发中断。

2、DM9000C的驱动代码编写

直接贴上修改好的代码:此代码是在厂家提供的驱动源码基础上依照S3C2440的应用修改的。

1 /*

2

3 dm9ks.c: Version 2.08 2007/02/12

4

5 A Davicom DM9000/DM9010 ISA NIC fast Ethernet driver for Linux.

6

7 This program is free software; you can redistribute it and/or

8 modify it under the terms of the GNU General Public License

9 as published by the Free Software Foundation; either version 2

10 of the License, or (at your option) any later version.

11

12 This program is distributed in the hope that it will be useful,

13 but WITHOUT ANY WARRANTY; without even the implied warranty of

14 MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

15 GNU General Public License for more details.

16

17

18 (C)Copyright 1997-2007 DAVICOM Semiconductor,Inc. All Rights Reserved.

19

20 V2.00 Spenser - 01/10/2005

21 - Modification for PXA270 MAINSTONE.

22 - Modified dmfe_tx_done().

23 - Add dmfe_timeout().

24 V2.01 10/07/2005 -Modified dmfe_timer()

25 -Dected network speed 10/100M

26 V2.02 10/12/2005 -Use link change to chage db->Speed

27 -dmfe_open() wait for Link OK

28 V2.03 11/22/2005 -Power-off and Power-on PHY in dmfe_init_dm9000()

29 -support IOL

30 V2.04 12/13/2005 -delay 1.6s between power-on and power-off in

31 dmfe_init_dm9000()

32 -set LED mode 1 in dmfe_init_dm9000()

33 -add data bus driving capability in dmfe_init_dm9000()

34 (optional)

35 10/3/2006 -Add DM8606 read/write function by MDC and MDIO

36 V2.06 01/03/2007 -CONT_RX_PKT_CNT=0xFFFF

37 -modify dmfe_tx_done function

38 -check RX FIFO pointer

39 -if using physical address, re-define I/O function

40 -add db->cont_rx_pkt_cnt=0 at the front of dmfe_packet_receive()

41 V2.08 02/12/2007 -module parameter macro

42 2.4 MODULE_PARM

43 2.6 module_param

44 -remove #include

45 -fix dmfe_interrupt for kernel 2.6.20

46 V2.09 05/24/2007 -support ethtool and mii-tool

47 05/30/2007 -fix the driver bug when ifconfig eth0 (-)promisc and (-)allmulti.

48 06/05/2007 -fix dm9000b issue(ex. 10M TX idle=65mA, 10M harmonic)

49 -add flow control function (option)

50 10/01/2007 -Add #include

51 -Modyfy dmfe_do_ioctl for kernel 2.6.7

52 11/23/2007 -Add TDBUG to check TX FIFO pointer shift

53 - Remove check_rx_ready()

54 - Add #define CHECKSUM to modify CHECKSUM function

55 12/20/2007 -Modify TX timeout routine(+)check TCR&0x01

56

57 */

58

59 //#define CHECKSUM

60 //#define TDBUG /* check TX FIFO pointer */

61 //#define RDBUG /* check RX FIFO pointer */

62 //#define DM8606

63

64 #define DRV_NAME 'dm9KS'

65 #define DRV_VERSION '2.09'

66 #define DRV_RELDATE '2007-11-22'

67

68 #ifdef MODVERSIONS

69 #include

70 #endif

71

72 //#include

73 #include

74 #include

75 #include

76 #include

77 #include

78 #include

79 #include

80 #include

81 #include

82 #include

83 #include

84 #include

85 #include

86 #include

87

88 #ifdef CONFIG_ARCH_MAINSTONE

89 #include

90 #include

91 #include

92 #endif

93

94 #include

95 #include

96 #include

97 #include

98

99

100 /* Board/System/Debug information/definition ---------------- */

101

102 #define DM9KS_ID 0x90000A46

103 #define DM9010_ID 0x90100A46

104 /*-------register name-----------------------*/

105 #define DM9KS_NCR 0x00 /* Network control Reg.*/

106 #define DM9KS_NSR 0x01 /* Network Status Reg.*/

107 #define DM9KS_TCR 0x02 /* TX control Reg.*/

108 #define DM9KS_RXCR 0x05 /* RX control Reg.*/

109 #define DM9KS_BPTR 0x08

110 #define DM9KS_FCTR 0x09

111 #define DM9KS_FCR 0x0a

112 #define DM9KS_EPCR 0x0b

113 #define DM9KS_EPAR 0x0c

114 #define DM9KS_EPDRL 0x0d

115 #define DM9KS_EPDRH 0x0e

116 #define DM9KS_GPR 0x1f /* General purpose register */

117 #define DM9KS_CHIPR 0x2c

118 #define DM9KS_TCR2 0x2d

119 #define DM9KS_SMCR 0x2f /* Special Mode Control Reg.*/

120 #define DM9KS_ETXCSR 0x30 /* Early Transmit control/status Reg.*/

121 #define DM9KS_TCCR 0x31 /* Checksum cntrol Reg. */

122 #define DM9KS_RCSR 0x32 /* Receive Checksum status Reg.*/

123 #define DM9KS_BUSCR 0x38

124 #define DM9KS_MRCMDX 0xf0

125 #define DM9KS_MRCMD 0xf2

126 #define DM9KS_MDRAL 0xf4

127 #define DM9KS_MDRAH 0xf5

128 #define DM9KS_MWCMD 0xf8

129 #define DM9KS_MDWAL 0xfa

130 #define DM9KS_MDWAH 0xfb

131 #define DM9KS_TXPLL 0xfc

132 #define DM9KS_TXPLH 0xfd

133 #define DM9KS_ISR 0xfe

134 #define DM9KS_IMR 0xff

135 /*---------------------------------------------*/

136 #define DM9KS_REG05 0x30 /* SKIP_CRC/SKIP_LONG */

137 #define DM9KS_REGFF 0xA3 /* IMR */

138 #define DM9KS_DISINTR 0x80

139

140 #define DM9KS_PHY 0x40 /* PHY address 0x01 */

141 #define DM9KS_PKT_RDY 0x01 /* Packet ready to receive */

142

143 /* Added for PXA of MAINSTONE */

144 #ifdef CONFIG_ARCH_MAINSTONE

145 #include

146 #define DM9KS_MIN_IO (MST_ETH_PHYS + 0x300)

147 #define DM9KS_MAX_IO (MST_ETH_PHYS + 0x370)

148 #define DM9K_IRQ MAINSTONE_IRQ(3)

149 #else

150 #define DM9KS_MIN_IO 0x300

151 #define DM9KS_MAX_IO 0x370

152 #define DM9KS_IRQ 3

153 #endif

154

155 #define DM9KS_VID_L 0x28