2.1 介绍

2.1.1 硬件

在对时钟频率进行初始化之后,就可以使用存储器控制器对 SDRAM 进行初始化了。

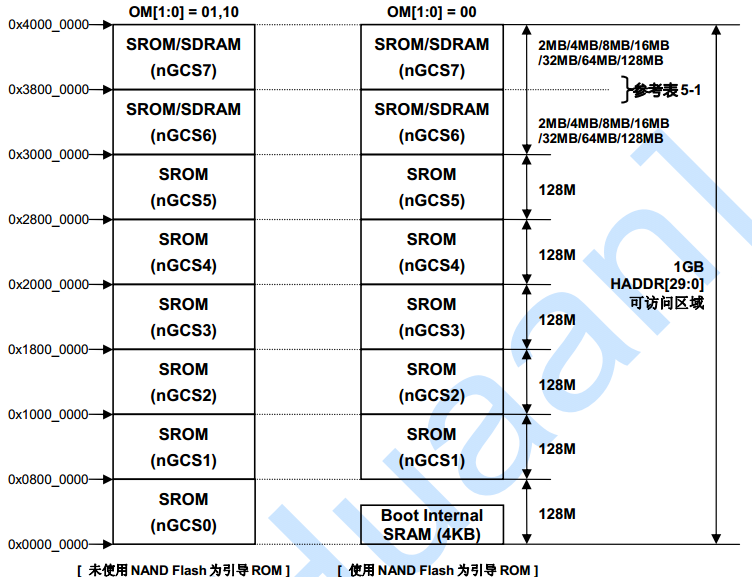

可以看看存储器控制器的映射表:

由图上可以看出,S3C2440 可以接两个 SDRAM,一个起始地址是 0x30000000,一个是 0x38000000,分别由片选信号 nGCS6 和 nGCS7 控制。

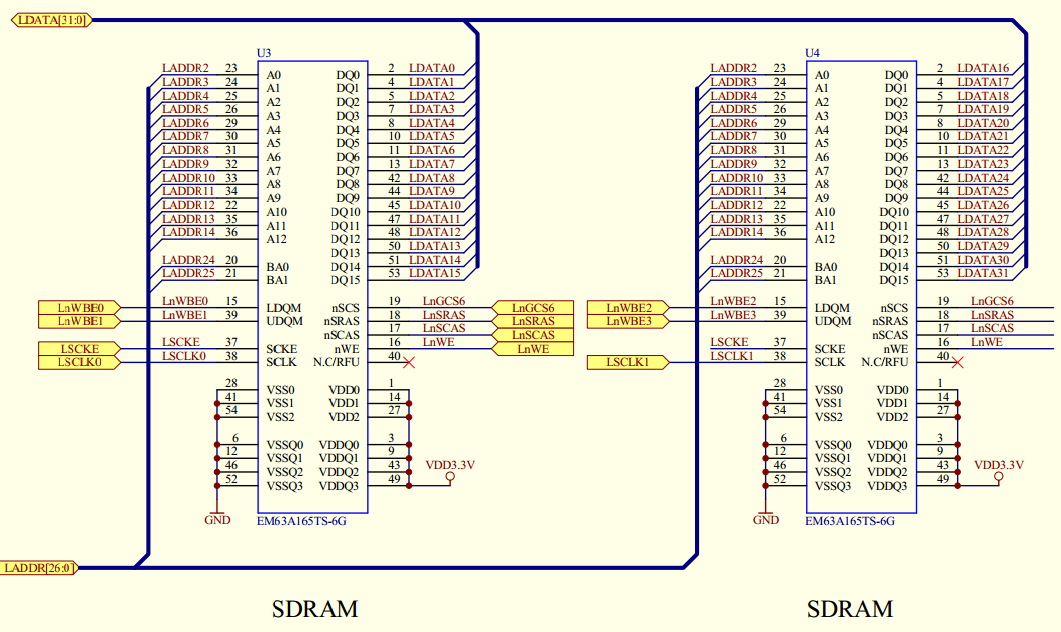

查看原理图上的 SDRAM 控制电路:

使用的是 nGCS6,那么 SDRAM 的地址就是 0x30000000

2.1.2 寄存器

存储器控制器涉及到的寄存器很多,具体看芯片手册。

2.2 代码编写

start.S 代码中:

1 /** 5. 初始化 SDRAM */

2 mov ip, lr /** 保存当前程序地址到 ip 寄存器 */

3 bl sdram_init /** 执行 SDRAM 的初始化 */

4 mov lr, ip

跳转到 sdram_init 标签中执行

sdram_init.S,这里是使用的 uboot 中的源码。

1 /** =============== BWSCON: 地址 0x48000000 总线宽度和等待控制寄存器 ================ */

2 #define BWSCON 0x48000000

3

4 /* DW:数据总线宽度数据定义 */

5 #define DW8 (0x0) /** 8 位数据总线宽度 */

6 #define DW16 (0x1) /** 16 位数据总线宽度 */

7 #define DW32 (0x2) /** 32 位数据总线宽度 */

8

9 /* WS: wait 状态 */

10 #define WAIT (0x1<<2) /** 开启 BANK 的 WAIT 功能 */

11

12 /* ST: 是否使用 使用 UB/LB */

13 #define UBLB (0x1<<3) /** BANK 使用 UB/LB */

14

15 #define B1_BWSCON (DW32) /** BANK1 的总线位宽设置 32 位 */

16 #define B2_BWSCON (DW16) /** BANK2 的总线位宽设置 16 位 */

17 #define B3_BWSCON (DW16 + WAIT + UBLB) /** BANK3 的总线位宽设置 16 位,使能 WAIT 和 UB/LB */

18 #define B4_BWSCON (DW16) /** BANK4 的总线位宽设置 16 位 */

19 #define B5_BWSCON (DW16) /** BANK5 的总线位宽设置 16 位 */

20 #define B6_BWSCON (DW32) /** BANK6 的总线位宽设置 32 位 */

21 #define B7_BWSCON (DW32) /** BANK7 的总线位宽设置 32 位 */

22

23 /** =================================== end BWSCON =============================== */

24

25 /** =============== BANK0CON: 地址 0x48000004 BANK0 控制寄存器 ===================== */

26 #define B0_Tacs 0x0 /* 0clk */

27 #define B0_Tcos 0x0 /* 0clk */

28 #define B0_Tacc 0x7 /* 14clk */

29 #define B0_Tcoh 0x0 /* 0clk */

30 #define B0_Tah 0x0 /* 0clk */

31 #define B0_Tacp 0x0

32 #define B0_PMC 0x0 /* normal */

33 /** =================================== end BANK0CON =============================== */

34

35 /** =============== BANK1CON: 地址 0x48000008 BANK1 控制寄存器 ===================== */

36 #define B1_Tacs 0x0 /* 0clk */

37 #define B1_Tcos 0x0 /* 0clk */

38 #define B1_Tacc 0x7 /* 14clk */

39 #define B1_Tcoh 0x0 /* 0clk */

40 #define B1_Tah 0x0 /* 0clk */

41 #define B1_Tacp 0x0

42 #define B1_PMC 0x0

43 /** =================================== end BANK1CON =============================== */

44

45 /** =============== BANK2CON: 地址 0x4800000C BANK2 控制寄存器 ===================== */

46 #define B2_Tacs 0x0

47 #define B2_Tcos 0x0

48 #define B2_Tacc 0x7

49 #define B2_Tcoh 0x0

50 #define B2_Tah 0x0

51 #define B2_Tacp 0x0

52 #define B2_PMC 0x0

53 /** =================================== end BANK2CON =============================== */

54

55 /** =============== BANK3CON: 地址 0x48000010 BANK3 控制寄存器 ===================== */

56 #define B3_Tacs 0x0 /* 0clk */

57 #define B3_Tcos 0x3 /* 4clk */

58 #define B3_Tacc 0x7 /* 14clk */

59 #define B3_Tcoh 0x1 /* 1clk */

60 #define B3_Tah 0x0 /* 0clk */

61 #define B3_Tacp 0x3 /* 6clk */

62 #define B3_PMC 0x0 /* normal */

63 /** =================================== end BANK3CON =============================== */

64

65 /** =============== BANK4CON: 地址 0x48000014 BANK4 控制寄存器 ===================== */

66 #define B4_Tacs 0x0 /* 0clk */

67 #define B4_Tcos 0x0 /* 0clk */

68 #define B4_Tacc 0x7 /* 14clk */

69 #define B4_Tcoh 0x0 /* 0clk */

70 #define B4_Tah 0x0 /* 0clk */

71 #define B4_Tacp 0x0

72 #define B4_PMC 0x0 /* normal */

73 /** =================================== end BANK4CON =============================== */

74

75 /** =============== BANK5CON: 地址 0x48000018 BANK5 控制寄存器 ===================== */

76 #define B5_Tacs 0x0 /* 0clk */

77 #define B5_Tcos 0x0 /* 0clk */

78 #define B5_Tacc 0x7 /* 14clk */

79 #define B5_Tcoh 0x0 /* 0clk */

80 #define B5_Tah 0x0 /* 0clk */

81 #define B5_Tacp 0x0

82 #define B5_PMC 0x0 /* normal */

83 /** =================================== end BANK5CON =============================== */

84

85 /** =============== BANK6CON: 地址 0x4800001C BANK6 控制寄存器 ===================== */

86 #define B6_MT 0x3 /* 配置BANK6的存器类型为 SDRAM */

87 #define B6_Trcd 0x1

88 #define B6_SCAN 0x1 /* 9bit */

89 /** =================================== end BANK6CON =============================== */

90

91 /** =============== BANK7CON: 地址 0x48000020 BANK7 控制寄存器 ===================== */

92 #define B7_MT 0x3 /* SDRAM */

93 #define B7_Trcd 0x1 /* RAS 到 CAS 的延迟为 3 个时钟 */

94 #define B7_SCAN 0x1 /* 列地址数为 9bit */

95 /** =================================== end BANK7CON =============================== */

96

97 /** =============== REFRESH: 地址 0x48000024 BANK7 SDRAM 刷新控制寄存器 ===================== */

98 #define REFEN 0x1 /* SDRAM 刷新使能 */

99 #define TREFMD 0x0 /* SDRAM 刷新模式为 CBR/自动刷新*/

100 #define Trp 0x0 /* SDRAM RAS 预充电时间 2 个时钟 */

101 #define Trc 0x3 /* SDRAM 半行周期时间 7 个时钟 */

102 #define Tchr 0x2 /* 3clk */

103 #define REFCNT 1113 /* SDRAM 刷新计数值, period=15.6us, HCLK=60Mhz, (2048+1-15.6*60) */

104 /** ======================================== end REFRESH ================================== */

105

106 .globl sdram_init

107 sdram_init:

108 /* memory control configuration */

109 /* make r0 relative the current location so that it */

110 /* reads SMRDATA out of FLASH rather than memory ! */

111 ldr r0, =SMRDATA /** 执行 SMRDATA 函数,对各个寄存器进行配置 */

112 ldr r1, =CONFIG_SYS_TEXT_BASE /** CONFIG_SYS_TEXT_BASE 为 0 */

113 sub r0, r0, r1

114 ldr r1, =BWSCON /* Bus Width Status Controller */

115 add r2, r0, #13*4 /* 将SMRDATA这一块地址赋值给r2中 */

116 0: /** 循环操作 */

117 ldr r3, [r0], #4

118 str r3, [r1], #4

119 cmp r2, r0

120 bne 0b /** 比较R2和R1,如果不相等,则跳回前面的 0 标号 */