大模型为AI注入新的活力之时,边缘AI的需求也随之增加,几大处理器IP厂商,都在扩展基于边缘的AI NPU,以卸载CPU的负载从而提升效率降低功耗。

日前,Ceva公司宣布推出Ceva-NeuPro-Nano NPU,扩展其Ceva-NeuPro Edge AI NPU产品系列。

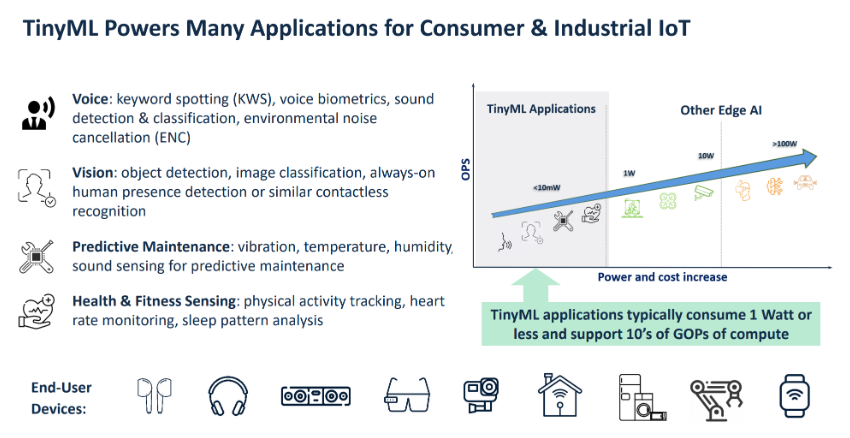

TinyML(Tiny Machine Learning)是一种在资源受限的微控制器和边缘设备上运行机器学习模型的技术。TinyML的目标是在低功耗、低内存和低计算资源的设备上实现高效的机器学习算法,以支持实时数据处理和决策。

物联网设备对高效、专业的人工智能解决方案的需求日益增加,推动了TinyML市场快速增长。根据研究机构ABI Research预测,到 2030 年,超过40% 的TinyML出货量将采用专用 TinyML 硬件,而非由通用MCU驱动。

TinyML需要什么?

TinyML具有如下四大特点:

·超低功耗:适用于电池供电或能量采集的设备,功耗通常在毫瓦级别。

·小内存占用:通常运行在只有几KB到几百KB RAM和Flash的微控制器上。

·实时处理:支持实时数据处理和响应,适用于物联网(IoT)设备。

·嵌入式应用:广泛应用于智能家居、可穿戴设备、工业物联网等领域。

以上四大特点同时也是TinyML的挑战,包括资源受限、功耗管理、实时性要求以及模型精度。

为了将AI放到边缘MCU中执行,需要更高效的算法设计,并对模型进行压缩和量化。

比如,设计适合嵌入式系统的轻量级算法,如小型卷积神经网络(CNN)、递归神经网络(RNN)等。并使用简单的激活函数和高效的算术运算,减少计算开销。

而对于模型压缩和量化,可采用多种方案,包括模型剪枝:移除模型中不重要的参数,减少计算和存储需求;权重共享:通过权重共享减少模型参数数量;量化:将浮点数转换为定点数,如8位或16位整数,降低内存和计算需求。

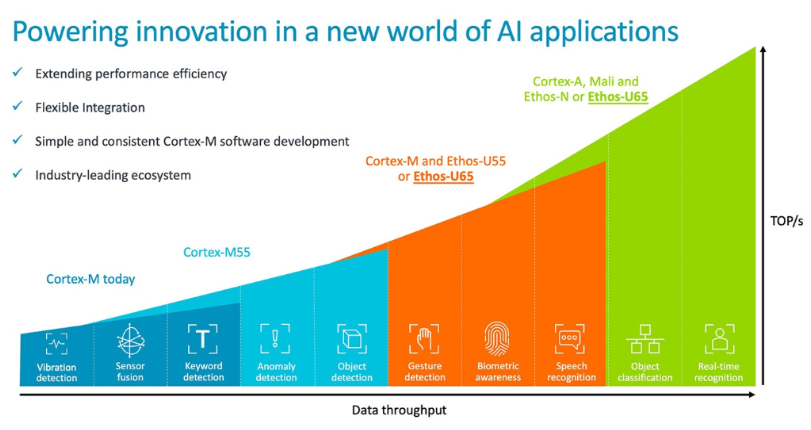

目前,TinyML的处理方式有几种,一个是MCU利用低功耗计算单元进行加速,如Arm的Cortex-M,另外,则是通过专用的硬件加速器卸载CPU的负载,几家主要的IP供应商都推出了专用的TinyML加速器IP,同时也有一些MCU厂商也自行开发了NPU/DSP或者其他类似的加速器。

典型的开发流程包括前期的数据收集与预处理,然后在高性能的计算系统中训练和优化模型,再使用模型压缩和量化技术,将最终修剪后的模型转换为嵌入式处理器可用的格式,再进行部署。

目前主流的TinyML IP供应商

实际上,几家主要的CPU IP供应商都提供NPU IP,包括Arm、Cadence、Synopsys、Verisilicon、Ceva等,有些适用于MCU,有些则适用于SoC中,根据处理性能、功耗、面积、成本等进行约束。

Arm的Ethos

Arm Ethos-U65是一款先进的微型神经处理单元(microNPU),专为嵌入式设备中的AI解决方案而设计。它继承了Ethos-U55的高能效,并在性能上提升了两倍,适用于Arm Cortex-A、Cortex-R和Neoverse系统。

Ethos-U65的主要特点包括:

卓越的性能和能效:在16nm工艺下达到1 TOP/s,同时在最小面积内实现2倍性能提升。

灵活集成:支持丰富的操作系统和DRAM,并适用于Cortex-M上的BareMetal或RTOS系统。

支持复杂AI模型:处理复杂的工作负载,特别是需要广泛AXI接口和DRAM支持的场景,性能提升达150%。

节能高效:相比之前的Cortex-M代,ML工作负载的能耗减少高达90%。

未来适应性强:支持卷积、LSTM、RNN等重计算操作符,以及自动在Cortex-M上运行其他内核。

离线优化:通过离线编译和优化神经网络,提高性能并减少系统内存需求,最多可减少90%。

Ethos-U65的多种功能使其能够满足各种高性能和低功耗嵌入式设备的需求,如智能相机、环境传感器、工业自动化和移动设备。它为开发、部署和调试AI应用提供了统一的工具链,是推动创新的强大助力。

Verisilicon

VeriSilicon的Vivante VIP9000处理器家族提供了适用于实时和低功耗AI设备的可编程、可扩展解决方案。其专利的神经网络引擎和张量处理结构在提供卓越推理性能的同时,具备业界领先的功耗和面积效率。VIP9000系列支持从0.5TOPS到20TOPS的性能范围,适用于从可穿戴设备、物联网、智能家居到汽车和边缘服务器等广泛应用。

VIP9000支持所有流行的深度学习框架,通过量化、剪枝和模型压缩等技术实现加速。其可编程引擎和张量处理结构支持多种数据类型和处理任务。通过ACUITY Tools SDK和各种运行时框架,AI应用可以轻松移植到VIP9000平台,实现高效开发和部署。

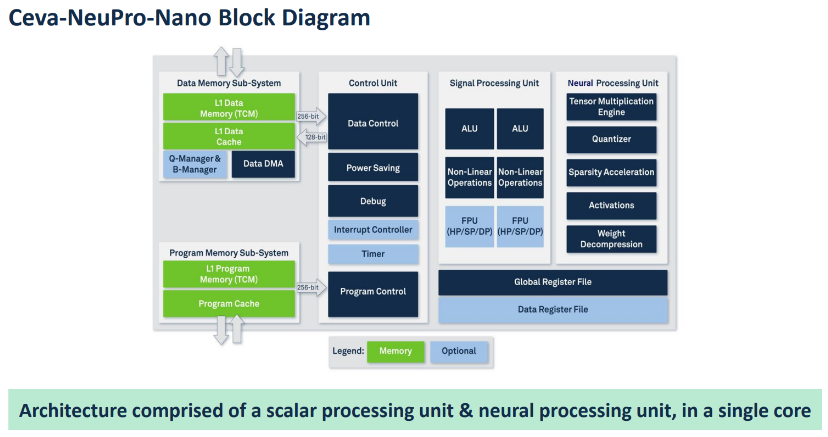

Ceva

Ceva-NeuPro-Nano 是一款高效自给式边缘 NPU,专为 TinyML 应用设计,适用于 AIoT 设备。其性能范围从 10 GOPS 到 200 GOPS,支持电池供电设备的常时开启应用,如可听设备、可穿戴设备、家庭音频、智能家居和智能工厂。无需主 CPU/DSP,即可独立运行,包括代码执行和内存管理。它支持 4、8、16 和 32 位数据类型,具有原生 Transformer 计算、稀疏性加速和快速量化功能。通过 Ceva-NetSqueeze 技术,内存占用减少 80%。提供 Ceva NeuPro-Studio AI SDK,与 TFLM 和 µTVM 等开源 AI 推理框架无缝协作,涵盖语音、视觉和传感用例。Ceva-NPN32 和 Ceva-NPN64 两种配置满足广泛的应用需求,提供最佳功耗效率和小巧硅面积。

Cadence

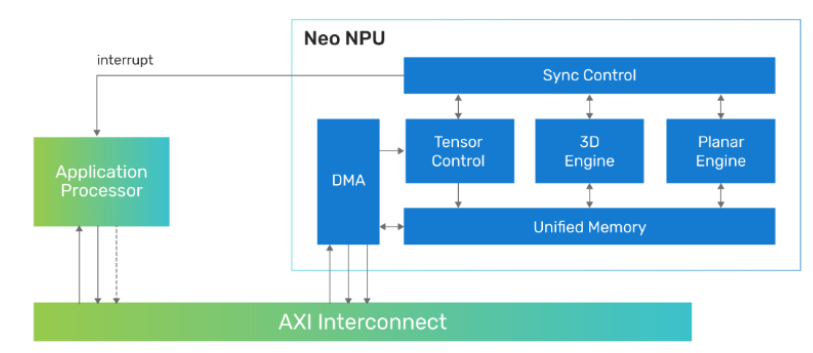

Cadence的Tensilica Neo NPU是高效能、低功耗的神经处理单元(NPU),专为嵌入式AI应用设计。它提供了从传感器、音频、语音/语音识别、视觉、雷达等多种应用的高性能AI处理能力。Neo NPU具备高度可扩展性,单核性能从256到32k 8x8-bit MAC每周期,最高可达80 TOPS,并可通过多核配置进一步提升性能,适应从超低功耗物联网设备到高性能AR/VR和汽车系统的需求。

Neo NPU支持Int4、Int8、Int16和FP16等数据类型,具备混合精度计算能力,优化了性能和精度的平衡。其架构支持各种神经网络拓扑,包括经典和生成式AI网络,能够卸载主处理器的负担。内置的压缩/解压缩功能有效减少系统内存占用和带宽消耗。

Neo NPU可在典型时钟频率下运行,达1.25GHz,在7nm工艺下提供卓越的计算性能。它集成了Cadence的NeuroWeave SDK,支持统一的软件开发环境,简化了模型部署和优化流程,提供高效、灵活的AI解决方案,满足多种嵌入式AI应用的需求。

Synopsys

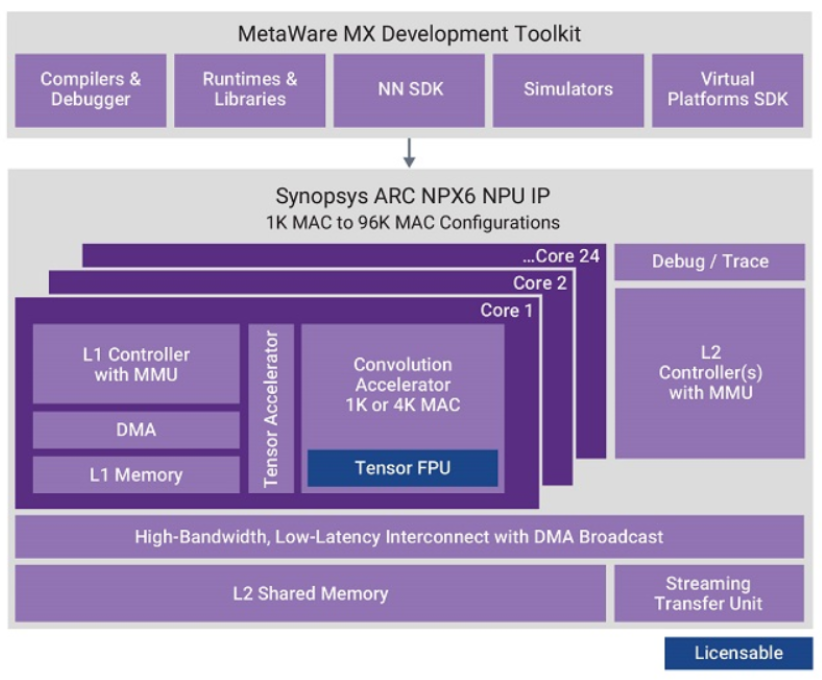

Synopsys ARC NPX6 NPU IP 系列是业内性能最高的神经处理单元(NPU)IP,专为满足AI应用的实时计算需求而设计,具备超低功耗。该系列包含ARC NPX6和NPX6FS,支持最新的复杂神经网络模型,包括生成式AI,并提供高达3,500 TOPS的性能,适用于智能SoC设计。

ARC NPX6 NPU IP单实例在5nm工艺下能提供高达250 TOPS的性能,通过稀疏特性可提升至440 TOPS。集成多个NPU实例后,性能可达3,500 TOPS。ARC NPX6支持从1K到96K MACs,兼容CNN、RNN/LSTM及新兴网络如Transformer。它支持INT 4/8/16位分辨率,并可选BF16和FP16。

ARC NPX6FS NPU IP专为功能安全设计,符合ISO 26262 ASIL D标准,适用于汽车和其他需要高安全性的应用。它具备双核锁步处理器和自检安全监控,满足混合关键性和虚拟化需求。

Synopsys提供的ARC MetaWare MX开发工具包包含编译器、调试器、神经网络软件开发工具包(SDK)、虚拟平台SDK、运行时和库以及高级仿真模型。该工具包能自动将算法划分到MAC资源上,实现高效处理,简化了开发流程。

ARC NPX6 NPU IP系列广泛应用于智能相机、传感器融合、工业自动化、汽车电子和高性能嵌入式系统等领域,助力实现智能SoC设计中的AI创新。

晶心科技

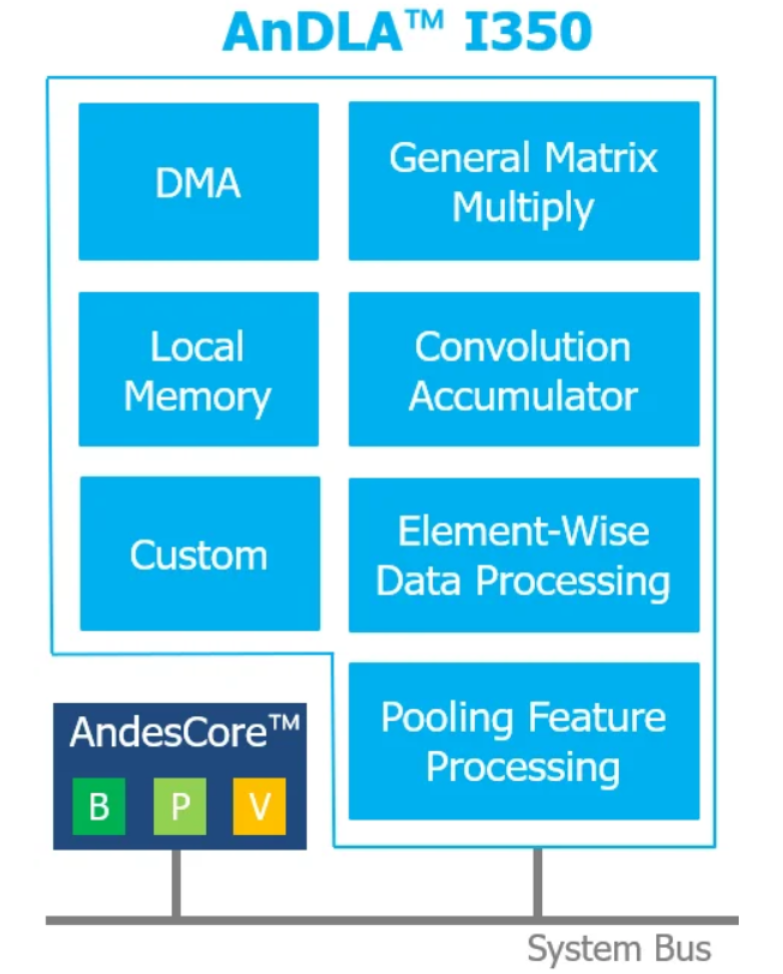

AndesAIRE AnDLA I350 是一款深度学习加速器,专为边缘和终端推理设计,提供高性能和高效能的AI解决方案。它支持TensorFlow Lite、PyTorch和ONNX等流行深度学习框架,并执行卷积、全连接、激活、池化等多种神经网络操作,使用int8数据类型。AnDLA I350 具备内部DMA和本地内存,采用操作融合技术提高效率。其可配置参数包括32至4096个MAC,16KB至4MB的SRAM大小,提供64 GOPS至8 TOPS的计算能力。适用于AIoT设备、智能相机、智能传感器、可穿戴设备、智能家电和机器人等应用领域,满足广泛的边缘AI需求。

其他选择

很多MCU公司也根据自身需求选择自行开发NPU,目前包括NXP、TI、英飞凌、ST、ADI等公司,都拥有自己的NPU。实际上,由于芯片厂商更加了解对应的终端需求,因此其CNN加速器无论是何形态,都可以适配其自身的应用。

考虑到各家对于TinyML的场景定义不同,随着SoC的功耗逐步下降以及对于边缘AI的算力需求增加,更多SoC也进入到这一场景中,同时借助CPU、GPU运行ML,也完全可以符合某些市场的需求。

软件开发生态

实际上,对于终端而言,最后PK的依然是生态系统,依然是开发门槛,以及性价比。所以我们看到IP供应商也都在强调其IP对于不同框架的兼容性,此外,MCU厂商也在积极布局软件的开发,从而实现差异化。

ST在2019年发布STM32Cube.AI工具,在2021年收购NanoEdge AI Studio,并推出了ST EDGE AI SUITE和Nano AI Studio;

NXP在2018年推出机器学习软件eIQ,并不断加大在AI/ML上的投入;

Microchip在2020年就将Cartesiam(现已被ST收购)、Edge Impulse和Motion Gestures的软件和解决方案接口引入其设计环境,并收购了Neuronix AI Labs;

Renesas在2022年完成对美国从事机器学习模型开发的初创企业Reality AI(以TinyML为业务)的收购;

TI将EDGE AI STUDIO更名为Model Analyzer;

Infineon收购瑞典的TinyML和AutoML领域初创公司Imagimob AB。

写在最后

随着各主流IP供应商陆续推出边缘TinyML IP,侧面印证了芯片客户对于这一技术的需求有多大。接下来MCU和SoC厂商也要对应有新的动向,尤其是未来ML需要有专门的加速器而非通用MCU所驱动时。

也正因此,目前MCU厂商的多角度尝试,正是为了探索出哪类加速器更加的适合。

总的说来,尽管边缘NPU市场竞争日益激烈,但需求依然会继续增长。

技术咨询

技术咨询 代买器件

代买器件 商务客服

商务客服 研发客服

研发客服