Microchip推出集成微型FPGA的PIC16 微控制器,售价不到 50 美分

编译自EEJOURNAL

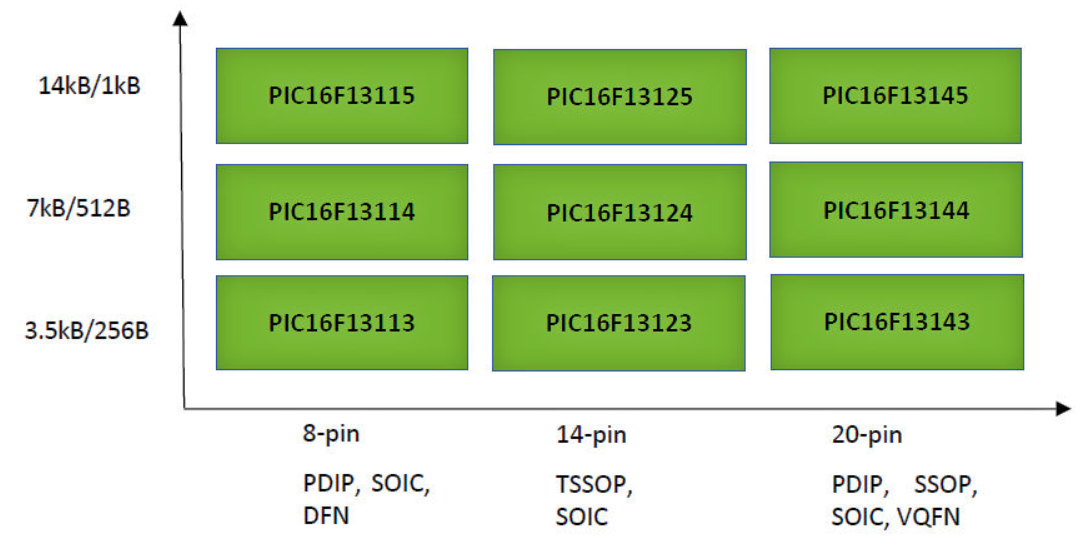

Microchip 现在提供一款基于闪存的微控制器,集成可编程逻辑块,其售价不到50美分。 Microchip PIC16F13145 系列的九个新产品,与其他型号16F系列采用相同的 8 位 RISC 微处理器架构,但它们还集成了一个新的可编程逻辑块,称为可配置逻辑块 (CLB)。 PIC16F13145 微控制器系列中的器件采用 8、14 和 20 引脚封装,具有 3.5 至 14 KB 闪存和 256 至 1024 字节 RAM。

Microchip PIC1613145 微控制器系列的九个成员具有相同的内部架构,但具有不同数量的 RAM 和闪存,并提供不同的封装,具体取决于您应用的 I/O 需求。 图片来源:Microchip

该系列中的器件具有相同类型和数量的外设,但外部 I/O 引脚数量有所不同,具体取决于封装。 十多年前,Microchip 在其微控制器中引入了一种称为可配置逻辑单元 (CLC) 的可编程逻辑外设。 与早期 Microchip PIC 和 AVR 微控制器中集成的 CLC 相比,PIC16F13145 系列中的CLB是一个更大、更复杂的可编程逻辑块,我们可能会在未来的 PIC16 产品中看到更大的CLB。为了向后兼容,PIC16F13145 微控制器还集成了四个 CLC。

在深入研究 PIC16F13145 器件的复杂内部结构之前,我认为解释如何使用 CLB 并提供一些示例使用非常重要,因为理解为何在8位低端微处理器内核上配备32-LUT的可编程逻辑块可能有些困难。当 PIC16F13145 微控制器的 CPU 对于执行任务而言速度太慢,或者当您需要某种形式的简单并行处理,超出微控制器的多任务处理能力时,CLB 可以方便地实现少量硬件级实时处理。

此类应用是我们开始使用 FPGA 的基础,Microchip 现在已将微型 FPGA(尽管比旧 CLC 更大)移植到其微控制器子系列之一中。 您可以使用 CLB 来实现状态机或“高速”外设,例如软件驱动的信号多路复用器、计数器、正交解码器、步进电机控制器或高速 PWM(脉宽调制器)。 CLB 可以在 CPU 处于睡眠模式时做出逻辑决策,从而降低系统的整体功耗。 CLB 的输出可以驱动外部设备引脚或微控制器其他外围设备的输入。

CLB 本身看起来非常像 FPGA 中的可编程逻辑结构。构成 CLB 的 32 个基本逻辑元件 (BLE) 与第一款 FPGA 中的逻辑单元非常相似——1985年赛灵思推出的Xilinx XC2064。每个 BLE 由一个 4 输入 LUT 和一个 D 触发器组成。 宽多路复用器为 16 个输入选择锁存器提供信号,然后使用从外部输入引脚、内部寄存器的位以及内部外设的输出引脚提取的 40 种不同输入信号之一来驱动 CLB 的 LUT 输入。 16 个输入选择锁存器的输出均馈入可编程边沿检测器。 这些边沿检测器默认由正边沿触发,但可以编程为由负边沿触发或完全旁路。 另外八个多路复用器将八个 CLB 输出位路由到外部引脚、内部寄存器或内部外围设备的输入。 例如,CLB 还包含一个 3 位硬件计数器,以帮助使用 CLB 构建状态机。

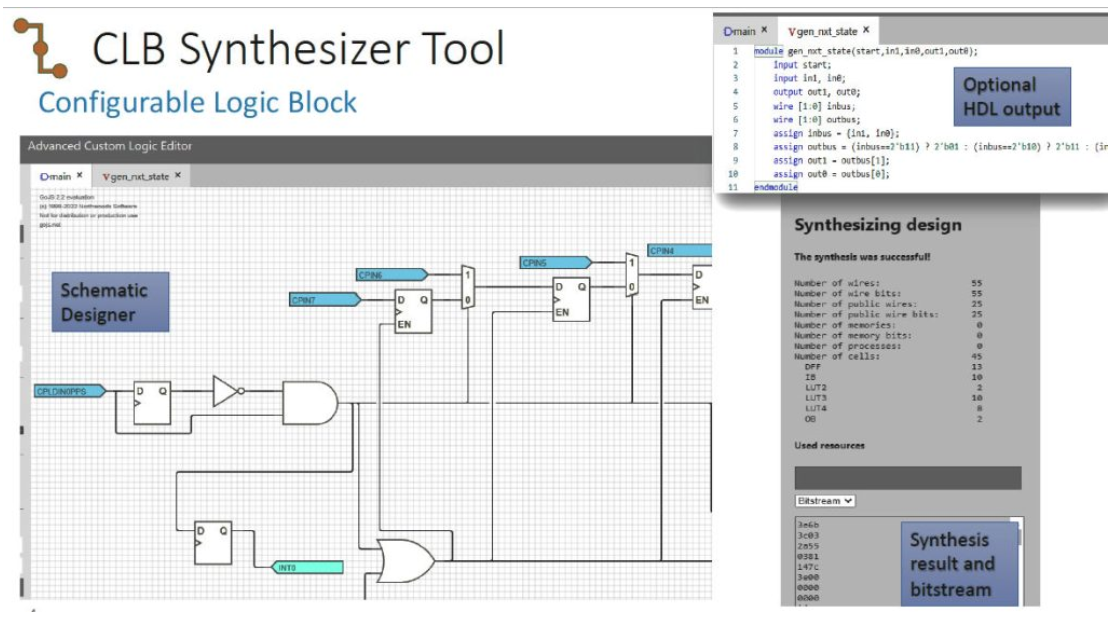

Microchip 的文档没有讨论 CLB 的内部接线、开关矩阵或其配置位,你不需要了解它们。 相反,MPLAB 代码配置器 (MCC) 是该公司 MPLAB X 集成开发环境 (IDE) 软件中的免费软件插件,可根据设计人员的原理图处理 CLB 配置详细信息。 您可以使用 MPLAB IDE 中集成的原理图编辑器为 PIC16F13145 的 CLB 创建设计。

所有 FPGA 设计最初都采用原理图捕获,直到 FPGA 变得太大且复杂,无法实现原理图。 20 世纪 90 年代初,随着 FPGA 变得越来越大,Verilog 或 VHDL 中的 HDL 编码开始取代原理图输入。我的好朋友 Robert Bielby 回忆道,到 2000 年代初,分层的、基于文本的 HDL 描述已经在很大程度上取代了 FPGA 设计的原理图输入,当时 FPGA 的最大容量已经达到了数千个 LUT。 (Bielby 在 Altera 和 Xilinx 工作了大约二十五年,很少有工程师能记得设计师何时使用原理图定义 FPGA。但是,Bielby 和我记得。)

Bielby 记得见过的最大的原理图设计需要 30 多张 D 尺寸的纸。 这对于原理图来说太大了。 Microchip 基于原理图的 CLB 设计方法让人回想起电子行业遥远的时代,但它仍然完全适合具有 32 个 LUT 的 FPGA。 PIC16F13145 微控制器的 32-LUT CLB 非常简单,只需原理图输入即可。

CLB 的原理图条目使用基本符号,例如 2、3 和 4 输入逻辑门、D 或 JK 触发器、2 或 4 输入多路复用器以及简单的整数常量。还可以直接使用 CLB 的 4 LUT,这是其基本逻辑元素。 一些微控制器的硬化外设也可以包含在设计中,以便 CLB 可以与那些片上外设进行交互。 CLB 还可以通过寄存器接口与微控制器的 CPU 交互,软件可访问的输入和输出寄存器在原理图上显示为位级输入和输出。

Microchip 用于 PIC16F13145 微控制器可编程逻辑的 CLB 合成器接受原理图级设计(左),并且还可以接受 HDL 代码(右上)。 图片来源:Microchip

在使用 MPLAB 代码配置器(MCC)综合设计之前,MPLAB 将原理图设计转换为 Verilog HDL 描述。 Microchip 使您可以通过块级容器将您自己的 Verilog 代码插入到 CLB 原理图中。 综合后,MPLAB 会将设计映射到 CLB,对设计进行布局和布线,并生成可与微控制器的已编译目标代码集成的配置比特流。CLB 配置作为常量序列存储在微控制器的闪存中,并在启动时通过 DMA 自动传输到 CLB。基于 RAM 的 CLB 是可重新配置的,因此可以在微控制器的闪存中存储多个 CLB 配置。微控制器可以在软件控制下重新配置 CLB,重新配置时间为 206 个指令周期,在微控制器最大 32MHz 时钟速率下略低于 26 微秒。

MCC 还提供基于 GUI 的方法来配置 PIC16F13145 微控制器子系列中的其他外设。 除了可编程逻辑 CLB 之外,PIC16F13145 微控制器还集成了许多其他外围设备。 所有 PIC16F13145 微控制器均包含四个较旧且较简单的可编程逻辑 CLC,以便与其他 Microchip 微控制器向后兼容。 此外,PIC16F13145 微控制器具有一长串内部外设,包括:

一个 10 位、100ksamples/sec ADC,带有 22 输入模拟多路复用器

1个8位DAC

两个模拟比较器

两个捕捉/比较/PWM 模块,具有用于定时和事件触发的 16 位分辨率和用于 PWM 的 10 位分辨率

两个10位PWM模块

1个可配置8/16位定时器、1个16位定时器和1个8位定时器

1个串口

1 个具有 SPI 和 I2C 模式的同步串行外设

1个外部中断引脚

供 ADC 内部使用的两个可选电压基准

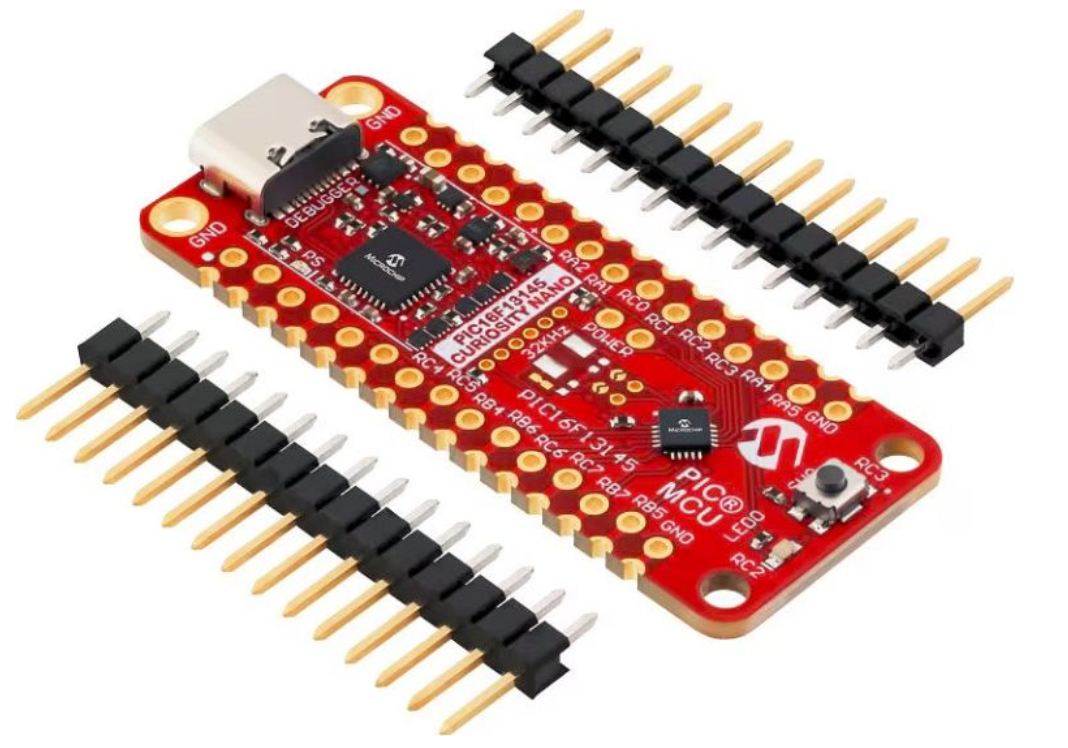

Microchip 为 PIC16F13145 微控制器开发了 Curiosity Nano 评估板。 它的尺寸约为 40 针 DIP,并配有可焊接的排针。该板通过 USB 电缆连接到主机系统,并可以自行对板载 PIC16F13145 微控制器的闪存进行编程。

低成本 Curiosity Nano PIC16F13145 评估板可让您探索微控制器的功能,并可通过评估板的 USB 端口对微控制器上的闪存进行编程。 图片来源:Microchip

Microchip PIC16F13145 微控制器最小器件的单价为 0.47 美元。PIC16F13145 微控制器系列中的 FPGA 结构只有32 个 LUT,大约是 1985 年推出的原始 Xilinx XC2064 FPGA 大小的一半。但如果 Microchip 决定生产售价为 2 美元的产品,应该要添加更多的LUT。

尽管这是一个非常不公平的比较,但您可以将 Microchip PIC16F13145 视为 AMD 和英特尔。 这些芯片包含多个 32 位或 64 位 Arm 处理器以及数千个 FPGA LUT。许多嵌入式设计并不需要那么多的处理能力,但它们通常需要比软件驱动的 8 位微控制器更高的性能时,这就是低成本 Microchip PIC16F13145 及其小型集成 FPGA 可以提供您所需的功能的地方。

本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。