-

逻辑使用量小

本文引用地址: 通用架构,可在 Xilinx 和 Altera 中轻松运行。也可以很容易地移植到ASIC。

RISC:

小指令集

多个累加器,多种数据大小

双寄存器文件

每条指令中的条件执行

数据存储器:使用(至少)一个模块

代码存储器:使用串行闪存或块

被设计为几乎是免费的,即在中占用很少的空间,并从串行闪存中执行。 许多新的板卡都已使用串行闪存来配置FPGA。 可以使用闪存中未使用的内存空间作为代码内存。

0

Spoc 可以参数化。

目前,第一个实现“Spoc0”不是。

Spoc0 具有以下固定特征:

4 种数据大小/累加器:1、8、16 和 32 位

2 个寄存器文件,每个寄存器 32 个寄存器,每个寄存器宽度为 16 位

64Kbits的数据寻址空间

64Kbits的代码寻址空间

至少使用 2 个块函数(一个用于数据空间,一个用于代码空间)

大约 300 行 Verilog

最大时钟速度在 90-110MHz 范围内(Spartan 3/Cyclone 2,最慢速度等级)

逻辑使用,约 175 个切片/300 个逻辑单元(Spartan 3/Cyclone 2)。

Spoc0 有多快?

当然,这取决于您的时钟速度以及您正在运行的指令类型...... 但即使在 100MHz 时,Spoc0 也可能比其他可用的 CPU 慢。

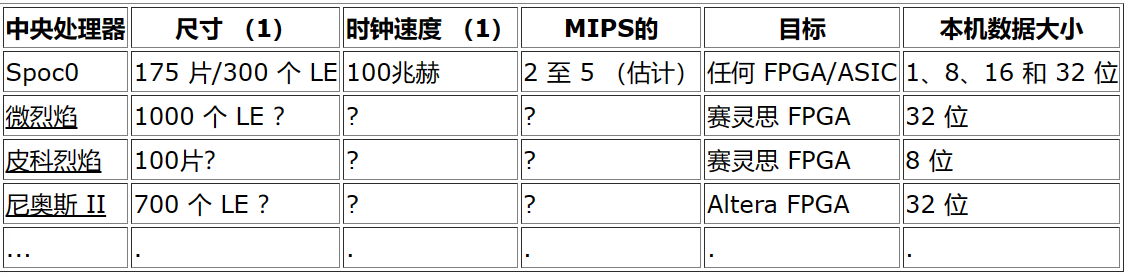

(1) Xilinx Spartan 3 或 Altera Cyclone 2,速度最慢等级

注意:所提供的表格不保证准确性或公平性(很难公平地比较不同的 CPU)

在设计 Spoc0 时,我们的目标不是获得尽可能快的 CPU,而是针对当今 FPGA(和 ASIC)的小型(低逻辑使用率)CPU。

在 CPU 世界中,速度和逻辑使用是成对的。 快速 CPU 使用固有的宽总线 - 这增加了它们的逻辑使用率。 Spoc0 采用相反的方法,将总线宽度与时钟周期进行权衡。 换句话说,Spoc0 序列化了它的许多任务(它每条指令使用更多的时钟周期),但仍然很纤薄。 将来,一些任务可以选择并行化 - 代价是更高的逻辑使用率。

上一篇:

下一篇: