10月13日,日本佳能公司宣布推出FPA-1200NZ2C纳米压印半导体制造设备,该设备将执行最重要的半导体制造工艺——电路图案转移。

据介绍,佳能的纳米压印光刻(Nano-Imprint Lithography,NIL)技术可实现最小线宽14nm的图案化,相当于生产目前最先进的逻辑半导体所需的5nm节点。此外,随着掩模技术的进一步改进,NIL有望实现最小线宽为10nm的电路图案,相当于2nm节点。

半导体制造领域,光刻机是昂贵且关键的设备,而纳米压印设备被多家日本半导体设备厂商视作替代光刻机的“下一代设备”,担负着以低成本制成尖端微细电路的使命。

铠侠、佳能和大日本印刷等公司是该技术路径的主要推动者,正合力研发,规划在2025年将该技术实用化。日经新闻网此前称,对比EUV光刻工艺,使用纳米压印光刻工艺制造芯片,能够降低将近四成制造成本和九成电量。

目前唯一可靠的制造5纳米及以下芯片的方法(EUV机器)因为贸易制裁禁止进入中国。而日本公司的技术则完全省略了光刻过程,而是直接将所需的电路图案压印到硅片上。由于其创新性,它不太可能被现有的贸易限制所禁止。

目前,佳能的发言人拒绝对新设备是否受到日本出口限制发表评论。

纳米压印究竟是什么黑科技?竟能代替复杂的光学光刻技术?

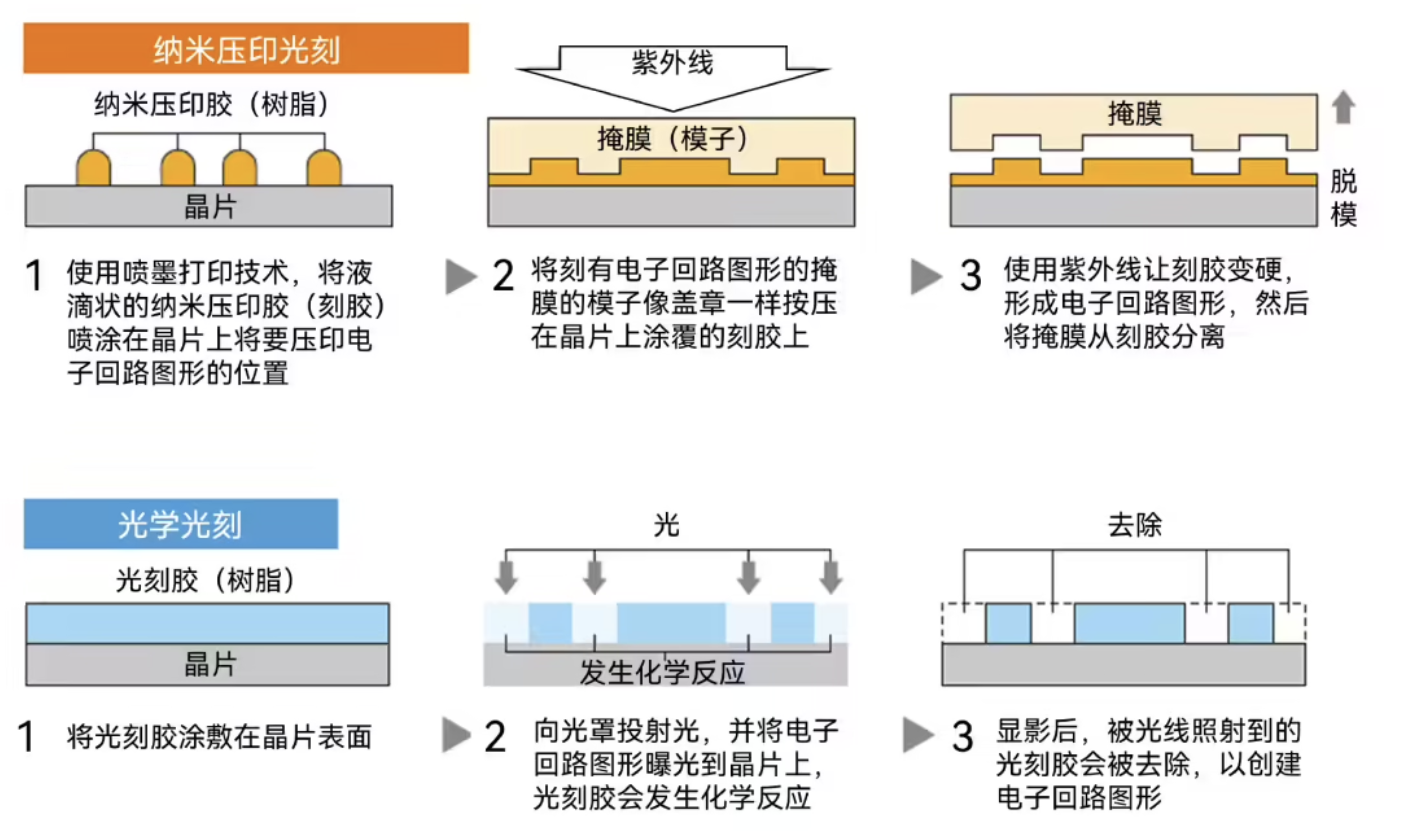

资料显示,纳米压印是一种微纳加工技术,它采用传统机械模具微复型原理。简单来说,传统的光刻设备通过将电路图案投影到涂有抗蚀剂的晶圆上来转移电路图案,而纳米压印光刻造芯片则通过将印有电路图案的掩模压印在晶圆上的抗蚀剂上,就像印章盖在橡皮泥上,然后经过脱模就能够得到一颗芯片。

纳米压印光刻(紫外纳米压印)与光学光刻对比

官方消息显示,佳能早在2004年开始秘密研发NIL技术,2014年美国分子压印公司(现佳能纳米技术)加入佳能集团,该研发消息才被公开。2021年春季,大日本印刷在根据设备的规格进行了内部模拟,发现在电路形成过程中每个晶片的功耗可以降低到使用EUV曝光时的大约1/10,根据大日本印刷的说法,NIL量产技术电路微缩程度则可达5nm节点。2017年7月,佳能纳米压印半导体制造设备“FPA-1200NZ2C”设备交付给东芝存储器四日市工厂。

从应用范围来看,纳米压印技术的适用场景非常广泛,包括集成电路、存储、光学、生命科学、能源、环保、国防等领域。

在佳能开发人员首藤真一看来,这种纳米压印设备是一种将创造未来的设备。未来,半导体会变得更精细,不仅会被封装在智能手机中,未来还会被用作贴纸,比如贴在人体皮肤上或隐形眼镜上。他相信只有纳米压印方式才能以客户要求的成本和速度实现这一点。

其中在芯片领域,纳米压印光刻不仅擅长制造各种集成电路,更擅长制造3D NAND、DRAM 等存储芯片,与微处理器等逻辑电路相比,存储制造商具有严格的成本限制,且对缺陷要求放宽,纳米压印光刻技术与之非常契合。

据DIGITIMES此前消息,SK海力士2023年引进佳能纳米压印设备,正在进行测试与研发,目标在2025年左右将该设备用于3D NAND量产。

国内已有多家上市公司积极布局该技术,这些公司集中在消费电子行业,近期在互动易平台回复纳米压印相关业务的上市公司包括美迪凯、利和兴、水晶光电、汇创达、歌尔股份、苏大维格等。