1. 实验目的

本文引用地址:(1)熟悉和掌握开发流程和软件使用方法;

(2)通过实验理解和掌握数码管驱动;

(3)学习用描述数码管驱动电路。

2. 实验任务

在数码管上显示数字。

3. 实验原理

数码管是工程设计中使用很广的一种显示输出器件。一个7段数码管(如果包括右下的小点可以认为是8段)分别由a、b、c、d、e、f、g位段和表示小数点的dp位段组成。实际是由8个LED灯组成的,控制每个LED的点亮或熄灭实现数字显示。通常数码管分为共阳极数码管和共阴极数码管,结构如下图所示:

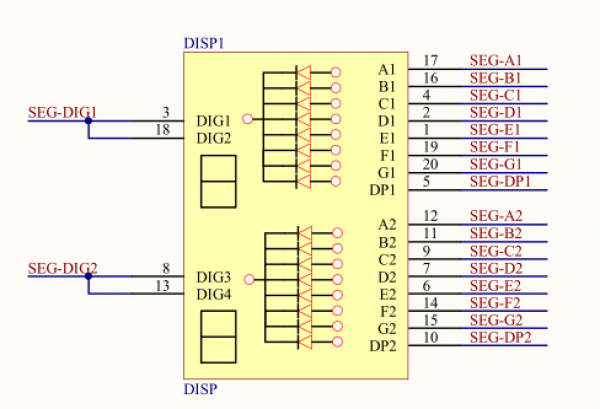

共阴8段数码管的信号端低电平有效,而共阳端接高电平有效。当共阳端接高电平时只要在各个位段上加上相应的低电平信号就可以使相应的位段发光。比如:要使a段发光,则在a段信号端加上低电平即可。共阴极的数码管则相反。 可以看到数码管的控制和LED的控制有相似之处,在小脚丫STEP-MXO2 V2开发板上有两位共阴极数码管:

数码管所有的信号都连接到的管脚,作为输出信号控制。只要输出这些信号就能够控制数码管的那一段LED亮或者灭。这样我们可以通过开关来控制FPGA的输出,和3. 3-8译码器实验一样,通过组合逻辑的输出来控制数码管显示数字,下面是数码管显示的表格

这其实是一个4-16译码器,如果我们想数码管能显示16进制可以全译码,如果只想显示数字,可以只利用其中10个译码

4. 用CircuitJS查看

5. 建模描述

数码管驱动清单segment.v

module segment

(

input wire [3:0] seg_data_1, //四位输入数据信号

input wire [3:0] seg_data_2, //四位输入数据信号

output wire [8:0] segment_led_1, //数码管1,MSB~LSB = SEG,DP,G,F,E,D,C,B,A

output wire [8:0] segment_led_2 //数码管2,MSB~LSB = SEG,DP,G,F,E,D,C,B,A

);

reg[8:0] seg [15:0]; //存储7段数码管译码数据

initial

begin

seg[0] = 9'h3f; // 0

seg[1] = 9'h06; // 1

seg[2] = 9'h5b; // 2

seg[3] = 9'h4f; // 3

seg[4] = 9'h66; // 4

seg[5] = 9'h6d; // 5

seg[6] = 9'h7d; // 6

seg[7] = 9'h07; // 7

seg[8] = 9'h7f; // 8

seg[9] = 9'h6f; // 9

seg[10]= 9'h77; // A

seg[11]= 9'h7C; // b

seg[12]= 9'h39; // C

seg[13]= 9'h5e; // d

seg[14]= 9'h79; // E

seg[15]= 9'h71; // F

end

assign segment_led_1 = seg[seg_data_1];

assign segment_led_2 = seg[seg_data_2];

endmodule

6. 实验步骤

1 登录小脚丫FPGA Web IDE系统,建立工程

2 新建设计文件,并键入设计代码

3 设定该代码位顶层文件

4 点击“逻辑综合”按钮,完成综合,代码无错误会显示完成

5 点击管脚分配,根据代码中端口的定义绑定相应的管脚

6 点击“FPGA映射”生成可以配置FPGA的JED代码

7 点击文件下载,并鼠标指向“下载JED文件”,鼠标右键保存到STEPFPGA盘中完成FPGA的编程

7. 显示效果