在上次的方案我有给大家介绍一款基于DSPG D7的4MIC降噪会议音响的方案,得到了很多客户的青睐,很多客户也立案做了很多项目,这里感谢各位的支持。这次我给大家介绍一个级联会议音响的项目,有兴趣的客户可以接着往下看。

由于目前的音箱大都以单个音箱为主,如果会议室较大,无法达到理想的效果。级联音箱可以通过有线和无线的方式实现级联。

为了达到声音播放与拾音同步的效果,利用DSPG现具备的一套适用于级联音响的Daisy Chain技术,微秒级的同步精度,达到了很好的语音播放,拾音同步的效果。基于此技术可以支持无线和有线的级联方式,为了考虑到时间精度我这里给大家讲解我们搭建的有线级联方案。

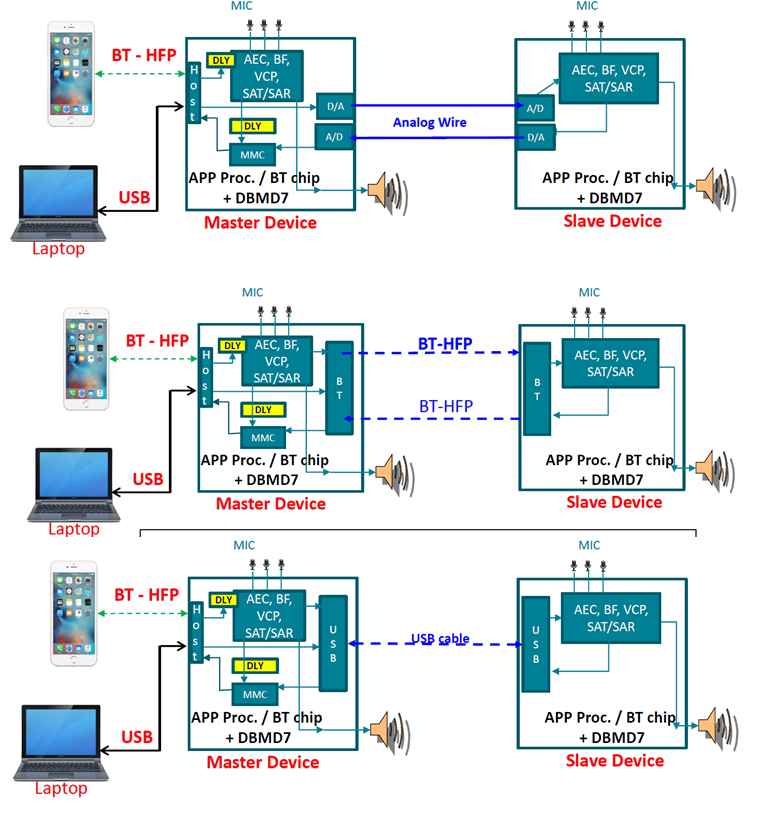

我这里给大家讲解一下Daisy Chain的概念。

.Daisy Chain 提高设备范围/房间覆盖率,可以适用于大型会议室。

.Daisy Chain 设备激活离通话者最近的MIC。

.Daisy Chain 设备共同工作将继续支持每个设备的功能集-良好的双通话性能,以及回声消除,波束形成和噪声消除。

.Daisy Chain设备离网络最近的设备是主设备,其他的是从设备。

.主设备通过USB或蓝牙连接到笔记本电脑/移动设备

.主从设备通过蓝牙、USB、DECT或3.5mm模拟电缆连接

.当设备使用蓝牙或USB连接时,设备之间的时钟漂移是预期的,由Rate Adaptation管理

.设备之间的互联应确保音频信号在Daisy Chain连接上的固定延时。

Daisy Chain 的技术支持模拟线连接、蓝牙连接、USB 数据线连接以及DECT连接的多种方式, 如方案方框图所示。基于我这个方法,我主要是讲解基于模拟线连接的方式,也就是通过4段的3.5mm的音频线来实现级联的效果。

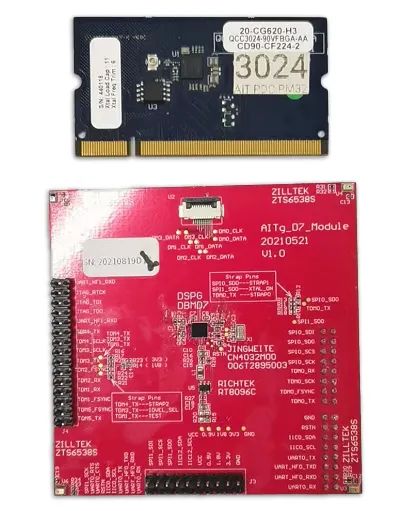

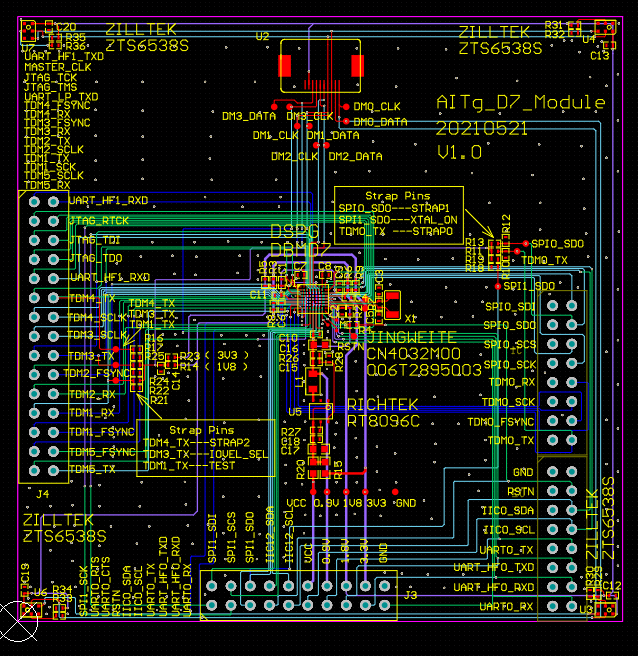

我们这里搭建的主控mcu是基于高通平台的QCC3024 蓝牙芯片,DSPG采用的是D7这颗IC,搭建用的是我们自己画的D7 evb。

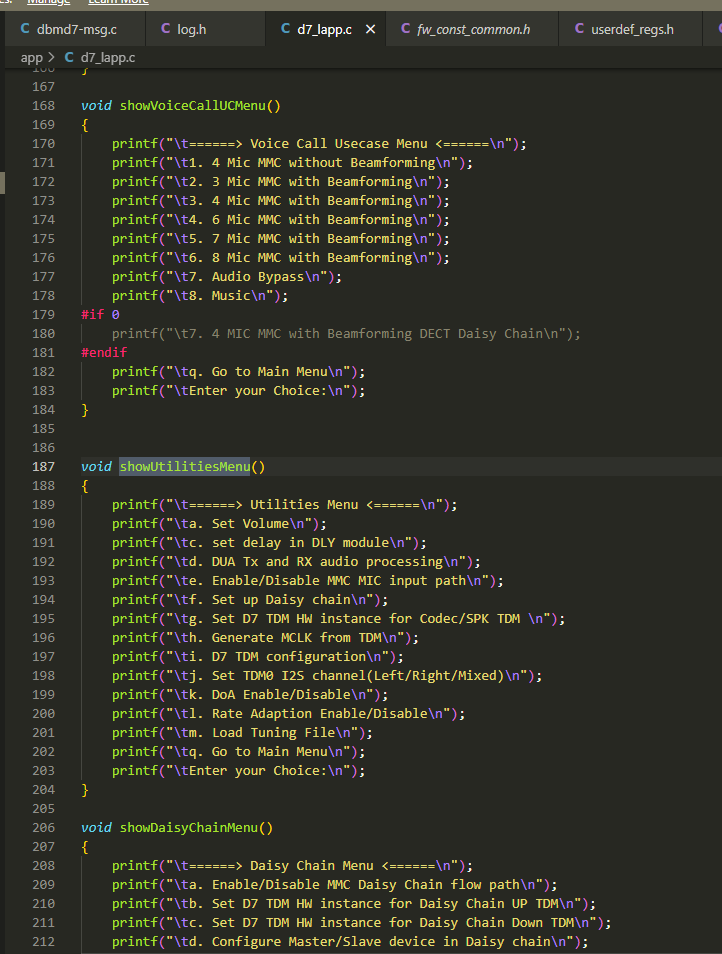

这里我给大家讲解一下大致的原理部分,会议音响的用途主要用于电话会议或者听歌的用途,其电话会议技术层面我们简称Voice Call Use Case,听歌的场景简称Music Use Case。

在该项目的设计中我们需要使用到D7的是哪个TDM口,其使用是TDM0对接MCU(QCC3024)I2S输出/入作为参考信号以及D7 voice call use case处理后的音频传给mcu的信号、TDM1是音频的输出口,也就是传给speack输出的音频数据(这里只需要做输出就行),TDM2是两个音响之间的连接通道,用于传递级联的数据。

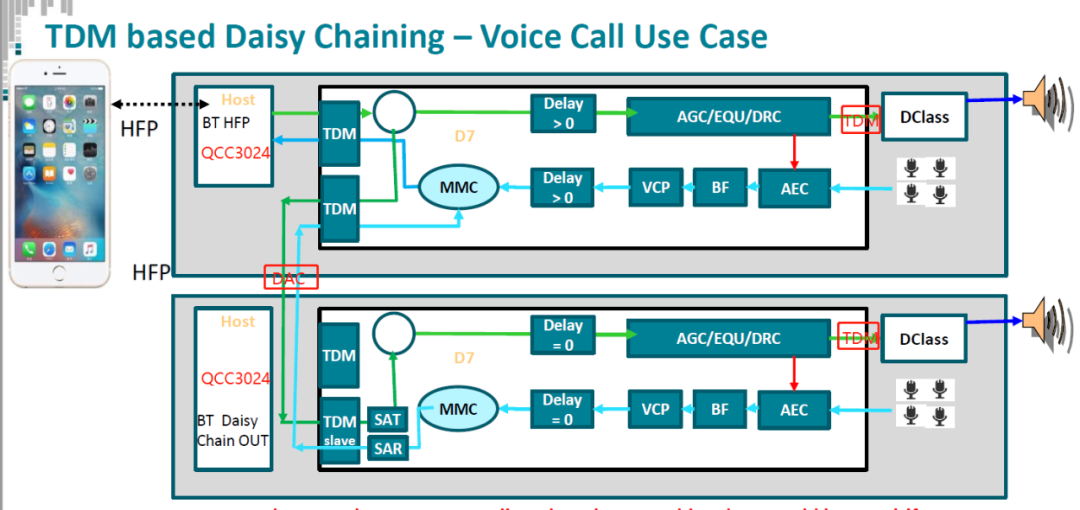

如下是Voice Call Use Case使用场景,如下方框图所示,其中绿色的箭头描述是通话下行的工作流程,蓝色的箭头描述是通话上行的工作流程。

通话下行的工作描述:

手机与QCC3024通过蓝牙连接(该为master机器),将下行的数据从QCC3024的I2S端口输出到master的TDM0端口,然后TDM0分两路传输:一路通过自身算法的AGC/EQU/DRC模块后传输到TDM1口,DTM1再经过DAC输出到speack上。

另一路是直接传输到TDM2,经过DAC模块输出给slave机器。

Slave机器通过TDM2口接收master传过来的声音,也通过自身算法的AGC/EQU/DRC模块后传输到TDM1口,DTM1再经过DAC输出到speack上。

这样就达到了级联同时输出的效果。

通话上行的工作描述:

Slave机器启动voiceCall,将4个MIC的数据收集起来,经过自身算法的AEC/BF/VCP等算法后,集成一路有效的音频数据,通过TDM2输出到master机器的TDM2口。

Master机器启动voiceCall,将4个MIC的数据收集起来,经过自身算法的AEC/BF/VCP等算法后,集成一路有效的音频数据,然后再将slave机器传过来的数据一起合到MMC模块进行算法处理,

MMC处理完成后,将数据直接通过TDM0传输给QCC3024的I2S端口,作为上行数据处理。

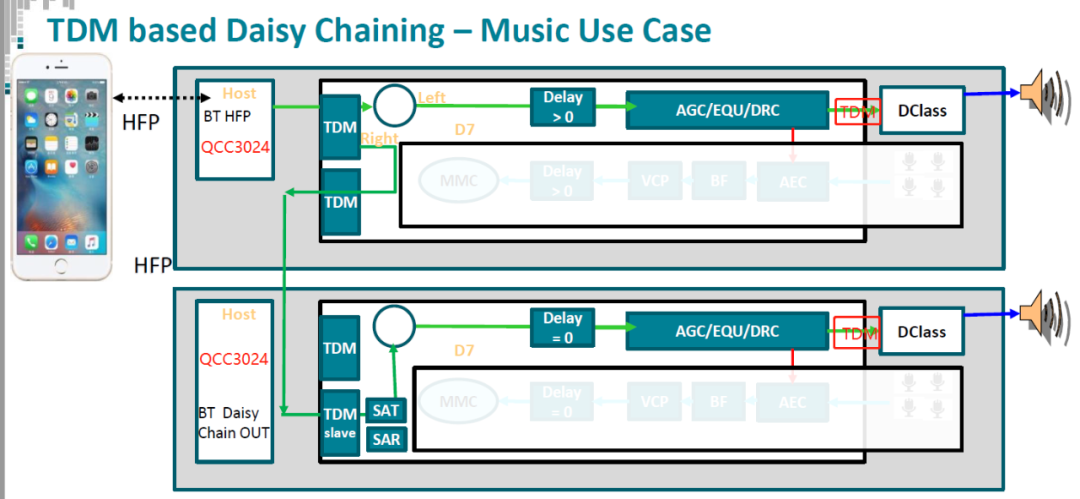

如下是Music Use Case的应用场景,如下方框图所示。其绿色的箭头的指示为左右声道的传输流程。

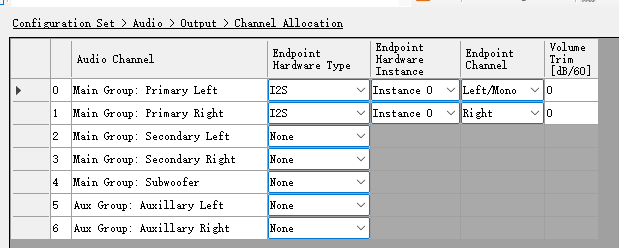

Music Use Case的传输是QCC3024 msater机器将音频数据通过I2S输出传输给TDM0口,TDM0将左声道数据通过自身bypass的功能传输到TDM1,经过DAC传输到speack输出。

Master机器通过TDM0将右声道的数据传输给TDM2,再经过TDM2输出到slave机器的TDM2口,slave机器通过自身bypass的功能传输到TDM1,经过DAC传输到speack输出。

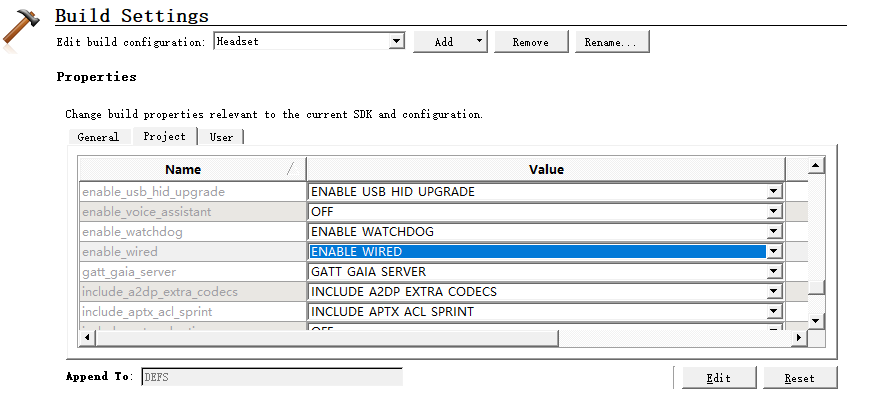

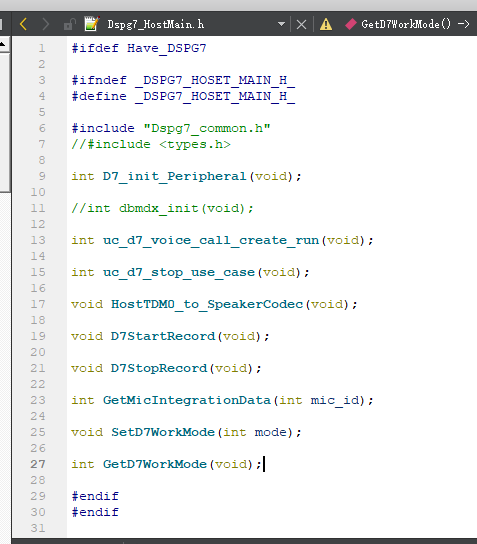

软件实现方法:

配置QCC3024为I2S输出,设置采用率为48K,32bit

移植DSPG的固件到QCC3024的平台上,接口设定为SPI接口。

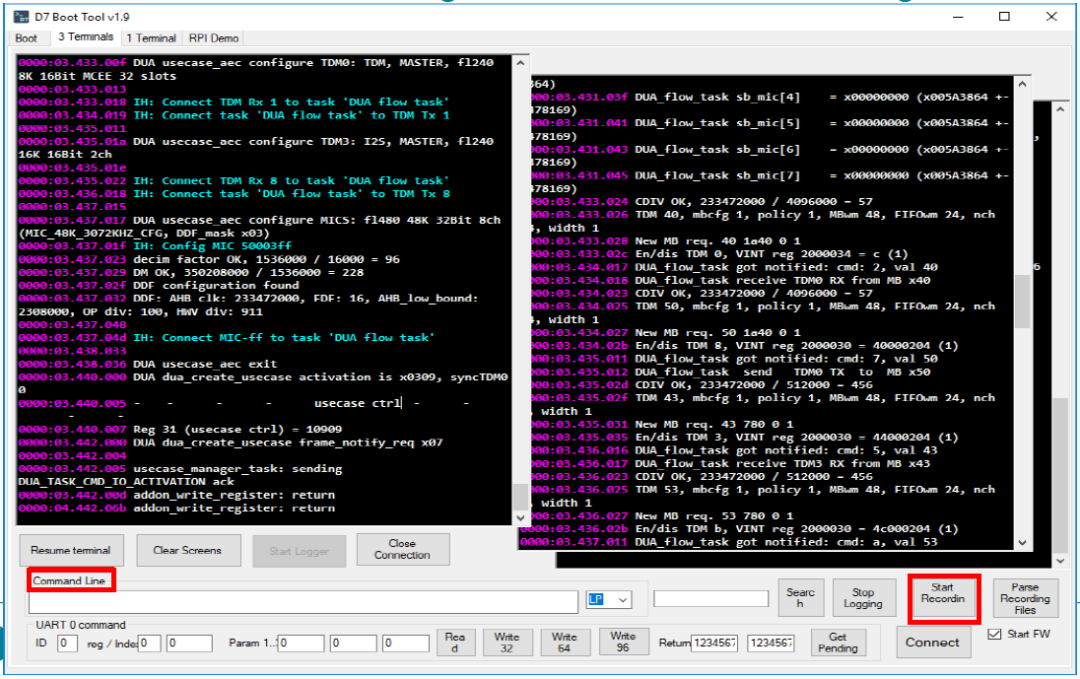

录音测试截图:

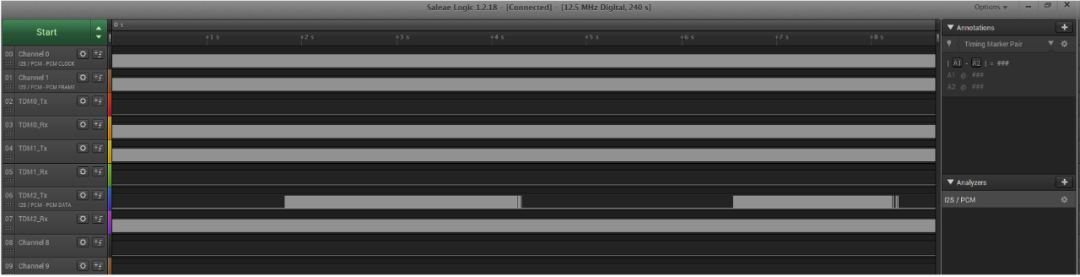

通过逻辑分析仪抓取的数据波形图:

MCU选择的要求:

mcu 必须要支持I2S输出,要支持SPI传输接口以及快速的传输速率(10M/s),这里我们选择高通QCC3024,是可以完全满足要求,最主要是可以得到大联大D7+QCC平台的技术全面支持。我这里选用了QCC3024,当前客户们可以依据你们自己的需求,选择不同的MCU平台。只需要符合上述的要求就可以了。

D7 PCB layout 的技术要求:

1、按照DSPG的要求 对D7板layout必须要4层板或以上。

2、如果MIC是固定在PCB板上,4个MIC的上下距离要保持在7CM以上。

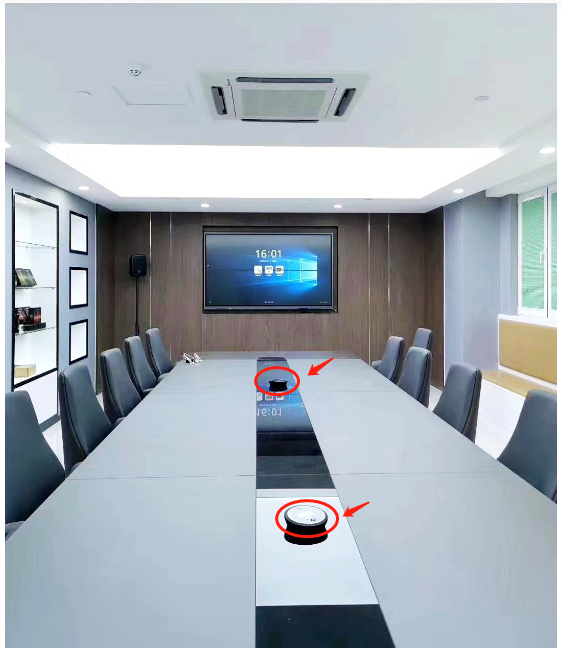

► 场景应用图

► 产品实体图

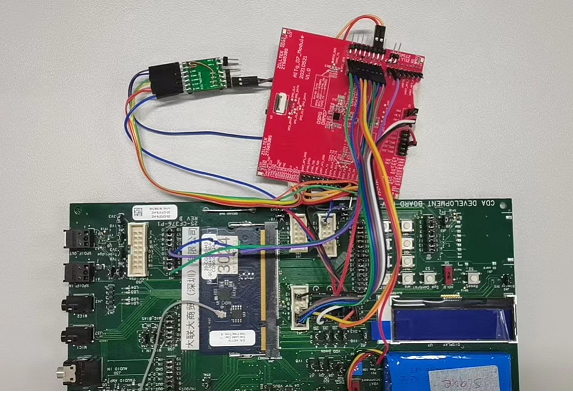

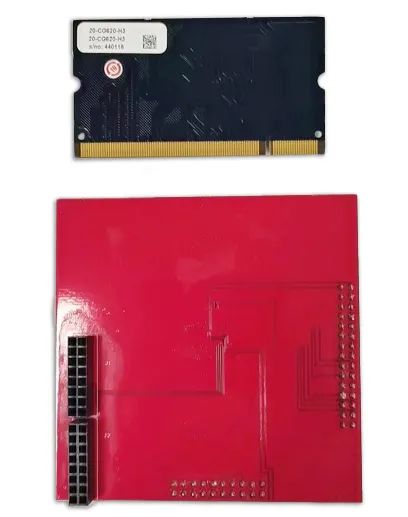

► 展示版照片

► 方案方块图

► PCB Layout 图

► 核心技术优势

DBMD7基于三个CEVA-X DSP处理器。该芯片配备了相关接口,用于与系统中的其他设备进行通信,如应用处理器(AP)、编解码器、数字麦克风和传感器。

DBMD7提供了以下组合:

三种高性能、高效率、低功耗的VLIW/SIMD数字信号处理器

支持丰富的接口集

体积小,适合移动设备

独立操作,与手机AP的简单接口

预处理算法最多可用于8个麦克风,以提高语音触发(VT)、语音命令(VC)和自动语音识别(ASR)性能。

发送路径:VT/VC,VC和音频缓冲,ASR预处理:回声消除(AEC),BF和降噪(NR)

接收路径:音频处理算法

语音通话中最多可使用8个麦克风的预处理算法

发送路径:AEC、NR、EQ、自动增益控制(AGC)

接收路径:NR、AGC、EQ、扬声器处理

DSP核心

DBMD7包括三个CEVA-X2 DSP处理器:

双可编程高频DSP处理器,运行高达700兆赫。

一个可编程低功耗DSP处理器,运行高达125MHz,用于低泄漏VT、检测和激活。

每个CEVA-X DSP处理器提供:

程序紧耦合内存(PTCM):64 KB RAM

程序缓存:32 KB

数据紧耦合存储器(DTCM):64KB RAM

数据缓存:64 KB

3个非矢量中断,1个矢量中断,1个NMI

4MB AXI共享RAM

仅限LP处理器的64KB ROM

► 方案规格

该方案的MUC,我们采用的是Qualcomm 的QCC3024蓝牙芯片,与DSPG的传输接口是通过SPI接口,因为SPI的传输速度快而又稳定。

DBMD7支持用于引导和控制的外部主机接口,速度如下:

SPI:高达25 Mbps

I2C:最高3 Mbps

UART:高达6 Mbps

DBMD7 DSP核心

DBMD7包括三个CEVA-X2 DSP处理器:

双可编程高频DSP处理器,运行高达700兆赫。

一个可编程低功耗DSP处理器,运行高达125MHz,用于低泄漏VT、检测和激活。

每个CEVA-X DSP处理器提供:

程序紧耦合内存(PTCM):64 KB RAM

程序缓存:32 KB

数据紧耦合存储器(DTCM):64KB RAM

数据缓存:64 KB

3个非矢量中断,1个矢量中断,1个NMI

4MB AXI共享RAM

仅限LP处理器的64KB ROM

安全加速器

对代码安全保护、身份验证和回滚保护的安全引导支持提供以下服务:

AES 128代码解密

基于ECDSA的代码认证验证

沙二段(224256)

散列公钥存储的OTP(Fuse)处理和使用

QCC3024硬件规格:

90-ball 5.5 x 5.5 x 1.0 mm 0.5 mm pitch VFBGA

蓝牙5.1规格、DSP最高频率120MHz

一路SPI,支持主或从模式,速率高达15.4 Mbps

支持APTX、AAC、SBC codec

三核处理器架构与低功耗应用

输出支持立体声