【导读】在日前的第 70 届 IEEE 国际固态电路会议 (ISSCC) 期间,韩国存储芯片大厂 SK 海力士(SK Hynix)展示了最新300 层堆叠第 8 代 3D NAND Flash的原型,令与会者大吃一惊。

3月20日消息,在日前的第 70 届 IEEE 国际固态电路会议 (ISSCC) 期间,韩国存储芯片大厂 SK 海力士(SK Hynix)展示了最新300 层堆叠第 8 代 3D NAND Flash的原型,令与会者大吃一惊。

SK海力士在会议在发表会的标题订为 “高密度存储和高速接口”,其中描述了该公司将如何提高固态硬盘的性能,同时降低单个 TB 的成本。

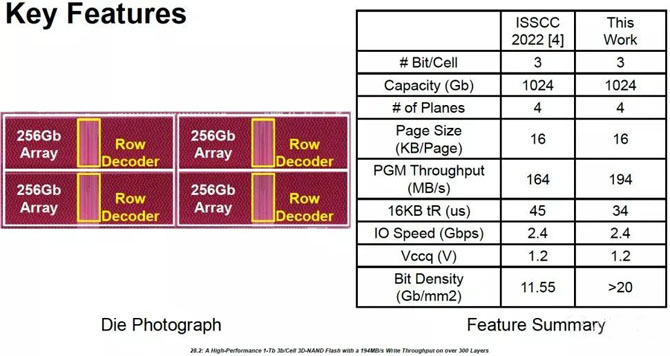

据介绍,SK海力士第 8 代 3D NAND 堆叠超过 300 层,容量为 1Tb(128GB),具有 20Gb/mm2 单位容量、16KB 单页容量(page size)、拥有四个 planes,接口传输速率为2400 MT/s。最大数据传输速率将达到 194 MB/s,相较上一代 238 层堆叠和 164 MB/s 传输速率的第七代 3D NAND Flash高出 18%。而在更快的输入和输出速度下,有助于 PCIe 5.0 x4 或更高的接口利用率。

新 NAND 的位密度增加近一倍,意味着将显著提高新制造节点的每晶圆生产率,也将降低 SK 海力士的成本,只是尚不清楚具体程度。

据 SK 海力士研发团队的说法,第 8 代 3D NAND Flash 采用了 5 项崭新的技术。

首先,其拥有三重验证程序(TPGM) 功能可缩小单元阈值电压分布,并将 tPROG (编程时间) 减少 10%,从而转化为更高的性能。

其次,采用 Adaptive Unselected String Pre-Charge (AUSP) 技术,再将 tPROG 降低约 2% 。

第三,APR方案可将读取时间降低约 2%,并缩短字线上升时间。

第四,编程虚拟串 (PDS) 技术可藉由降低通道电容负载来缩短 tPROG 和 tR 的界线稳定时间。

最后,平面级读取重试 (PLRR) 功能,允许在不终止其他平面的情况下,更改平面的读取级别。之后,立即发出后续读取命令,并提高服务质量 (QoS),从而提高读取性能。

由于 SK 海力士针对新产品还在开发中,因此该公司尚未透露生产最新一代 3D NAND Flash 的量产时间。尽管如此,分析师预计该300层3D NAND Flash将于 2024 年年底或者 2025 年年初上市发售。

(来源:芯智讯)

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。

推荐阅读: