本文分析了SPI 存储器的结构特点和测试难点,提出了一种基于并行转串行逻辑的SPI 存储器算法图形自动产生的方法,并以SPI EEPROM 芯片AT25HP512 为例,实现了测试程序开发。实验证实,该方法可以克服SPI 存储器地址算法自动产生的困难,对该类芯片测试具有通用性。

0 引言

串行存储器大多采用I2C 或SPI 接口进行访问,其中以SPI 接口的芯片最多,主要包括EEPROM、FLASH memory、FRAM等类型。与并行存储器相比,串行存储器引脚少、体积小、易于扩展、与单片机或控制器连接简单、工作可靠,而且大多拥有掉电保持数据的特性,所以越来越多地用在各类电子产品和工业测控系统中。但SPI 存储器所有输入的内容全都由一个管脚完成,通用自动测试仪无法分辨这些信息类型,因此不便于实现地址自动算法产生,这给使用通用测试仪测试该类芯片带来了很大难度。本文首先介绍了SPI 类串行接口存储器的结构,进而以芯片AT25HP512 为例,讲述了其工作原理及测试难点,最后提出了一种能应用于通用自动测试仪的SPI 存储器测试方法。

1 SPI 串行接口存储器的基本结构

1.1 SPI 总线的结构

SPI 是一种通用串行接口总线,字长为8 位或16 位,SPI接口利用SCK、SI 和SO 三根线进行数据读/ 写。其中,SCK 为时钟信号,用于对数据传输的速率进行同步,在每一个SCK 周期,有一位数据移入或移出串行存储器。SI 为串行数据输入,用于输入命令和数据。SO 为串行数据输出,用于输出状态和数据。本文将以一种典型的SPI EEPROM AT25HP512 为例分析其结构及访问方式。图1 为AT25HP512 芯片的管脚定义,其他SPI存储器通常也都有类似的管脚。

1.2 AT25HP512 的读/ 写方式

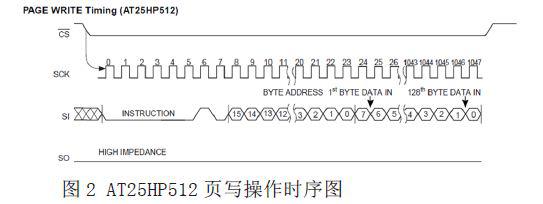

AT25HP512 容量64K 位,采取分页存储的结构,每页128 位,既可随机读/ 写数据,又可以以序列方式连续读/ 写。序列读操作一旦执行,位地址可以自动增加,直到读出所有单元;序列写操作一旦执行,可以完成一页的128 位写。图2 为AT25HP512页写操作的时序图,利用该特性可快速完成数据的访问。

2 使用自动测试仪测试SPI 存储器的难点

2.1 数字集成电路自动测试仪的特点

自动测试仪(ATE),用于检测集成电路功能的完整性。标准的数字ATE 可针对专用及通用数字电路提供高速、高通道数字控制、测试能力。芯片的测试程序通常会有许多个功能测试向量以测试不同的功能模块,这些向量都会被加载ATE 内存中,以顺序或并发方式被执行。在实际生产过程中,由于受ATE 内存大小(即图形深度)的限制,如果向量过长,超过测试设备图形深度,就要加载一段向量,测试一段向量,再加载一段向量,再测试。该做法会使测试成本大为增加,因此往往不允许多次加载,所有测试向量需要一次性加载或由算法自动产生,以保证测试的连续性。

2.2 存储器测试特点

存储器虽然逻辑结构简单,但容量通常较大,而且由于存储器各个存储单元有可能出现相互打扰,即某个存储单元的数据变化可能引起其他单元的变化,因此存储器需要反复读/ 写的测试,测试向量的总长度往往超过ATE 的测试图形深度。针对存储器这种结构固定、可连续访问、测试算法固定的器件,需要ATE 能根据算法自动产生测试图形,用比较短的测试向量,按照固定地址产生逻辑自动完成有规律的地址变化,实现连续读/写操作。

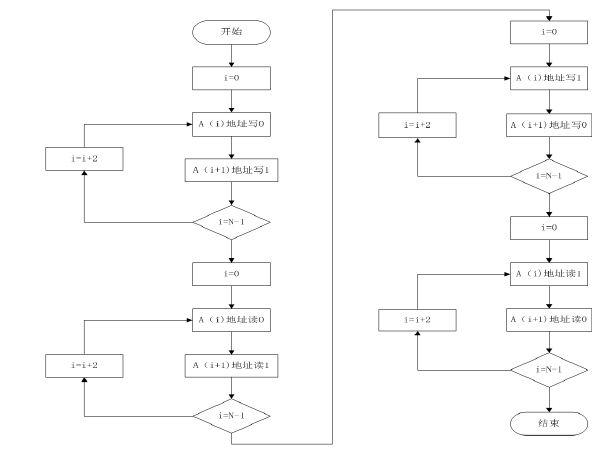

通用ATE 一般都具备一组或多组地址产生器(APG),该单元模块可完成地址保持(HOLD)、自加(INC)、自减(DEC)等操作,使用这些标准逻辑,就可以实现绝大多数的存储器测试算法。以最常用的棋盘格测试算法为例。

如果顺序写测试程序,需要4N 的测试向量深度(N 为存储器容量),但是用测试算法,每一步流程只需要几条向量,全部只需要用几十条向量就能完成,具体方法如图3 所示。可见利用自动地址产生逻辑,可以实现极大深度的存储器测试。

2.3 SPI 存储器测试难点

上述方法可用于多数并行存储器,但难以用于SPI 存储器。

主要原因为:

(1)SPI 存储器没有独立的数据总线和地址总线,所有输入都由SI 这一根线完成,SI 除要发送地址外,还要发送数据和指令,无法独立应用于地址操作,也就无法完成对地址的算法产生,如INC 等;

(2)SPI 总线通常应用8 位寄存器,为完成一个数据传输需要在8 个时钟周期,由8 条向量串行执行,这就大大增加了向量的长度。因此,尽管ATE 有足够的数据宽度,却往往受限于数据位的深度不足,无法完成测试。

3 SPI 存储器的测试实现方法

首先,SCK 信号要按测试需求产生测试时钟,~CS、~WP 和~HOLD 给出相应控制信号。

其次,为了利用了测试仪的通道宽度,减少测试向量的深度,需要将串行发送的数据以并行的方式存储于测试仪中。多数通用测试仪都设计了并行转串行的逻辑模块,即在多个通道上并行输入数据,通过系统指令完成转换,由一个通道将数据发送出来。如果ATE 不具备该功能,也可由外部逻辑实现。

最后,要最大限度地应用测试仪的AGP 模块地址自动产生逻辑,将串行程序算法并行化处理,最终给出区别存储器地址和其他输入信息的控制逻辑。

3.1 棋盘格算法测试

以AT25HP512 棋盘格测试为例,串行SPI 存储器测试可分为以下步骤。

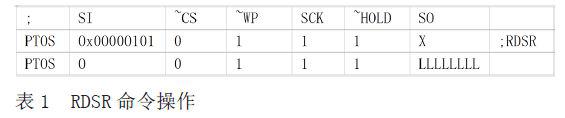

(1)并行转串行。存储器待收发的数据和指令都以8 位并行的方式放置在内部寄存器中,因此要借助ATE 并行转串行输出功能,将8 个通道的数据从一个通道输出。以并行转串行指令PTOS 为例,PTOS 00000101,相当于从SI 引脚在8 个周期串行输出0 0 0 0 0 1 0 1 ;

(2)将指令寄存的数据以8 位并行方式连接到测试通道上。

以读状态寄存器命令为例,SI 要输出的数据连接到不同通道,再由并转串逻辑电路输出。读出的结果与预期值进行比较。

表1 相当于执行了读状态寄存器命令RDSR,本例中读回的预期结果为LLLLLLLL.

(3)设置状态寄存器。发送写状态寄存器命令WRSR,设置存储器为写READY 状态。

(4)将8 位地址线连接到AGP 相关的通道上。

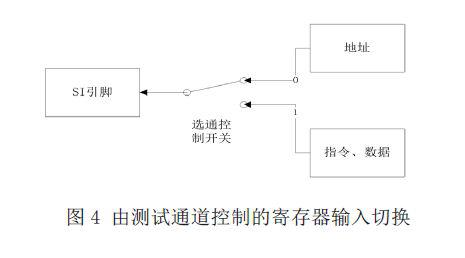

(5)为了能在SI 引脚上既能输出地址又能输出指令和数据,要设置多路选择单元,完成切换。切换控制位可以由通道位完成。图4 为测试通道控制的寄存器输入切换,控制位为0,SI引脚切换至地址线,控制位为1,SI 引脚切换至数据线和指令线。

应用该开关,就可以把需要使用算法的地址和不需要利用算法的指令和数据在通道上分开。

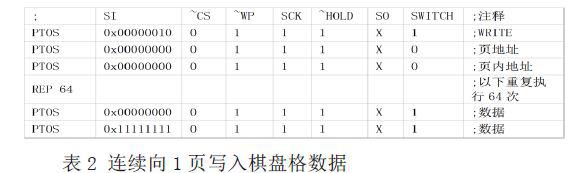

(6) 完成向存储单元写入数据的操作。表2 实现了连续写一页的函数PAGEWRITE 操作,从0 地址开始连续进行128 个写操作,把00000000 和11111111 的棋盘格数据交替写入一页中。

(7) 利用AGP,实现页地址递增操作。每一页写都调用PAGEWRITE,每完成一次页写操作,页地址自动加1,执行下一页的写操作,直到全部页的写操作完成。表3 为每调用一次单页写,页地址自动加1 的操作。

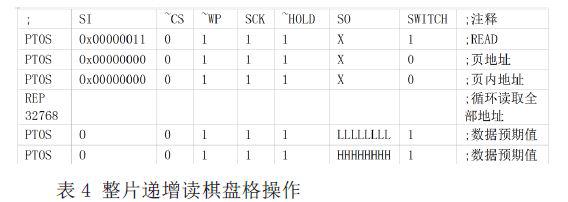

(8) 读并检验结果操作。与写操作类似,给出读指令和起始地址后,可连续读出所有单元。

以上方法,首先完成了逐页的连续写操作,页地址可自动递增,每完成一次正向棋盘格(按0101 格式)写操作后,再以0 地址为起始地址,完成整个器件地址自动递增的连续读操作。然后再按照相同的方法执行一次反向棋盘格(按1010 格式)的写、读,从而实现完整的棋盘格测试。

3.2 其他测试算法

在实际工程中应用最多的是存储器测试法算法复杂度为N的测试算法,除棋盘格测试法外,较为常用的还有齐步法、列条图形法和前进后退法等。应用这些算法测试SPI 存储器都与棋盘格测试类似,只是AGP 自动产生算法的方式不同,本文不再详述。

4 结语

本文分析了SPI 串行存储器的结构和访问方式,利用通用自动测试仪的并行转串行指令,增加了选通控制逻辑,为ATMEL公司的SPI 串行存储器AT25HP512 编写了测试程序,该程序最终以二进制代码的形式顺序存储于测试仪中。实验证明,该方法可以克服SPI 存储器地址算法自动产生的困难,对该类芯片测试具有通用性。