如何通过处理器防止物联网系统软件执行过程中的威胁

基于硬件的加密技术与安全存储提供了实现安全物联网设计所需的基础。安全引导和安全固件空中下载 (FOTA) 更新使用这一基础来建立软件执行的信任根。尽管如此,物联网 (IoT) 设备仍需要得到持续的保护,以防止在运行时环境中执行的软件应用程序和系统代码在访问安全资源时,软件有意或无意地破坏这些资源。

本文介绍了开发人员如何利用 NXP Semiconductors、STMicroelectronics 等公司提供的处理器中集成的安全机制,以更有效地方式防止系统在软件执行过程中受到威胁。

运行时软件如何遭到破坏

如本系列前面几部分所述,密码、安全密钥存储以及安全引导和固件更新为物联网安全提供了必要的构件。尽管这些功能是物联网设备整体安全的关键因素,但对于专门破坏互连系统中运行时软件的攻击,仍是一种不完全的解决方案。理想情况下,由于受信任环境是在通过安全引导创建的信任根基础上所建立,因此试图穿透这些机制所提供的防线将会失败。实际上,使用这些强大的安全功能所构建的系统可能会因在系统中注入一段腐化代码或恶意软件的攻击而被劫持,而且曾经发生的攻击都是采用这种方式。

黑客可以使用各种各样的方法来利用系统某一部分中的安全漏洞攻击其他部分。例如,缓冲区溢出攻击可利用软件应用允许大型输入数据流写入到预期缓冲区外。如果溢出数据包含代码,则处理器可以在之后执行这些代码,从而为黑客提供进一步攻击的入口。通过使用这些方法和其他方法,黑客会逐渐扩大渗透到系统的更广泛部分。

在任何系统软件堆栈层中,任何软件组件都可能存在漏洞。随着开发人员致力于创建功能更丰富的系统,对更多软件组件的需求增加了这些系统遭受更多漏洞攻击的几率。同时,软件中存在的各种漏洞会持续增加。例如,权威的通用漏洞披露 (CVE®) 列表显示,2020 年第一季度公开披露的网络安全漏洞同比增长 15%。

多层保护可保护关键软件

缓和威胁是黑帽黑客与白帽安全专家之间的持久战。虽然威胁将不断出现,但开发人员可以利用各种方法来隔离典型应用程序中要求的多个不同软件进程,来大幅加强设计的安全性。多年来,安全系统一直建立在分层保护方法的基础上。在这种经典方法中,同心保护环可提高系统中的隔离级别。在最外层运行的应用程序受到限制,无法访问内层的设备驱动程序和系统服务,而内层也会受到限制,无法访问最内层的软件内核(图 1)。

图 1:安全软件系统以保护环的形式保护应用程序、驱动程序和操作系统内核,逐渐提供了更大的保护力度。(图片来源:维基百科)

从 80286 开始的 Intel x86 设备现在可从 Rochester Electronics 获取,它们支持四个保护层,并且指定使用选择器寄存器,包括一个两位请求特权级 (RPL) 字段。通过各种用于在运行时隔离用户进程的机制,Arm® TrustZone 等现代处理器架构大幅扩展了安全功能。开发人员可以在许多嵌入式系统处理器中找到这种分层保护功能,其中包括:

Microchip Technology 的 SAM L11 微控制器系列(基于 Arm Cortex®-M23)

Nordic Semiconductor 的 nRF9160 无线片上系统 (SoC)(基于 Arm Cortex-M33)

Nuvoton Technology 的 M2351 微控制器(基于 Arm Cortex-M23)

NXP Semiconductors 的 LPC55 微控制器(基于 Arm Cortex-M33)

Silicon Labs 的 EFR32BG21 无线 SoC 系列(基于 Arm Cortex-M33)

STMicroelectronics 的 STM32L5 微控制器系列(基于 Arm Cortex-M33)

Arm TrustZone for Cortex-M 为 NXP 的 LPC55S69JBD100K 和 STMicroelectronics 的 STM32L552VET6 等 Arm Cortex-M 嵌入式系统处理器带来了增强的安全功能。TrustZone for Cortex-A 为 NXP 的 i.MX 8M Mini MIMX8MM6DVTLZAA 和 STMicroelectronics 的 STM32MP157AAC3T 等基于 Arm Cortex-A 的应用处理器提供了类似的功能。

对于每个 Arm 系列,TrustZone 提供的机制可支持安全引导和安全代码、数据和存储器以及其他安全功能。TrustZone for Cortex-M 处理器旨在支持嵌入式系统的低延迟要求,具有性能增强,包括快速安全中断和基于硬件的快速安全状态转换。本文说明了 TrustZone for Cortex-M 处理器,并重点介绍了代表此类别的一对处理器:NXP 的 LPC55S69JBD100K 和 STMicroelectronics 的 STM32L552VET6。

处理器工作模式实现了扩展保护

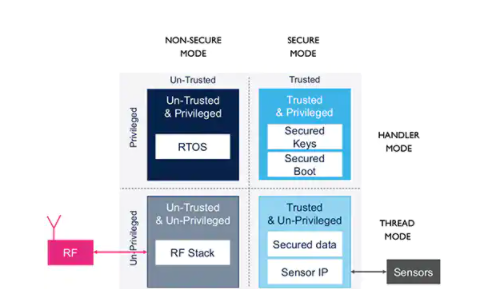

作为 TrustZone 架构的核心,处理器可以在多种工作模式下运行,以支持软件进程和系统资源的隔离。处理器的“安全”和“非安全”模式提供了一种将受信任的进程与不受信任的进程隔离的方法。处理器的“处理程序”和“线程”模式提供了单独的保护机制,在隔离进程和资源方面提供了更高的精细度。

在 TrustZone 架构中,以处理程序模式运行的处理器会使软件始终以特权模式运行。因此,建议使用此模式来运行实时操作系统 (RTOS) 等软件,或访问引导映像、安全密钥以及其他对系统操作至关重要的资源。在线程模式下,软件以非特权模式运行,但是特权进程可以更改在此模式下运行的软件的特权级别。线程模式通常可用于运行应用程序代码。

在组合使用时,安全/非安全与处理程序/线程模式可提供与早期支持保护环的系统同类的分层保护功能。例如,使用 STMicroelectronics 的 STM32L552VET6,开发人员可以将具有完全特权的受信任代码与具有最小特权的不受信任代码隔离开(图 2)。

图 2:STMicroelectronics 的 STM32L552VET6 等 TrustZone 处理器提供了各种处理器模式的组合,能够让开发人员隔离引导映像等受信任系统软件与第三方射频 (RF) 通讯栈等不受信任应用程序代码。(图片来源:Digi-Key,原始资料来源于 STMicroelectronics)

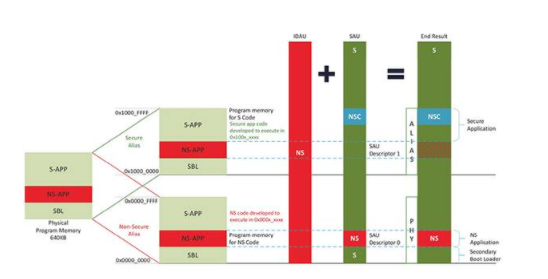

这些处理器中集成的隔离机制限制了每个处理器访问程序数据存储器不同区域的能力。例如,当 NXP LPC55S6x 内核处于安全状态时,尽管仍可访问非安全数据存储器,但却无法访问非安全程序存储器。另一方面,当 LPC55S6x 内核以非安全状态运行时,则只能访问非安全程序存储器和数据存储器(图 3)。

图 3:NXP 的 LPC55S6x 器件等处理器可确保内核在安全状态(S 状态)下运行以读取安全程序存储器(绿色),或在非安全状态(NS 状态)下运行以读取非安全程序存储器(红色)。(图片来源:NXP Semiconductors)

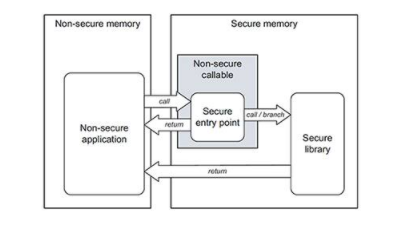

当在安全状态下运行以执行受信任软件时,这些处理器无法从非安全程序存储器中获取指令。相反,当在非安全状态下运行以执行不受信任的软件(例如应用程序代码)时,这些处理器将无法访问位于安全区域中的代码或数据。尽管如此,应用程序代码通常需要能够执行安全库中的受信任代码。通过定义非安全可调用 (NSC) 存储器区域以提供受允许的安全库入口点,TrustZone 处理器能够让开发人员达到此要求(图 4)。

图 4:非安全可调用区域提供了从非安全到安全存储器区域的安全入口点,允许非安全应用程序执行安全库中的函数。(图片来源:STMicroelectronics)

存储器别名可增强安全性

NXP 的 LPC55S69JBD100K 和 STMicroelectronics 的 STM32L552VET6 等 TrustZone 处理器通过将物理程序存储器别名化为安全和非安全存储器空间,来管理执行。例如,STMicroelectronics 的 STM32L552VET6 两次将闪存和 SRAM 中的代码别名化,一次别名化为非安全地址范围(0x0800_0000 至 0x0BFF_FFFF),再次别名化为安全地址范围(0x0C00_0000 至 0x0FFF_FFFF)。同样,NXP 的 LPC55S69JBD100K 将物理程序存储器别名化为从 0x0000_0000 开始的非安全空间,以及从 0x1000_0000 开始的安全空间。这些处理器中的每一个都对其他存储器类型和外设使用类似的方法,将它们两次别名化为安全和非安全区域。

当处理器需要访问某个存储器位置时,能否访问该位置由两个硬件单元生成的安全属性确定:

实现定义属性单元 (IDAU) 是处理器核心外部的固定硬件单元,提供由制造商定义的存储器映射的固定安全状态。

安全属性单元 (SAU) 是集成在处理器核心中的可编程单元,可用于定义多达八个存储器区域的安全状态。

在系统初始化期间,在安全模式下运行的配置例程通过设置几个 SAU 寄存器来定义每个区域的安全状态;这些寄存器包括:

SAU 区域编号寄存器 (SAU_RNR),用于选择一个区域以进一步进行操作

SAU 区域基地址寄存器 (SAU_RBAR),用于定义区域的起始地址

SAU 区域限制地址寄存器 (SAU_RLAR),用于定义区域的范围

在 STM32L5 系列的 STM32Cube MCU 软件包中,STMicroelectronics 提供了多个模板文件,这些文件演示了如何使用包含 SAU 配置在内的处理器功能。如清单 1 所示,开发人员可以使用宏 (SAU_INIT_REGION(n)) 为每个配置参数定义这些区域。该宏能够设置 SAU 结构中的寄存器值,而这些值会在配置设置写入器件时使用。

副本

/*

// 《e》Initialize SAU Region 0

// 《i》 Setup SAU Region 0 memory attributes

*/

#define SAU_INIT_REGION0 1

/*

// 《o》Start Address 《0-0xFFFFFFE0》

*/

#define SAU_INIT_START0 0x0C03E000 /* start address of SAU region 0 */

/*

// 《o》End Address 《0x1F-0xFFFFFFFF》

*/

#define SAU_INIT_END0 0x0C03FFFF /* end address of SAU region 0 */

/*

// 《o》Region is

// 《0=》Non-Secure

// 《1=》Secure, Non-Secure Callable

*/

#define SAU_INIT_NSC0 1

/*

// 《/e》

*/

/*

// 《e》Initialize SAU Region 1

// 《i》 Setup SAU Region 1 memory attributes

*/

#define SAU_INIT_REGION1 1

/*

// 《o》Start Address 《0-0xFFFFFFE0》

*/

#define SAU_INIT_START1 0x08040000 /* start address of SAU region 1 */

/*

// 《o》End Address 《0x1F-0xFFFFFFFF》

*/

#define SAU_INIT_END1 0x0807FFFF /* end address of SAU region 1 */

/*

// 《o》Region is

// 《0=》Non-Secure

// 《1=》Secure, Non-Secure Callable

*/

#define SAU_INIT_NSC1 0

/*

// 《/e》

*/

。

。

。

**

brief Setup a SAU Region

details Writes the region information contained in SAU_Region to the

registers SAU_RNR, SAU_RBAR, and SAU_RLAR

*/

__STATIC_INLINE void TZ_SAU_Setup (void)

{

#if defined (__SAUREGION_PRESENT) && (__SAUREGION_PRESENT == 1U)

#if defined (SAU_INIT_REGION0) && (SAU_INIT_REGION0 == 1U)

SAU_INIT_REGION(0);

#endif

。

。

。

#define SAU_INIT_REGION(n)

SAU-》RNR = (n & SAU_RNR_REGION_Msk);

SAU-》RBAR = (SAU_INIT_START##n & SAU_RBAR_BADDR_Msk);

SAU-》RLAR = (SAU_INIT_END##n & SAU_RLAR_LADDR_Msk) |

((SAU_INIT_NSC##n 《《 SAU_RLAR_NSC_Pos) & SAU_RLAR_NSC_Msk) | 1U

清单 1:此代码段包含在 STMicroelectronics 的 STM32L5 系列 STM32Cube MCU 软件包内的模板中,向开发人员展示如何定义存储器区域及其相关的安全状态。(代码来源:STMicroelectronics)

IDAU 和 SAU 共同确定存储器位置是否可访问,并返回两者中最高的安全级别。由于处理器使用与其安全/非安全工作状态相对应的存储器别名,IDAU 与 SAU 的组合生成的安全属性可确保仅访问具有匹配安全级别的区域(图 5)。

图 5:在 NXP LPC55S69JBD100K 中,IDAU 和 SAU 组合起来为每个存储器别名生成一个安全属性,从而有效地删除不允许在各自区域外运行的代码。(图片来源:NXP Semiconductors)

例如,当 NXP 的 LPC55S69JBD100K 在安全模式下运行时,由 IDAU 和 SAU 生成的安全属性将阻止访问物理存储器块的安全别名中包含的非安全应用程序,从而有效地从安全别名中消除该非安全代码。相反,当处理器在非安全模式下运行时,IDAU 和 SAU 安全属性将有效地从产生的非安全别名中清除安全应用程序。

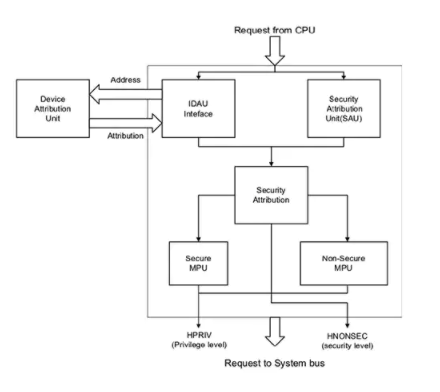

设置权限和访问控制

尽管 IDAU 和 SAU 直接强制安全和非安全访问限制,但它们与安全和非安全存储器保护单元 (MPU) 共同确定与目标资源关联的访问权限(图 6)。

图 6:在图中所示的 NXP LPC55S69JBD100K 等 TrustZone 处理器中,由 SAU 和 IDAU 生成的安全属性与安全和非安全 MPU 管理的设置组合在一起,来提供权限级别和安全级别。(图片来源:NXP Semiconductors)

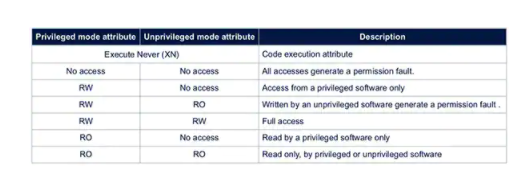

MPU 内置在这些处理器中,可提供对存储器资源的精细访问控制。例如,在 STMicroelectronics 的 STM32L552VET6 中,MPU 支持多种访问权限。在处理器以特权处理程序模式或非特权线程模式运行时,这些访问权限会有所不同(表 1)。

表 1:STMicroelectronics 的 STM32L552VET6 允许开发人员使用其 MPU 来定义在特权模式和非特权模式下具有不同操作方式的不同访问级别。(表格来源:STMicroelectronics)

在这些属性中,Execute Never (XN) 属性能够让开发人员确保处理器永远不会尝试从关联的存储器区域执行代码,从而提供了另一个级别的运行时保护。例如,在直接从闪存运行代码的系统中,开发人员可以为未使用的 SRAM 区域设置 XN 属性,以消除系统遭到劫持的任何可能性,即使恶意代码在这些区域成功注入攻击。

将保护扩展到更多外设和存储器

这些处理器的 IDAU、SAU 和 MPU 功能提供了灵活的基础,以保护系统软件和应用程序的运行时执行,但是这些功能仅限于处理器本身。像 NXP LPC55S69JBD100K 和 STMicroelectronics STM32L552VET6 这样的处理器可通过各种方法,将安全和特权功能扩展到其他存储器系统和接口。

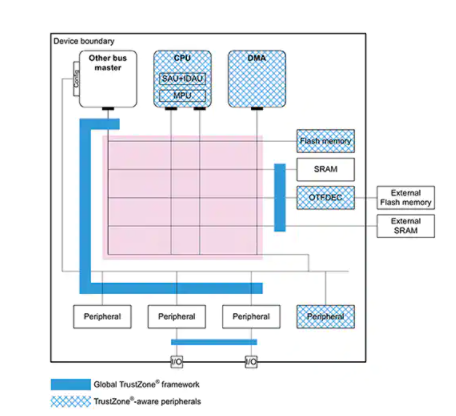

对于 STM32L552VET6,STMicroelectronics 用自己的全局 TrustZone 控制器 (GTZC) 对原生 TrustZone 机制进行了补充。这种全局 TrustZone 控制器旨在保护外设、嵌入式 SRAM 和外部存储器(图 7)。

图 7:STMicroelectronics 的 STM32L552VET6 处理器集成了全局 TrustZone 控制器 (GTZC),可将安全保护扩展至原生 TrustZone 框架中未包含的外设和存储器。(图片来源:STMicroelectronics)

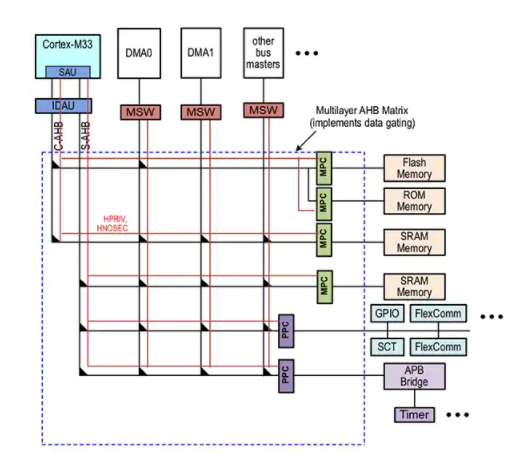

在 NXP LPC55S69JBD100K 中,特权属性 (HPRIV) 和安全属性 (HNONSEC) 跨越内部高级高性能总线 (AHB) 矩阵,传递到存储器保护校验器 (MPC)、外设保护校验器 (PPC) 和其他总线主控器的主安全包装器 (MSW)(图 8)。

图 8:在 NXP LPC55S69JBD100K 中,特权和安全级别会传递至其他硬件单元,而硬件单元可将这些属性应用于涉及存储器、外设和其他总线主控器的操作。(图片来源:NXP Semiconductors)

虽然了解软件隔离和系统保护的底层机制很重要,但开发人员可以利用开发支持在自己的设计中快速应用这些功能。

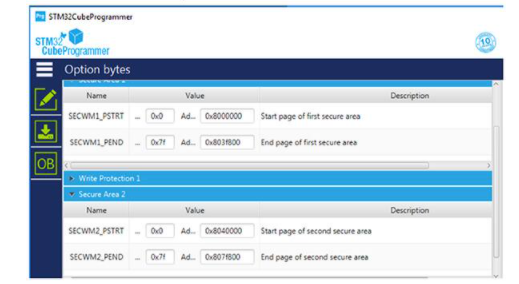

STMicroelectronics 提供了 STM32L552E-EV、STM32L562E-DK 和 NUCLEO-L552ZE-Q 评估板作为快速原型开发平台,用于构建基于其 STM32L5 处理器的应用。该公司的 STM32CubeIDE 集成开发环境 (IDE) 提供了综合的软件编程环境,并且其 STM32CubeProgrammer 提供了图形用户界面 (GUI) 和命令行界面 (CLI) 版本,用于对内部和外部存储器进行编程。例如,使用此工具,开发人员可以定义闪存中的安全区域(图 9)。

图 9:STMicroelectronics 的 STM32CubeProgrammer 提供了一种简单的方法来定义闪存中的安全区域。(图片来源:STMicroelectronics)

为了快速开发基于 NXP 的 LPC55S69 处理器的系统,开发人员可以在 NXP 的 LPC55S69-EVK 评估板上构建设计。对于系统配置和软件编程,NXP MCUXpresso IDE 提供了一个综合性平台,可用于创建基于 NXP LPC55S69 处理器的应用。

结语

物联网安全依赖于密码学和安全存储等基本安全机制,以及在基于硬件安全机制的信任根上构建应用的功能。尽管这些都是确保安全的必需条件,但很少能够足以应对那些利用系统运行时环境中漏洞的持续威胁。通过利用越来越多的处理器中提供的分层保护机制,开发人员可以构建安全的物联网设备,更好地缓解这些威胁并减少或消除它们对物联网应用的影响。

本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。