一、环境介绍

MCU: STM32F103ZET6

代码开发工具: Keil5

TCP/IP协议栈: LWIP

网卡: DM9000

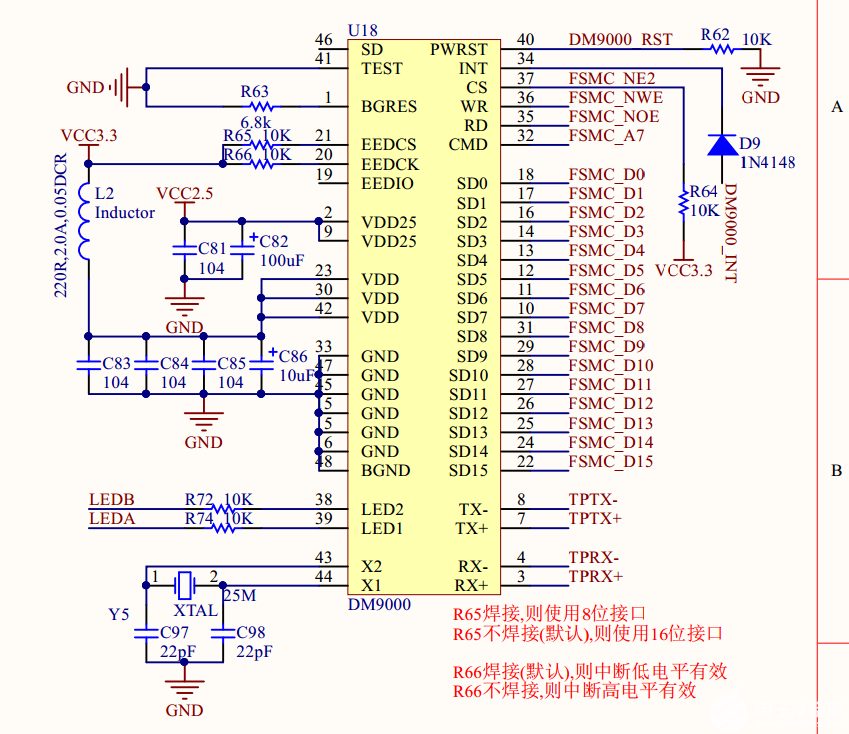

本篇文章主要讲解如何在STM32F103工程里添加移植LWIP协议,最终完成TCP服务器、TCP客户端的通信测试。 网卡采用的是DM9000,工程代码中,采用STM32的FSMC接口来驱动DM900网卡,DM9000是并口网卡,引脚多,但是速度快,也可以采用其他网卡,SPI协议的、UART协议的等。 比如:ENC28J60。 因为主要是讲LWIP协议栈的移植,所以网卡相关的代码就没有细说(需要准备一个网卡可以正常通信的工程,再移植)。

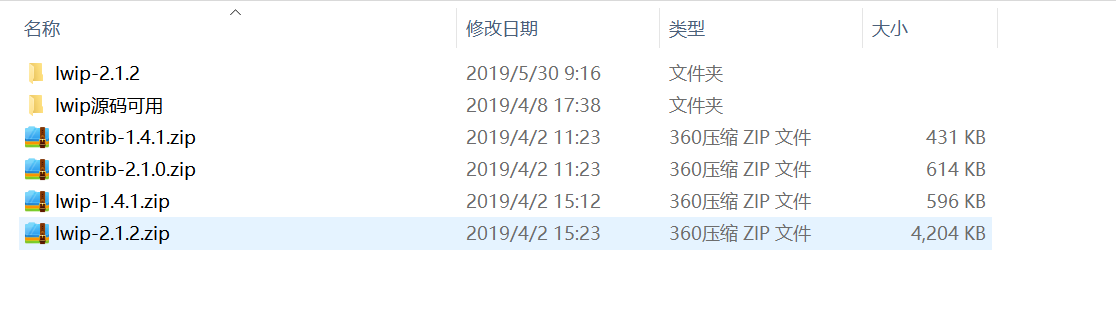

下面进行工程的移植代码比较多,需要下载对应版本的LWIP源码,STM32本身的DM9000网卡代码也比较多,文章里会讲解移植的详细的过程,代码贴出了核心部分。

为了方便大家下载体验,下面给了个下载链接,里面包含了本次文章移植的工程、LWIP源码,移植文档等,方便直接体验。地址在这里:https://download.csdn.net/download/xiaolong1126626497/19907087

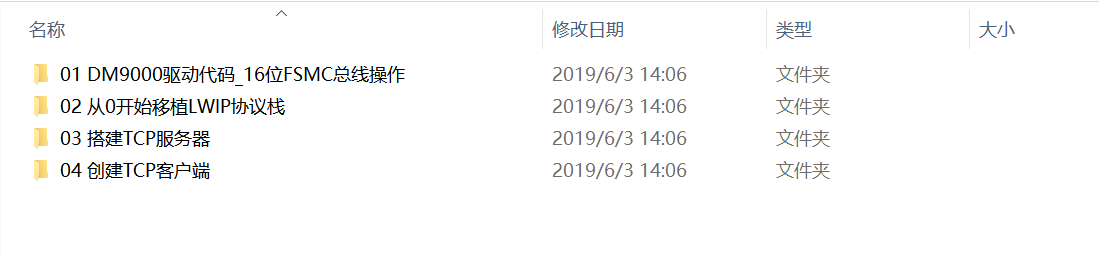

资料包里的内容如下:

二、D9000网卡

2.1 DM9000简介

DM9000 是一款完全集成的、性价比高、引脚数少、带有通用处理器接口的单芯片快速以太网控制器。 自带一个 10/100M PHY 和 4K 双字的 SRAM ,DM9000A 为适应各种处理器提供了8位、16 位数据接口访问内部存储器,DM9000拥有自动协商功能,DM9000特性如下:

1、集成自适应10/100M收发器。

2、内置16k字节的SRAM。

3、支持硬件帧校验。

4、兼容3.3V和5.0V输入输出电压。

DM9000 有多种型号,有 100 引脚和 48 引脚的, 开发板选择的是 48 引脚的 DM9000,型号为 DM9000CEP。

2.2 DM9000 中断引脚电平设置

DM9000的34(INT)引脚为中断输出引脚,默认情况下该引脚高电平有效。可以通过设置DM9000 的 20(EECK)引脚来改变 INT 的有效电平,当 EECK 拉高以后, INT 低电平有效,否则的话 INT 是高电平有效的。开发板上 R66 电阻为 EECK 的上拉电阻,因此开发板上 DM9000 的 INT 引脚是低电平有效的。

2.3 DM9000 数据位宽设置

前面我们提了一下 DM9000 支持 8 位和 16 位两种数据位宽,可以通过 DM9000 的 21(EECS)引脚设置其数据位宽,当 EECS 上拉的时候 DM9000 选择 8 位数据位宽,否则的话选择 16 位数据位宽。开发板上的 R65 电阻为 EECS 的上拉电阻,但是此电阻并未焊接! DM9000 芯片的数据位宽为 16 位。

2.4 DM9000寄存器表

寄存器 |

描述 |

寄存器地址 |

默认值 |

|

NCR |

网络控制寄存器。 |

00H |

00H |

|

NSR |

网络状态寄存器。 |

01H |

00H |

|

TCR |

发送控制寄存器。 |

02H |

00H |

|

TSR I |

发送状态寄存器 I。 |

03H |

00H |

|

TSR II |

发送状态寄存器 II。 |

04H |

00H |

|

RCR |

接收控制寄存器。 |

05H |

00H |

|

RSR |

接收状态寄存器。 |

06H |

00H |

|

ROCR |

接收溢出计数寄存器。 |

07H |

00H |

|

BPTR |

背压门限寄存器。 |

08H |

37H |

|

FCTR |

溢出控制门限寄存器。 |

09H |

38H |

|

FCR |

TX/RX 流量控制寄存器。 |

0AH |

00H |

|

EPCR |

EEPROM/PHY 控制寄存器。 |

0BH |

00H |

|

EPAR |

EEPROM/PHY 地址寄存器。 |

0CH |

40H |

|

EPDRL |

EEPROM/PHY 数据寄存器低位。 |

0DH |

XXH |

|

EPDRH |

EEPROM/PHY 数据寄存器高位。 |

0EH |

XXH |

|

WCR |

唤醒控制寄存器。 |

0FH |

00H |

|

PAR |

物理地址寄存器。 |

10H~15H |

由 EEPROM 决定 |

|

MAR |

广播地址寄存器。 |

16H~1DH |

XXH |

|

GPCR |

通用目的控制寄存器(8bit 模式)。 |

1EH |

01H |

|

GPR |

通用目的寄存器。 |

1FH |

XXH |

|

TRPAL |

TX SRAM 读指针地址低字节。 |

22H |

00H |

|

TRPAH |

TX SRAM 读指针地址高字节。 |

23H |

00H |

|

RWPAL |

RX SRAM 写指针地址低字节。 |

24H |

00H |

|

RWRAH |

RX SRAM 写指针地址高字节。 |

25H |

0CH |

|

VID |

厂家 ID。 |

28H~29H |

0A46H |

|

PID |

产品 ID。 |

2AH~2BH |

9000H |

|

CHIPR |

芯片版本。 |

2CH |

18H |

|

TCR2 |

发送控制寄存器 2。 |

2DH |

00H |

|

OCR |

操作控制寄存器。 |

2EH |

00H |

|

SMCR |

特殊模式控制寄存器。 |

2FH |

00H |

|

ETXCSR |

即将发送控制/状态寄存器。 |

30H |

00H |

|

TCSCR |

发送校验和控制寄存器。 |

31H |

00H |

|

RCSCSR |

接收校验和控制状态寄存器。 |

32H |

00H |

|

MRCMDX |

内存数据预取读命令寄存器(地址不加 1)。 |

F0H |

XXH |

|

MRCMDX1 |

内存数据读命令寄存器(地址不加 1)。 |

F1H |

XXH |

|

MRCMD |

内存数据读命令寄存器(地址加 1)。 |

F2H |

XXH |

|

MRRL |

内存数据读地址寄存器低字节。 |

F4H |

00H |

|

MRRH |

内存数据读地址寄存器高字节。 |

F5H |

00H |

|

MWCMDX |

内存数据写命令寄存器(地址不加 1) |

F6H |

XXH |

|

MWCMD |

内存数据写命令寄存器(地址加 1)。 |

F8H |

XXH |

|

MWRL |

内存数据写地址寄存器低字节。 |

FAH |

00H |

|

MWRH |

内存数据写地址寄存器高字节。 |

FBH |

00H |

|

TXPLL |

TX 数据包长度低字节寄存器。 |

FCH |

XXH |

|

TXPLH |

TX 数据包长度高字节寄存器。 |

FDH |

XXH |

|

ISR |

中断状态寄存器。 |

FEH |

00H |

|

IMR |

中断屏蔽寄存器。 |

FFH |

00H |

|

2.5 DM9000常用寄存器介绍

NCR、 NSR、 TCR、 RCR、 FCTR、 BPTR、 TCR2、 ISR、 IMR。

NCR(网络控制寄存器)寄存器

BIT |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

名称 |

RESERVED |

WAKEEN |

RESERVED |

FCOL |

FDX |

LBK |

RST |

FCOL:强制冲突模式,用于检测。

FDX:内部 PHY 全双工模式。

LBK:回环模式(LoopBack)

00 正常;

01 MAC 内部回环;

10 内部 PHY100M 模式数字回环;

11 保留;

RST:置 1 软件复位, 10us 后自动清零。

NSR 寄存器(网络状态寄存器)

BIT |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

名 称 |

SPEED |

LINKST |

WAKEST |

RESERVED |

TX2END |

TX1END |

RXOV |

RESERVED |

SPEED:网络速度,在使用内部 PHY 情况下,0 表示 100Mbps,1 表示 100Mbps,当 LINKST=0时,此位无意义。

LINKST:连接状态, 0 为连接失败, 1 位已连接。

TX2END: TX(发送)数据包 2 完成标志,读取或写 1 将清零该位。

TX1END: TX(发送)数据包 1 完成标志,读取或写 1 将清零该位。

RXOV: RX(接收)FIFO 溢出标志。

TCR 寄存器(发送控制寄存器)

BIT |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

名 称 |

RESERVED |

TJDIS |

EXCECM |

PAD_DIS2 |

CRC_DIS2 |

PAD_DIS1 |

CRC_DIS1 |

TXREQ |

TJDIS: Jabber 传输禁止。

1,禁止 Jabber 传输定时器(2048 字节)。

0,使能。

EXCECM:严重冲突模式控制

0,当冲突计数多于 15 则终止本次数据包。

1,始终尝试发送本次数据包。

PAD_DIS2:禁止为数据包 II 添加填充。

CRC_DIS2:禁止为数据包 II 添加 CRC 校验。

PAD_DIS1:禁止为数据包 I 添加填充。

CRC_DIS1:禁止为数据包 I 添加 CRC 校验。

TXREQ: TX(发送)请求,发送完成后自动清零该位

RCR 寄存器(发送控制寄存器)

BIT |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

名称 |

RESERVED |

WTDIS |

DIS_LONG |

DIS_CRC |

ALL |

RUNT |

PRMSC |

RXEN |

WTDIS:看门狗定时器(2048 字节)禁止。

1,进制

0,使能

DIS_LONG:丢弃长数据包, 1,丢弃数据包长度超过 1522 字节的数据包。

DIS_CRC:丢弃 CRC 校验错误数据包。

ALL:允许广播。

RUNT:允许小于最小长度的数据包。

PRMSC:各种模式。

RXEN:接收使能。

FCTR 寄存器(流控制阈值寄存器)

BIT |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

名称 |

HWOT |

HWOT |

HWOT |

HWOT |

LWOT |

LWOT |

文章来源于:电子工程世界 原文链接

本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关文章  映泰发布Z170GTN迷你主板:无敌信仰灯(2016-09-30)

接口有四个SATA 6Gbps、一个M.2 32Gbps、一个U.2 32Gbps,扩展接口提供一条PCI-E x16、一条M.2 2230(无线网卡专用),集成Intel I219V千兆网卡。

Realtek......

是Intel i226-V 2.5千兆网卡、AQC113万兆网卡、AX1690 Wi-Fi 6E无线网卡(蓝牙5.3)。音频则是7.1声道。

接口有两个雷电4/USB4、一个HDMI 2.1......

以太网供电设备控制电路设计详解(2024-08-09)

是在最初的以太网技术基础上于1980年开发成功的。现在,以太网一词泛指所有采用CSMA/CD协议的局域网。以太网2.0版由数字设备公司、Intel公司和Xerox公司联合开发,它与IEEE802.3......

Intel逼你升级!华硕Z270高端主板全曝光:好帅但爱不起(2016-11-30)

Intel逼你升级!华硕Z270高端主板全曝光:好帅但爱不起;随着传言1月5日发布日的临近,Intel七代酷睿Kaby Lake和200系(H/B/Z)新主板即将与消费者见面。

此前,我们......

技嘉静音迷你机太帅:骁龙835你行吗?(2017-01-13)

系列。

这款“GB-EAPD-4200 BRIX”的体积只有165×105×27毫米,不过0.46升,可以壁挂,内部采用Intel Apollo Lake超低功耗平台,具体处理器型号没说,不过从HD......

AMD全新座驾:技嘉两款300系主板曝光(2016-11-02)

Intel 200系列)。

AMD的新款芯片组将有X370、B350、A320等不同型号,同时支持Zen CPU、APU,还会引入DDR4、NVMe、M.2、USB 3.1 Gen2、PCI-E 3.0等一......

凌华智能推出AmITX Mini-ITX 主板,助力边缘人工智能和物联网创新(2024-11-22 11:29)

Intel®Core™ i9/i7/i5/i3 和 Intel® N97 处理器,提供灵活的性能选择• 通过 PCIe 5.0 x16、DDR5 和 2.5GbE PoE 为高性能应用提升速度• 通过......

亚信电子与安勤科技携手共创TSN技术新浪潮(2023-07-18)

信电子与安勤科技共同合作开发完成。基于安勤科技SLP-WHG无风扇设计工业电脑(IPC),搭载高性能第8代Intel® Core™ i7处理器,与RT-Linux实时操作系统开发环境,同时......

澜起科技发布全新第四代津逮CPU,以英特尔第四代至强可扩展处理器为内核(2023-01-12)

上一代产品,第四代津逮®CPU采用先进的Intel 7制程工艺,其最大核心数为48核,最高睿频频率为4.2GHz,最大共享缓存为105MB,关键性能指标大幅提升。

同时,在带宽、吞吐、延时......

车规级SSD硬盘标准已来(2023-08-11)

、ADAS域、座舱域不可能都装一个PCIe网卡,为解决这个问题,Intel提出了SR-IOV。SR-IOV最初应用在网卡上。简言之,就是一个物理网卡可以虚拟出来多个轻量化的PCI-e物理设备,从而......

|

技术咨询

技术咨询 代买器件

代买器件 商务客服

商务客服 研发客服

研发客服