这两年,中国大陆掀起了轰轰烈烈的晶圆厂建设热潮,尤其是12寸晶圆厂,更是雨后春笋般布满中国各地高新园区。根据SEMI去年12月的预测,在未来十年内,全球将会有62座半导体晶圆厂投产,其中有26座位于中国大陆,占全球总数的42%。

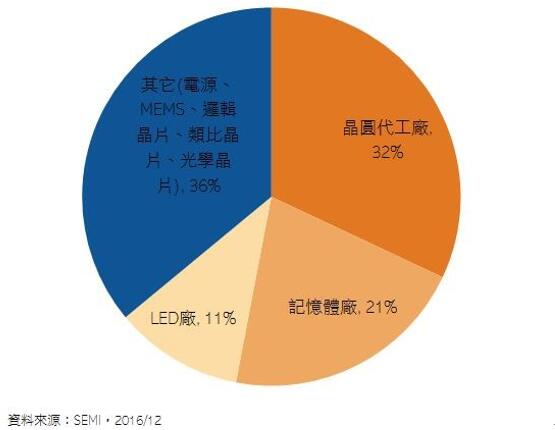

未来十年的新增晶圆厂类别

在这波建厂热潮当中,有一家厂商预见到了未来庞大的市场需求,宣布建设第二条12英寸生产线,并于去年年底正式开工,那就是华力。在国家政策和市场利好的推动下,华力将怎样发挥其优势并继续前进呢?

日前,在CITE 2017上,半导体行业观察采访了上海华力微电子有限公司副总裁舒奇,听他讲述华力微的现在和未来。

55nm节点是主力,携手合作伙伴扩大影响力

2010年1月,华力微电子成立上海,这是由上海联和投资有限公司、上海华虹(集团)有限公司、上海华虹NEC电子有限公司和宏力半导体制造有限公司联合投资建立的公司。

据舒奇副总裁介绍,现在他们的客户也主要集中在55nm逻辑工艺产品上,另外还有NORFlash产品,当中以55nm逻辑工艺占大多数。除了55nm逻辑,55nm CIS,55nm eFlash、65nm NOR Flash,55nm ULP等都是华力目前专注的领域。苦心经营的华力获得了多个国内外一线IC设计公司的认可。而这些认可来自于他们对技术的持续投入和对市场趋势的把握。这在华力新近获得高度认可的55nm ULP平台上体现得淋漓尽致。

众所周知,在即将爆发的物联网时代,对低功耗需求达到了前所未有的苛刻,如何打造低功耗的芯片成为设计商和制造商的共同目标。华力的55nm ULP就是这样产生的。

据介绍,华力55nm ULP工艺平台是基于华力成熟的55nm LP工艺,通过一系列的工艺改善与器件性能提升稳定,从完整的设计和IP生态系统层面出发,从芯片整体设计考虑降低漏电,是一个立足于提供物联网应用的完整解决方案。按照舒奇先生所说,这是一个国际领先、国内尖端的集成电路工艺技术,与以前的通用型55纳米低功耗工艺平台比较电压降低了30%,功耗降低了20%。提供了eHVT和eLVT核心器件,支持核心工作电压最低调降至0.9V,能够帮助客户打造低功耗的无线互联网产品、NB-IOT产品和可穿戴产品,提升其市场竞争力,减少国内IC设计公司对国外相关技术的依赖。

“在未来,这个工艺还能结合射频工艺以及嵌入式闪存工艺,提供客户完整的可穿戴芯片方案”,舒奇先生强调。

除了紧跟市场,推出相应的技术平台外,与第三方的合作,也是保持华力竞争力的另一个关键。舒奇先生表示,在和日本客户的合作中,根据客户需求做IP开发,就是这方面的一个典型例子。近期和Cypress的合作,更是一个同类合作典范。

日前,Cypress基于华力55nm低功耗工艺和Cypress SONOS知识产权开发的低功耗嵌入式闪存产品开始量产。据介绍,这个55nm嵌入式闪存平台主要定位微处理器和物联网应用,。与别的嵌入式闪存技术需要额外加入9到12层光罩不同,SONOS技术只需要在原有CMOS工艺上加入3张光罩,这就让得整个方案具有很好的成本优势。

未来华力能给予这个平台,提供一个集成度更高、功耗更低、成本更有优势的差异化方案。

推进工艺和厂房升级,满足多样化需求

虽然在目前的工艺上有很大的成本优势,但是随着产品要求的转变,性能的提升,还有产能的需求,晶圆代工厂也需要做技术和厂房升级,满足多样化需求。

去年,华力宣布了他们的二厂计划,在问到关于这个厂的目标时,舒奇先生告诉半导体行业观察的记者,按照目前的规划二厂将会在今年年底封顶,并与2018年下半年进行28nm部分量产,初期的预计产能为每月1万片。而在工艺方面,根据舒奇的介绍,会先从28nm PolySiON入手,然后再进入到28nm HKMG,后者目前已经在研发,计划在2019年量产。而二厂一期的满载产能为35000片一个月,舒奇先生强调。

除了在传统的工艺上投入,华力还会在新工艺上做尝试,他们在二厂二期规划了FD-SOI,,如果市场有需求,他们能够迅速响应,推出量产产线。

国内晶圆代工市场,未来将会面临一波竞争,在问到未来将如何保持自己竞争力时,舒奇先生表示,加强客户服务、保证平台多样性,还有客制化平台,这是他们的特点,未来并会继续保持,这样就会让他们持续获得客户的认可。