每当芯片行业中出现一个新的技术趋势时,制定规则的几乎都是欧美大厂,在概念和技术的领先优势下,其他人只能跟在后面按照规则玩游戏。但这一次,中国推出了自己的Chiplet()标准。

12 月 16 日,在 “第二届中国互连技术与产业大会”上,首个由中国集成电路领域相关企业和专家共同主导制定的《接口总线技术要求》团体标准正式通过工信部中国电子工业标准化技术协会的审定并发布。

据介绍,这是中国首个原生 Chiplet 技术标准。

Chiplet,芯片界的乐高

简单表述一下什么是Chiplet。

借用长江证券研报给出的解释,所谓的Chiplet,是一种可平衡计算性能与成本,提高设计灵活度,且提升IP模块经济性与复用性的新技术之一。

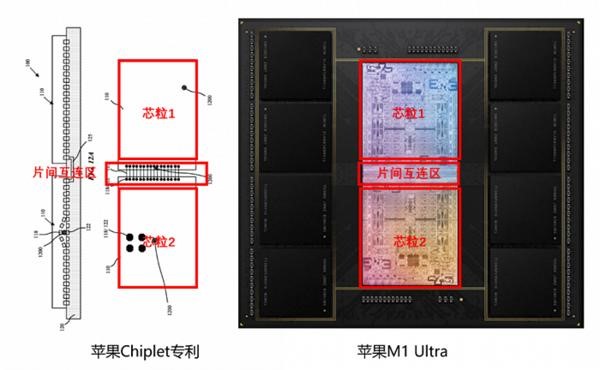

本质上是IP核芯片化的小芯粒,将SoC分解为单独的、预先在工艺线上生产好的、实现特定功能的芯片裸片,再将这些模块化的小芯粒互连起来,并通过2.5D或3D的技术封装在一起,从而形成一颗异构集成系统级芯片。

Chiplet模式是在摩尔定律趋缓下的半导体工艺发展方向之一。该方案通过将多个裸芯片进行先进封装实现对先进制程迭代的弯道超车。与传统的SoC 方案相比,Chiplet 模式具有设计灵活性、成本低、上市周期短三方面优势。近年国际厂商积极推出相关产品,如华为鲲鹏920、AMD 的Milan-X 以及苹果M1 Ultra 等。

被寄予厚望的“”

大约在一年前,也就是2021 年 5 月,中国计算机互连技术联盟(CCITA)在工信部立项了 Chiplet 标准,即《小芯片接口总线技术要求》,由中科院计算所、工信部电子四院和国内多个芯片厂商合作展开标准制定工作。

其实,在中国推出自己的小芯片标准之前,国际上已由英特尔、AMD、台积电等芯片公司联合成立了Chiplet联盟,并定制了1.0标准,计划对原本各家自有的Chiplet技术进行规范,对接口和协议等方面形成统一公认的标准,以此推动Chiplet生态建设。但由于近年来国际形式复杂多变,一味依靠国际标准很难保证技术的平稳长久发展,国内行业需要从标准到应用生态中的每一环都独立可控。

因此,拥有自己的Chiplet标准对中国集成电路产业延续“摩尔定律”,突破先进制程工艺限制具有重要意义。

与国际标准互不冲突

《小芯片接口总线技术要求》描述了 CPU、GPU、人工智能芯片、网络处理器和网络交换芯片等应用场景的小芯片接口总线(chip-let)技术要求,包括总体概述、接口要求、链路层、适配层、物理层和封装要求等。

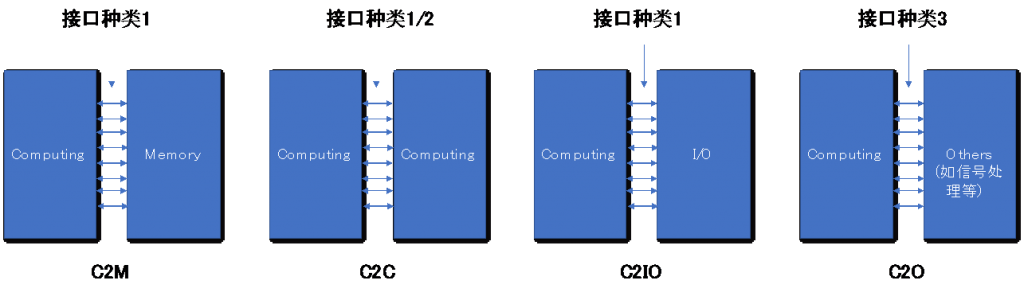

据介绍,小芯片接口技术有以下应用场景:

· C2M (Computing to Memory),计算芯片与存储芯片的互连。

· C2C (Computing to Computing),计算芯片之间的互连。两者连接方式:

· 采用 并行单端 信号相连,多用于 CPU 内多计算芯片之间的互连。

· 采用 串行差分 信号相连,多用于 AI、Switch 芯片性能扩展的场景。

· C2IO (Computing to IO),计算芯片与 IO 芯片的互连。

· C2O (Computing to Others),计算芯片与信号处理、基带单元等其他小芯片的互连。

此标准列出了并行总线等三种接口,提出了多种速率要求,总连接带宽可以达到 1.6Tbps,以灵活应对不同的应用场景以及不同能力的技术供应商,通过对链路层、适配层、物理层的详细定义,实现在小芯片之间的互连互通,并兼顾了 PCIe 等现有协议的支持,列出了对封装方式的要求。

虽然我们拥有了属于自己的小芯片标准,但毕竟1.0标准是全球业内统一的标准,因此认可度和适用性更加广泛。据了解,中国的小芯片设计不但可以使用国际先进封装方式,比如 CoWoS,也可以充分利用国内封装技术积累,实现一种或者几种成本低廉、重点针对 Chiplet 芯片架构、可以覆盖 80% 以上应用场景的先进封装手段。

郝沁汾作为中国小芯片标准的主要发起人和起草人,他在谈到中国发布的小芯片相关技术标准时指出:“中国的小芯片标准是开放的,从标准的协议到参考实现都是开放的,实现参考设计所需的技术细节,我们都可以在标准协议中找得到。我们将围绕这样一套原生的技术标准,进一步完善标准内容,开发相应的参考设计,并孵化相应的企业,以推动我国集成电路行业围绕 Chiplet 技术形成更加广泛的社会分工。“

至于中国小芯片标准与 的关系,郝沁汾表示,中国小芯片标准更偏重本土化的需求,与 UCIe 并不是竞争关系,目前 CCITA 已经在考虑和 Intel UCIe 在物理层上兼容,以降低 IP 厂商支持多种 Chiplet 标准的成本。

那么对于中国首个Chiplet标准发布,各位读者是怎么看的呢?