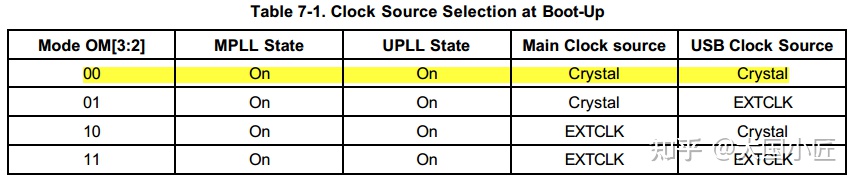

时钟源选择

在nRESET的上升沿锁存OM[3:2]引脚,两个引脚在原理图中都接地,所以都为低电平。所以MPLL的时钟源来源于晶振;UPLL的时钟源也来源于晶振。

2. 配置流程

t1时刻:上电后,晶振起振,FCLK直接由晶振产生;

t2时刻:nRESET拉高,OM[3:2]被所存,晶振作为MPLL与UPLL的输入,但是由于MPLL与UPLL还未配置,所以FCLK还是工作于晶振时钟;

t3时刻:软件设置PLL CONTROL REGISTER (MPLLCON & UPLLCON)寄存器,配置MDIV、PDIV、SDIV的值,决定MPLL与UPLL的输出频率;紧接着设置CLOCK DIVIDER CONTROL (CLKDIVN)寄存器,配置FCLK/HCLK/PCLK之间的比例;这个时候PLL进入锁定状态;

t4时刻:锁定时间结束,PLL输出稳定。