不同位宽设备的连接

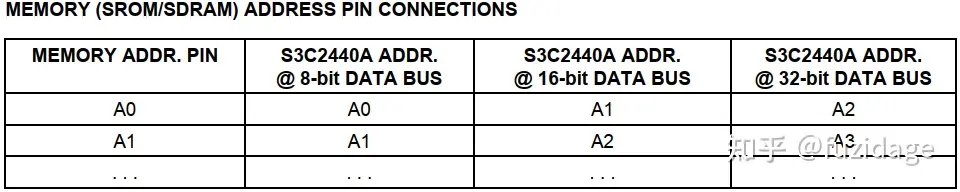

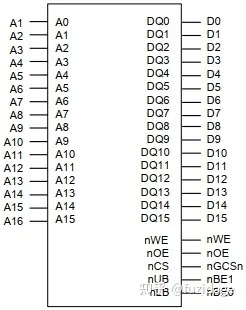

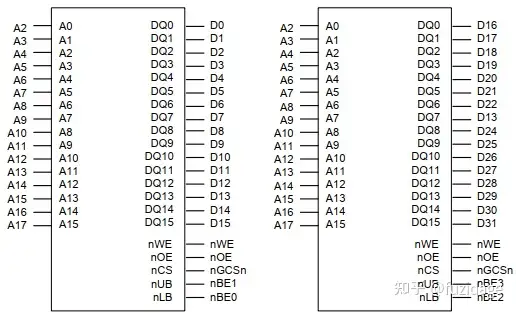

我们先看一下2440芯片手册上外设rom是如何与CPU地址总线连接的。

8bit rom与CPU地址线的连接

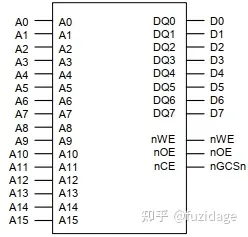

8bit*2 rom与CPU地址线的连接

8bit*4 rom与CPU地址线的连接

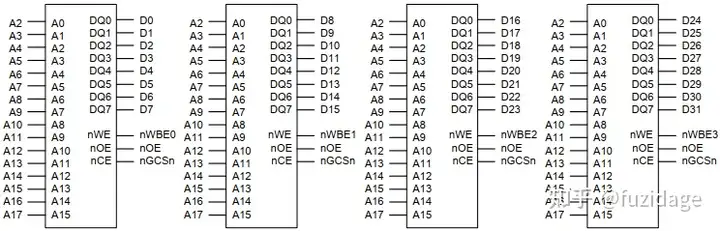

16bit rom与CPU地址线的连接

16bit*2 rom与CPU地址线的连接

从上面的图中,我们知道可以对2片位宽为8bit的外设扩展级联成1个16bit的外设,同理可用4片位宽为8bit的外设进行级联成1个32bit的外设...

从上面的图中,我们还看见一个规律:

当外设总线位宽为8bit时, 外设A0接CPU的地址总线ADDR[0], A[1]->ADDR[1] ...A[15]->ADDR[15] 当外设总线位宽为16bit时,外设A0接CPU的地址总线ADDR[1], A[1]->ADDR[2] ...A[15]->ADDR[16] 当外设总线位宽为32bit时,外设A0接CPU的地址总线ADDR[2], A[1]->ADDR[3] ...A[15]->ADDR[17]

那么为什么要这样设计呢?

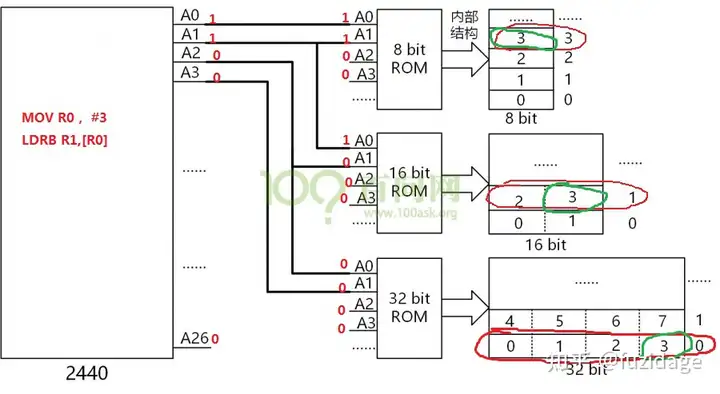

我们先看一个例子: 假设CPU执行:

MOV R0, #3 LDRB R1, [R0] @ 从内存地址为3的地方,读出一个字节

如图有8bitROM、16bitROM、32bitROM

(1)对于8bitROM ,8bit是一次读写的最小单位,即0地址是第一个8bit,1地址是第二个8bit;

CPU发出地址3,即A0和A1都为1,8bitROM的A0和A1收到的也都是1,

于是找到了ROM上地址为3的8bit数据,包含了我们需要的数据。

(2)对于16bitROM ,16bit是一次读写的最小单位,即0地址是第一个16bit,里面有两个8bit数据;

CPU发出地址3,即A0和A1都为1,16bitROM的A0和A1分别收到的是1和0,

于是找到了ROM上地址为1的16bit数据,包含了我们需要的数据,最后内存控制器再帮我们挑选出所需的8bit数据。

(3)对于32bitROM ,32bit是一次读写的最小单位,即0地址是第一个32bit,里面有四个8bit数据;

CPU发出的地址3,即A0和A1都为0,32bitROM的A0和A1收到的都是0,

于是找到了ROM上地址为0的32bit数据,包含了我们需要的数据,最后内存控制器再帮我们挑选出所需的8bit数据。

用表格更好理解:

| ROM/bit | CPU发出地址 | ROM收到地址 | ROM返回数据 | 内存控制器挑选出数据给CPU |

|---|---|---|---|---|

| 8bit(ROM) | 0b000011 | 0b000011 | 编号3的存储单元中的8数据 | 编号3的存储单元中的8数据 |

| 16bit(ROM) | 0b000011 | 0b000001 | 编号1的存储单元中的16数据 | 根据”A0=1”,挑出低8bit数据 |

| 32bit(ROM) | 0b000011 | 0b000000 | 编号0的存储单元中的32数据 | 根据”A1A0=11”,挑出最低8bit数据 |

结论:

和cpu地址总线相连的外设地址线确定了要访问外设的地址,即哪个存储单元;

然后内存控制器拿到外设存储单元中的数据后,再根据那几个错开的引脚[A1-A0]的值(CPU地址总线没接的那几个引脚的值),来挑出相应的数据给CPU。

再举一个栗子: 假如读取一个32位的数据时

MOV R0, #4

LDR R1, [R0] @去地址4,读取4字节数据

我们知道CPU发出的是32bit地址,那么

对于16bit Rom,内存控制器会给它发2次,rom也会相应的接收2次;

对于8bit Rom,内存控制器给它发4次, rom接收4次,

那么CPU怎么知道它外接的rom位宽是16bit,8bit还是多少...?

当然内存控制器知道了,配置总线位宽寄存器。 如何配置总线位宽寄存器

执行过程如下:

| ROM/bit | CPU发出地址 | ROM收到地址(内存控制器转发给rom) | ROM返回数据 | 内存控制器组装数据给CPU |

|---|---|---|---|---|

| 8bit(ROM) | 0b000100 | 0b000100 | 地址4的一个1byte数据 | 组装地址7、6、5、4数据成4字节数据 |

| 0b000101 | 地址5的一个1byte数据 | |||

| 0b000110 | 地址6的一个1byte数据 | |||

| 0b000111 | 地址7的一个1byte数据 | |||

| 16bit(ROM) | 0b000100 | 0b00010 | 地址2的一个2byte数据 | 组装地址3、2的数据成4字节数据 |

| 0b00011 | 地址3的一个2byte数据 | |||

| 32bit(ROM) | 0b000100 | 0b00001 | 地址1的一个4byte数据 | 直接返回4字节数据 |

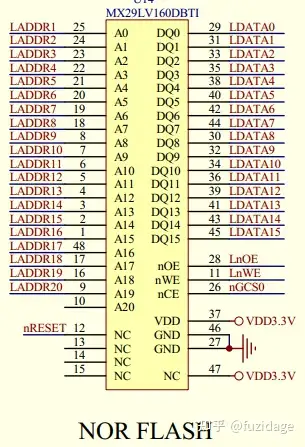

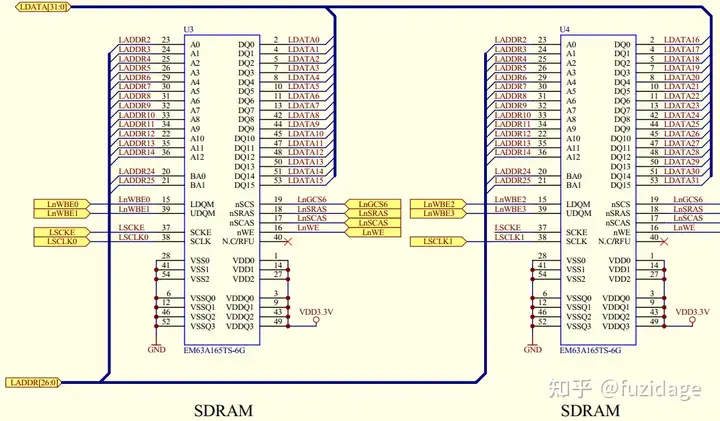

怎样确定芯片的访问地址?

1. 根据片选信号确定基地址 2. 根据芯片所接地址线确定范围

| 外设类型 | 接内存控制器的哪个片选 | 基地址 | 占用CPU的地址总线 | 地址范围(offset + size) |

|---|---|---|---|---|

| nor | nGCS0 | 0x0000,0000 | ADDR0-ADDR20 | 0x0000,0000 ~ 0x001f,ffff(2M) |

| dm9000网卡 | nGCS4 | 0x2000,0000 | ADDR0和ADDR2 | 0x2000,0000 ~ 0x2000,0005(5byte) |

| sdram | nGCS6 | 0x3000,0000 | ADDR0-ADDR25 | SDRAM的地址范围 |

这里再次提醒一下,有人发现nor没有和CPU的ADDR0相连接,sdram没有和CPU的ADDR0、ADDR1相连接。不要觉得ADDR0、ADDR1没用到,由于nor数据位宽是16bit,ADDR0是给内存控制器拆分数据用的,同样sdram数据位宽32bit,ADDR0、ADDR1也是给内存控制器拆分数据用的。这个上面已分析过,这也是什么要错位连接的原因。