结果表明,非易失性(NV)SRAM是用于存储安全数据的最安全的存储器。通过使用 DES 或三重 DES 加密内存,可以建立加密边界,使安全信息不被黑客渗透。通过使用防篡改反应传感器,可以进一步保护SRAM的易失性,这些传感器将擦除加密密钥作为响应。密码键盘等金融应用依靠自动程序和数据存储器加密功能来保护数据。DS5250是一款高性能、安全的8051微控制器,利用安全SRAM的独特特性来保护敏感数据。

无论是在自动取款机、护照/身份验证设备还是便利店的销售点终端中,都必须保护密码、个人识别码 (PIN)、加密密钥和专有加密算法等关键信息免受黑客攻击。金融服务采用详细的政策和程序来保护硬件和软件。因此,金融交易系统的设计者在开发每年处理数十亿美元的设备时面临着具有挑战性的权衡。

为了保持信任,支付系统必须具有端到端的安全性。中央银行的服务器位于一个有围栏的受限访问建筑物内,但公共场所的远程支付终端很容易受到黑客入侵。尽管可以用保护外壳包围微控制器并连接辅助防盗报警系统,但坚定的攻击者仍然可以通过关闭电源来击败警报系统。即使可以打开机箱,如果外壳与微控制器的防篡改加密边界耦合,也会为安全信息创建一个安全的茧。为了真正安全,支付系统架构必须在使用受信任计算机的芯片中内置防篡改技术。通过这种方式,执行计算的芯片通过快速擦除密钥、程序和数据存储器¹来保护其加密边界免受入侵。安全微控制器最强大的防御措施是在检测到篡改时快速擦除内存内容。DS5250安全高速微控制器不仅能擦除存储器内容,而且还是一种廉价的嵌入式系统,带有SRAM用于程序和数据存储。

使用物理内存建立信任

大多数嵌入式系统都是使用通用计算机开发的,这些计算机具有灵活性和易于调试。但是,如果这些好处导致安全漏洞²,它们可能会成为责任。黑客的第一个攻击点通常是微控制器的物理存储器,因此在支付终端使用最佳存储器技术尤为重要。现成的逻辑分析仪,如惠普HP16500B型,可以物理监控地址和数据总线的电信号,这可能会揭示存储器和私有数据的内容,如密钥。防止这种窃听的两个最重要的对策是在内存总线上使用强加密技术,并选择即使在没有电源的情况下也能快速擦除的内存技术。一些嵌入式系统通过使用具有内部浮栅存储器(如EPROM或闪存)的微控制器来尝试安全性。但最好的内存技术会擦除其内容,而不是试图隐藏它。虽然可擦除紫外线的EPROM不需要电力进行擦除,但提供紫外线几分钟的尴尬增加了其脆弱性。闪存或EEPROM存储器要求处理器保持工作状态,电源电压保持在指定的工作范围内,才能成功完成擦除。这些浮栅内存技术对于安全应用程序来说是糟糕的选择,因为它们在断电时无限期地保持其状态,使黑客有无限的时间来发现敏感数据。更好的方法是使用像SRAM这样的存储器技术,如果断电或篡改检测电路被激活,它会以下列方式之一做出反应:

断电后,内存默认为零。

内部存储器和加密密钥在纳秒内擦除 通过篡改检测电路。

外部存储器可在应用软件控制下擦除 写入时间小于 100ns。

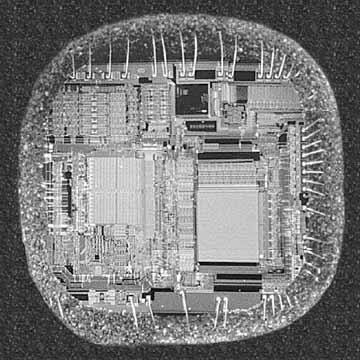

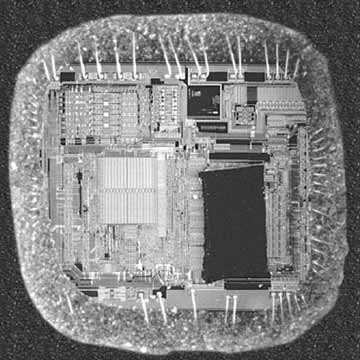

一些设计人员可能会试图通过将微控制器与存储器放在同一芯片上来克服浮栅存储器的脆弱性。这可以防止未经授权访问其内存内容。某些实现使用一个或多个内部锁位,设置为编程结束时的最后一步。设置后,这些位可防止微控制器在从印刷电路板上脱焊并放置在设备编程器(例如广泛使用的BP微系统型号BP-1700通用工程编程器)中时显示其内容。实际上,擦除锁定位的唯一方法是擦除所有存储器,这允许对设备进行重新编程,但在此过程中会破坏程序存储器内容。进一步的安全尝试包括添加内部存储器加密阵列,当设备程序员尝试验证或转储其内容时,该阵列对存储器阵列的输出进行加密。英特尔 MCS® 51 家族处理器就是一个例子,该处理器使用 64 字节用户编程的加密阵列,该阵列在验证期间将内存内容与加密阵列进行 XNOR。除非用户知道加密数组的内容,否则在验证操作期间提取的任何信息都是毫无意义的。但是,即使是锁位方法也可能被击败。在技术期刊和互联网新闻组³中很容易找到入侵浮栅器件(如EPROM、EEPROM和闪存)以及有选择地擦除安全锁位的技术。一些设备制造商建议,采用实心塑料封装的一次性可编程器件可提供一定程度的防锁位黑客攻击保护。然而,“保护程度”是一个相对术语。热酸的应用可以在模具上溶解塑料封装而不会损坏它。然后,使用简单且廉价的Karl Suss PM 8手动探针台等工具仔细研究模具布局,可以揭示安全锁头的位置。这种技术通常在UV可擦除EPROM上执行。解封后,用不透明的油漆甚至电工胶带涂上芯片,并在锁头的位置上仔细地制作针孔。将设备暴露在强烈的紫外线下,然后擦除安全锁定位,但主内存阵列不受影响。然后可以在标准编程器中读取该器件,就好像从未设置过锁定位一样(图 1 和图 2)。半导体公司通常会执行这种简单的程序来分析故障。

图1.微控制器芯片显示酸解封后暴露的EPROM。

浮栅内存技术对于安全应用程序来说是糟糕的选择,因为它们在断电时无限期地保持其状态,使黑客有无限的时间来发现敏感数据。更好的方法是使用像SRAM这样的内存技术。

图2.同一微控制器覆盖了其EPROM阵列,暴露了安全锁定位,以便于擦除。

浮栅存储器技术的另一个缺点是,存储器单元本质上是非易失性的,即使从微控制器断电,也能保持其内容。当从浮栅设备断电时,数据的衰减时间以数百年为单位。当基于私钥基础结构 (PKI) 的系统需要长期保护私钥时,这种时间流逝是一个问题4,因为它让黑客有无限的时间在设备执行篡改响应之前突破芯片中的物理防御并访问内存。

SRAM 和速度

所有安全应用都需要快速的读/写周期时间,以实现最高级别的保护。SRAM是所有存储器技术中最快的。它可以作为篡改响应的一部分立即擦除或“归零”。此外,SRAM广泛可用,价格合理,并具有安全数据存储的独特功能。4.虽然具有固有的挥发性,但在没有V的情况下,它可以很容易地使非挥发性超过10年抄送使用锂备份,它还可以为时间戳和约会交易的实时时钟供电。浮栅存储器技术无法实现这些功能。

对交易进行身份验证

当今支付终端的PINpad模块为金融支付系统提供了核心信任。该模块受银行当局和信用卡发卡机构监管,需要一个带有常驻软件的安全微控制器,其中包括键盘、磁条读卡器、智能卡读卡器和 LCD 显示器的设备驱动程序。还必须有某种与通用主机(PC,486,ARM)进行高速串行通信的方法,以及用于安全端到端通信的PKI加密例程。PINpad模块微控制器的存储器占用空间可能高达数百KB,超过单个芯片的经济尺寸,因此需要外部存储器。如前所述,除非微控制器和外部存储器之间的通信使用强加密技术,否则外部存储器容易受到窃听。这种加密方案有几个相互构建的要求:

加密/解密必须以与指令相当的速率进行 执行。必须在每个程序上执行加密操作 获取或一小组字节(如果使用块加密(如数据) 加密标准 (DES)。加密算法必须强大, 快速且基于硬件。卓越的解决方案是三重 DES (3DES) 使用专用的片上 3DES 硬件,其执行速度比 通过单个 DES 加密器的多次传递。

外部存储器必须是SRAM以支持高数据传输速率 加密引擎需要。还需要电池备份的SRAM 以便在检测到篡改时可以快速擦除内存。

对加密操作至关重要的数据,例如加密密钥 切勿在处理器外部看到。处理器必须生成 并安全地存储至少一部分加密密钥。这些 密钥作为篡改响应的一部分被擦除,呈现外部 记忆难以理解。

程序和数据的初始加载和加密必须由 微处理器内部的引导加载程序。这可以防止未经授权的 查看应用程序代码并隐藏加密方法,使 引导加载程序防火墙。引导加载程序不仅必须阻止访问 对已经加载的信息,但还必须防止敌对代理 防止加载未经授权的流氓软件。一个例子是捕获 工作密码键盘或 ATM,擦除其软件并加载新软件 旨在从不知情的用户那里收集 PIN 码。因此,所有 引导加载程序和主机系统之间的通信必须加密 防止敌对特工拦截和解码。

。SRAM是所有存储器技术中最快的,可以作为篡改响应的一部分立即擦除或“归零”。

DS5250 — 集于一体

通过使用加密,可以构建带有SRAM的嵌入式系统,用于程序和数据存储。DS5250安全微控制器就是这种系统的一个例子(图3)。它每秒执行多达 6 万条基于 25 的指令,将其程序和数据存储器存储在高达 8051MB 的外部 SRAM 中。最敏感的信息可以存储在8kB的内部数据存储器中。SRAM的数据保留通过微处理器内的专用电池开关硬件处理,该硬件提供任一V抄送或电池电源到外部存储器。这种系统可以连接到身份验证外围设备,例如符合 ISO-7816 标准的智能卡读卡器、指纹扫描仪和键盘。

图3.DS5250的执行速度高达6.25 MIPS,并将程序和数据存储器存储在高达8MB的外部SRAM中。

程序和数据总线上的专用加密/解密引擎可确保外部总线的安全性。DS5250的程序存储器总线采用8字节块加密,可选择单通道或3DES。数据存储器总线可选择使用专用硬件进行实时加密。密钥生成由真正的随机数生成器辅助,该生成器通过了联邦信息处理标准出版物 4-11 (FIPS PUB 1-140) 第 1.140.1 节“加密模块的安全要求”中所述的统计随机数生成器测试。程序内存完整性检查功能通过将各个块的校验和与先前计算的值进行比较,进一步提高了内存安全性。块校验和无法匹配存储的值会引发用户可编程的篡改响应,从而防止替换攻击。

除了支持NV SRAM外,DS5250还集成了许多系统安全功能。高性能 4096 位模算术加速器 (MAA) 单元在 1024ms 内以 6 位的模幂为 RSA 计算提供支持。额外的5kB内部SRAM可用于密钥存储、数据存储器和/或程序存储器,并用作MAA的暂存存储器。应用软件使用基于链密码、双密钥 3DES 加密算法的引导加载程序质询/响应协议通过串行端口安全加载。另外,DS5250允许系统设计人员创建专用引导加载程序软件,利用微控制器的所有安全特性。

内部篡改传感器可以检测微处理器芯片上的物理攻击并启动篡改响应,擦除用于解码外部存储器的加密密钥。用户定义的传感器或开关可以连接到自毁输入引脚,这些引脚具有相同的篡改响应,但也会破坏存储在内部代码/数据RAM存储器中的任何数据。此外,自毁输入可消除SRAM的所有电源,确保所有程序和数据存储器丢失。连接到外部引脚的自毁中断源允许系统软件根据特定实现的需求灵活地创建自定义篡改响应。然而,DS5250安全微控制器芯片具有独立的加密边界,具有防篡改反应,因此无需额外的篡改响应,从而降低了系统成本。图4A和4B对比了常见的安全方法与DS5250方法。

图 4A.嵌入式系统设计人员通常倾向于使用具有相关外设/存储器的通用微控制器构建安全计算机,将印刷电路板包裹在多个昂贵的篡改传感器中。

图 4B.DS5250安全微控制器具有独立的加密边界,具有防篡改反应,无需额外的篡改响应,从而降低了系统成本。

确保其安全

每个金融终端,无论是密码键盘、POS 终端还是 ATM,都会处理驻留在其 RAM 和 ROM 中的机密信息。这使得内存组件对于金融交易的安全性至关重要。随着黑客变得越来越复杂,用于保护机密信息的安全方法也必须如此。尽管有许多级别的保护,但加密SRAM为嵌入式存储器内容提供了最佳保护。

也许最重要的是,DS5250安全高速微控制器可保护敏感信息,并保持支付系统的信任,以满足金融行业法规的要求。必要时,它会无条件地擦除私钥、程序和数据作为篡改响应,确保数据安全无虞。