20世纪80年代初,Intel公司推出了MCS-51单片机,随后Intel以专利转让的形式把8051内核发布给许多半导体厂家,从而出现了许多与MCS-51系统兼容的产品。这些产品与MCS-51的系统结构相同,采用CMOS工艺,因而常用80C51系列来指代所有具有8051指令系统的单片机。在80C51系列中,OC8051以架构清晰、取指带宽大、时钟效率高等诸多优点受到业内人士的青睐。本文在分析OpenCores网站提供的一款OC8051IP核的基础上,给出了一种仿真调试方案;利用该方案指出了其中若干逻辑错误并对其进行修改,最终完成了修改后IP核的FPGA下载测试。

1 OC8051结构分析

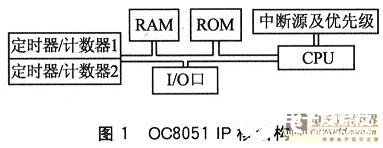

OpenCores网站提供的OC8051 IP核与8051的系统结构相同,如图1所示。该IP核兼容所有8051指令系统,内部资源包括:8位CPU,寻址能力达2×64K;4 KB的ROM和128字节的RAM;4个8位I/O口;16位内部定时/计数器;5个中断源和2个中断优先级。采用Verilog语言对其各个模块进行描述。系统主要模块及其功能说明如表1所列。不同模块对应的源文件均是以模块名称命名的,例如累加器A对应的源文件为oc8051_acc.v。

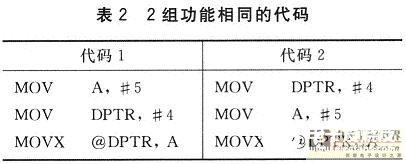

虽然上述OC8051 IP核宣称兼容所有8051指令系统,但是实际执行时并非如此。例如在执行表2所列的2组功能相同的代码时,所得到的执行结果并不相同。代码1的执行结果是将5写入地址为0的外部RAM,代码2的执行结果是将5写入地址为4的外部RAM。造成这种现象的原因是,oc8051_ext_addr_sel模块配置写外部RAM地址时延误了一个时钟周期。若要OC8051 IP核与标准8051系统一致,须对源文件中类似的逻辑错误进行修改。

2 OC805 1仿真调试及修改

对于硬件设计而言,仿真的作用是验证设计结果的逻辑功能是否符合初始规定,如果在这一层次上设计出了问题,那么以后各个层次的工作将完全不确定。由前文可知,OC8051 IP核存在着逻辑错误,所以有必要通过仿真的手段实现错误查找和定位,从而最终完成对逻辑错误的修改。

2.1 仿真调试方案

OC8051仿真调试方案如图2所示。其原理是:在Keil软件环境中编写测试程序,编译生成.hex文件并将其注入ROM的指令寄存器中。testbench负责产生OC8051工作时钟及控制使能等信号,并将OC8051执行ROM中指令的结果输出到文本/波形文件中。开发人员通过对文本/波形文件和Keil调试工具执行测试程序的结果进行比较,从而实现对逻辑错误的查找与定位,并对IP核源文件进行修改。

值得注意的是,虽然Modelsim功能强大,可以方便地观察到任何层次模块信号的变化,但是OC8051 IP核的结构和时序比较复杂,仍避免不了仿真时因为中间信号多所带来的不便。因此,在仿真调试时可寻求一些简化操作的机制。考虑到借助数据寄存器指针DPTR和累加器A,MOVX指令可以将程序执行过程中任何寄存器的值输出到外部RAM中,而观察外部RAM中的值相对容易,因而本文采用了这种机制。

2.2 具体修改方法

(1)oc805 1_ext_addr_sel模块

读写外部RAM地址可以由DPTR指示,也可以由Ri指示,该模块的主要功能是选择读写外部RAM地址。通过select和write信号完成对buff和state的配置,从而完成对读写外部RAM地址addr_out的配置。在Modelsim环境中,执行表1中的代码1时,发现addz_out的变化总是比DPTR慢一个时钟周期,因而其执行结果是将5写入地址为0的外部RAM。造成这种现象的原因是配置buff和state时采用了always进程,本文将该部分代码修改为:

assign state="write";

asstgn buff="select"?{8h00,ri}:{dptr_hi,dptr_lo};

(2)oc8051_psw模块

该模块由一个8位标志寄存器及其控制逻辑组成,用来收集指令执行后的有关状态。8位寄存器的各位状态通常是在指令执行过程中自动形成,但也可以由用户根据需要采用传送指令加以改变。原设计中负责解释传送指令的逻辑采用if语句:

if(addr[7:3]=='OC8051_SFR_B_ACC)data_out[addr[2:O]]<=cy_in;

'OC8051_SFR_B_ACC被定义为累加器A的高5位地址,用在这里显然不对。应该将其改为程序状态字PSW的高5位地址'OC8051_SFR_B_PSW。

(3)OC8051_alu模块

该模块是一个性能极强的运算器,不但可以进行四则运算和逻辑运算,而且具有数据传送、移位、程序转移等功能。其中,程序转移功能是当遇到短转移指令SJMlE’或变址转移指令JZ、CJNE、DJNZ等时,改变程序计数器PC的值,对应原设计为always进程中的'OC8051_ALU_PCS分支。其代码如下:

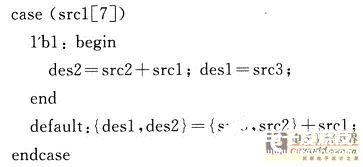

输入src3为PC[15:8],src2为PC[7;0],src1为目标转移地址rel。需要注意的是,rel是以立即数形式存在的,且为补码格式(补码数的加减法运算统一为加法运算)。若src1=1'b1成立,则rel为一负数,对应转移指令是往前转移;否则,往后转移。当rel为负数时,原设计仅考虑了:PC[7:0]≥| rel |的情况,其对目标地址{des1,des2}的处理不全面;当PC[7:0]

其中c是借位标志位,用来标识程序转移时PC[7:0]对PC[15:8]的影响。

(4)oc8051_decoder模块

该模块用于对指令译码。其设计思想是,分析当前输入信号op_in和所处状态state,把指令的功能配置为其他模块的控制信号,并得出下一个状态。因为各指令的指令周期不同,所以每条指令译码执行状态也各有不同。模块主体由状态机构成,在每个状态下对状态机不同的执行状态进行条件判断嵌套,以此实现对不同指令的多路选择。对模块仿真时发现,执行如DJNZ、JB、CLR等指令的结果不正确,其原因是在某些状态下对某些指令的译码有误,主要表现为配置了错误的控制信号。对模块修改结果如表3所列。

2.3 仿真结果

程序执行方式是单片机的基本工作方式,通常可以分为单步执行和连续执行两种。事实上,2.2小节中的具体修改方法正是结合这两种工作方式实现的。数据加密标准(DES)是著名的对称密钥分组密码,由美国标准FIPS 46-2定义。基于8051指令系统,DES的软件实现难度不大,但它是对OC8051 IP核工作能力的一次综合检验。采用DEs标准测试向量:

密钥K=1A624C89520DEC46

明文P=748502CD38451097

密文C=DD0CFEB783CF3FDE

结合图2所示的仿真调试方案,Modelsim环境中OC8051执行DES的仿真结果如图3所示。

3 基于FPGA的下载测试

利用FPGA对其功能进行了验证。选用Altera公司的EP2C35F672C6型号FPGA开发板,含有33 216个逻辑单元(LE)、丰富的存储器(RAM)和4个锁相环(PLL)。采用QuartusII软件,OC8051 IP核综合后占用3 917个逻辑单元,时钟频率最高达到30.81 MHz,FPGA测试的实际频率为27 MHz。

利用QuartusII对OC8051 IP核综合、布局布线后,采用JTAG方式将配置文件下载至FPGA中,测试程序仍采用DES算法程序。In-System Memory ContentEditor是QuartusII提供的一个可在线操作FPGA片上RAM内容的工具,通过JTAG方式,用户可以查看和修改RAM中的内容。如果用户设计对RAM中的内容进行了修改,需要查看修改后的结果是否为所期望的,则使用该工具最为方便。OC8051 IP核外部RAM中的数据可以通过该工具方便地操作,所以本文对DES测试向量的输入和输出都是通过它来完成的,如图4所示。

FPGA下载测试结果表明,OC8051工作正常,与仿真结果一样,测试程序运行正确。

结 语

本文介绍了一种OC8051 IP核的仿真测试方案。该方案给出了查找与定位IP核中逻辑错误的方法,并详细介绍了各种错误的修改方法。测试结果表明,OC8051工作正常,已经初步具备了微控制器的功能,可以被运用于实际的工程开发中。