现在,x86、Arm、RISC-V三分天下格局已定,RISC-V已经开始触及AI SoC、应用处理器,伴随RISC-V愈发向高性能计算发展,越来越多的新挑战开始浮现。

通常每家CPU Core IP公司提供多达几十种甚至上百种产品,但PPA(性能、功耗、面积)在不同应用中,最佳点都有所不同,下游用户—芯片设计公司,需要根据自己的产品场景找到自己最适用的PPA,并通过设计工作以实现CPU核,最终才能实现自身芯片的最大差异化。与之相悖的是,开发一款处理器,不仅要掌握许多CPU核设计的专业知识,还需要大量熟练掌握RTL语言的设计工程师。这是横亘在芯片设计公司面前的巨大门槛。

众所周知,RISC-V生态建设是现如今最难的事情,只有拥有更多RISC-V产品,才能更好铺开市场,扩大应用,从而扩充生态。因此,对高性能RISC-V的未来,定制计算和降低门槛是关键词。ICCAD 2023期间,Codasip(科达希普)分享了其在定制计算上的战略和最新产品。

Codasip是谁,有什么不一样?

“Codasip与其它RISC-V IP厂商不同的是,我们既提供RISC-V IP,也提供方便开发的设计工具Codasip Studio,”Codasip公司大中华区销售总经理胡征宇这样向EEWORLD介绍。

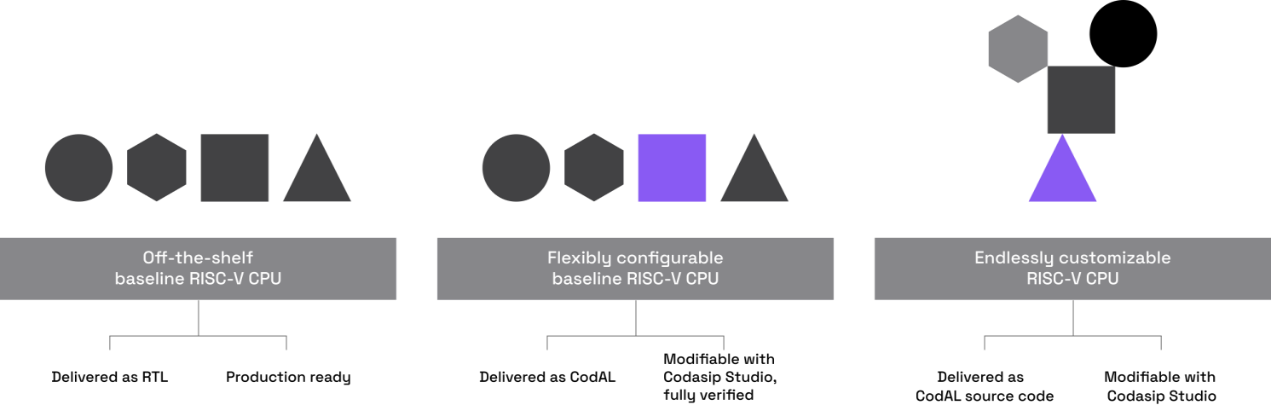

可以将这家公司的业务理解成提供“半定制化”解决方案,既可以为用户提供专业打造的基础性IP产品,也可以在IP的基础上,采用基于Eclipse行业标准环境和类似于C语言的架构描述语言,开启自己的定制化设计,从而让用户获得自己独一无二的定制处理器内核。

就像我们买衣服一样,会有两种极端模式:一种是完全通过流水线生产,这种模式生产的产品只能覆盖典型身高、体重等基本需求;另一种则是完全定制,这种产品可以精准到每个毫米,但这种情况,要么需要我们要花大价钱找人定制,要么自己包揽全部的设计和裁剪。但实际上在大多数情况下,我们只需要把流水线生产的产品,修剪下袖长,或者改改腰宽,就能得到一件最适合自己的衣服。

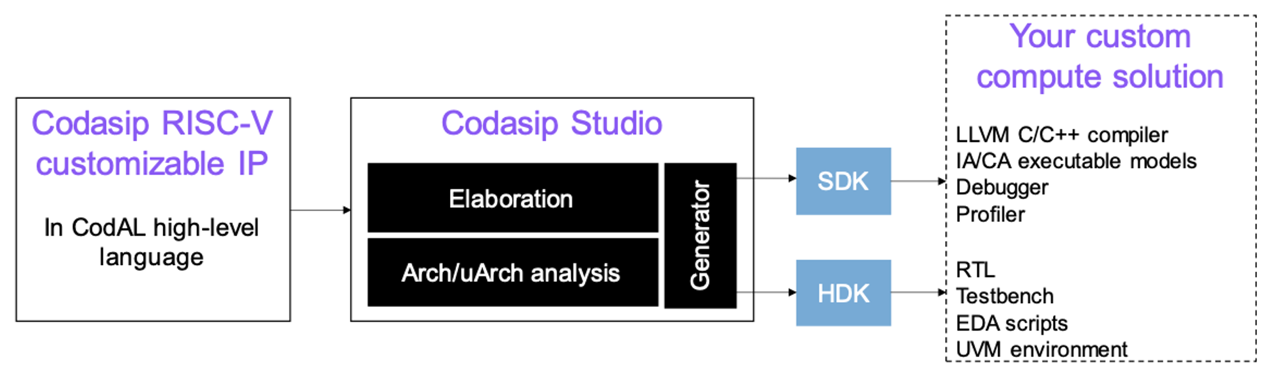

设计CPU核,通常需要掌握晦涩难懂的硬件设计语言,学习成本很高,这是芯片设计人才稀缺的原因之一。对芯片公司来说,掌握处理器设计的工程师的延聘成本也非常高。就CPU开发的传统方式而言,通常是由软件工程师团队负责软件开发工具包(SDK),硬件团队负责RTL设计,再有一个团队负责验证。这种传统方法在很多公司延续至今,但这种设计流程需要配备很多工程师,还要指挥他们协调工作,以让他们的步调一致。

Codasip看到的就是这样的市场需求,使用RISC-V核的芯片公司,不需要从头开始设计RISC-V处理器,可以在Codasip提供的现成可用且经过验证的示例基础上,根据自己的特定应用,找到适合自己特定场景的最佳处理器架构、指令集和PPA,同时以自动化的方式,生成SDK、RTL和验证工具,完成自身特有的RISC-V CPU核设计,用最高的效率推出独具特色的产品。

当然,标准的基准IP产品也经过了Codasip的精心设计,因而也会有将近一半的客户将这些产品作为标准产品而使用。毕竟,在设计衣服时,标品会考虑到大部分人的情况,不需要修改就会很合身。而另外一部分客户,则获得了架构许可和工具,可以根据他们独特的应用修改处理器内核。

这种独一无二的能力,为Codasip的销售提供了巨大动能。作为一家成立于2014年的公司,从成立至今,使用其IP和工具设计的CPU/DSP芯片的发货量已奔向30亿颗。与此同时,Codasip还是RISC-V国际组织的创始成员,以及基于LLVM和GNU的处理器解决方案的长期供应商。目前,Codasip总部位于德国慕尼黑,在捷克、法国和英国均设有设计中心。

PPA绝非固定的衡量标准

“PPA未必是绝对的唯一衡量标准,使用相同CPU IP核的不同客户,由于产品的应用场景不同,其对CPU IP核PPA的需求很有可能大不相同。打个比方,PPA是一个三角形,实际应用中客户需要的值会是三角形上某个点,但这个点未必就是CPU IP核厂商声称的‘最佳PPA值’那个点。Codasip的工具正是协助芯片设计客户,针对最适合自己应用需求的PPA值,更快更好地打造最适合自己的专有RISC-V IP核。” 胡征宇表示,Codasip提供了可定制的RISC-V 处理器IP核和EDA工具,而这些IP核和工具已经成为帮助客户实现最适合自身需求PPA的优化引擎。客户可以根据自己的应用调整和改进PPA,与基准(baseline)设计相比有机会获得成倍的性能提升。

Codasip公司大中华区总经理胡征宇

RISC-V非常吸引人的魅力之一就是指令集开源,芯片设计公司可以根据自己的特定需求优化内核设计。与此同时,RISC-V 指令集使用模块化设计,设计人员不仅可以添加任何标准扩展,还可以创建自己的自定义指令,同时保持完全的RISC-V兼容性。Codasip 可支持客户通过优化指令来实现降低功耗或提升性能等特定需求。

Codasip Studio使用独特的CodAL架构描述语言设计了所有内核。Codasip Studio可自动生成LLVM软件工具链,用于定制内核、RTL、测试平台和UVM验证环境。

Codasip Studio与CodAL的主要功能包括快速探索架构,自动生成自定义编译器,自动生成功耗和面积优化的、可合成以及可读的RTL。CodAL采用了类似于C语言的句法,从而使开发工程师不需要精通RTL机器语言就可以进行架构描述。

通过高级别语言来描述ISA并自动生成SDK,可以进行快速迭代实验以扩展指令集。这样,可以为专用指令处理器选择经过充分优化的ISA。与手动更改相比,自动生成SDK不仅更快,而且更不容易出错。这意味着,设计过程会变得更便宜、更可预测,从而避免不必要的风险和路线图中断。

64位RISC-V再添新成员

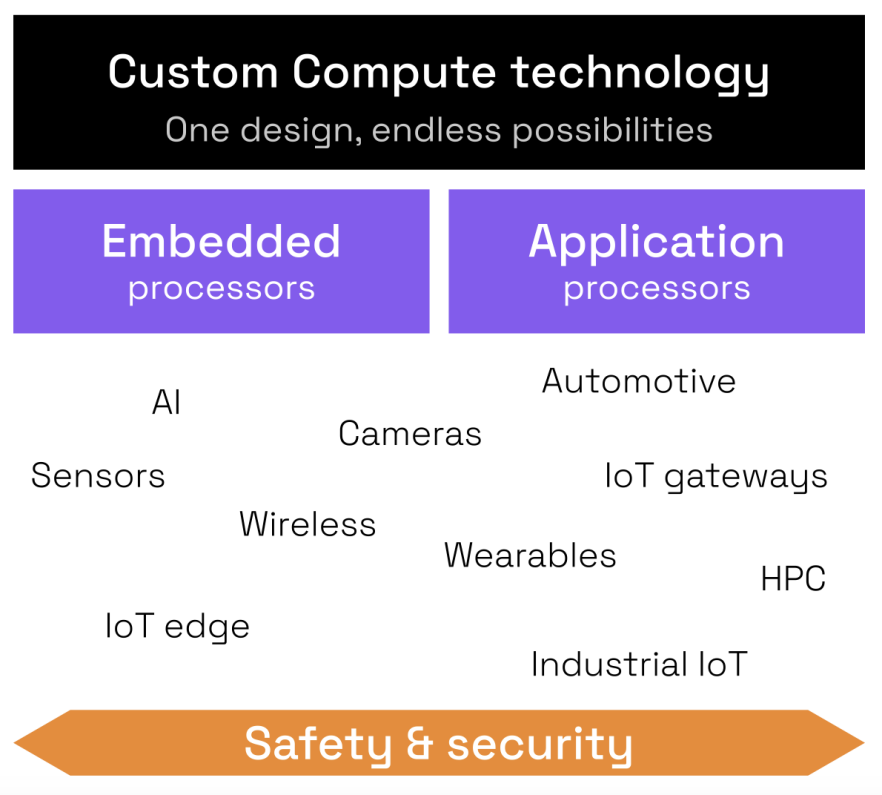

最近,Codasip推出支持RISC-V定制计算(Custom Compute)的700系列处理器。700系列相比过往产品拥有更高性能的基准内核,是对Codasip广受欢迎的嵌入式内核的补充。

该系列产品沿袭了Codasip高度灵活的特点,可以利用配置选项进行高级优化,或通过Codasip Studio快速高效地定制设计,为应用提供无限可能。

700系列处理器可以同时搭载嵌入式处理器内核(Embedded Processors)和应用处理器内核(Application Processors),可灵活调整以适用于不同场景应用,包括边缘、可穿戴设备、工业、自动驾驶、AI、HPC等各种场景。

该系列的首款处理器名为 A730,目前已经向部分客户交付,它是一款64位RISC-V应用处理内核。该处理器能够运行Linux,提供单核和多核配置,其配置选项使其性能比前几代提高了2 倍。

同时,为了充分发挥使用通用指令集的优势,Codasip的客户不仅可以选择使用Codasip A730,还可以使用任一700系列的未来成员,抑或是选择Codasip广受好评的 L31处理器内核。

官网显示,Codasip的产品组合分为两类处理器,32位的嵌入式处理器包括L11和L31,主要应用在不需要操作系统的裸机和RTOS应用上;64位的应用处理器包括A70和A730,主要是应用在上至四核高速缓存相干系统和Linux应用内。

“随着物联网应用越来越多,对定制芯片的需求正在不断上升。” 胡征宇向EEWORLD介绍,700系列不论是面对性能要求更高的64位应用处理计算,还是功耗要求更高的可穿戴设备,都可自如应对,客户可以非常方便地根据应用自行调整其处理器的架构和指令集来实现最佳PPA,这便是定制化的魅力所在。

胡征宇强调Codasip一直致力于推动RISC-V生态的发展和繁荣,自2021年以来,Codasip一直是中国RISC-V峰会的赞助商之一。Codasip非常期待见证来自中国的RISC-V技术进步和行业发展,并通过大学计划等多种方式与中国的RISC-V社区保持紧密联系,全力服务好现有和潜在的中国客户。