近些年,随着工艺不断演进,硅的工艺发展趋近于其物理瓶颈,晶体管再变小变得愈加困难:新一代GAAFET(Gate-All-Around,闸极环绕场效应晶体管)新技术使用更加立体和复杂的3D晶体管,因此难度更高。另一方面,制程越先进,生产技术与制造工序越复杂,制造成本呈指数级上升趋势。

本文引用地址:升级的两个永恒主题 —— 性能、体积/面积,而先进制程和先进的进步,均能够使得向着高性能和轻薄化前进。在摩尔定律失效之前,芯片系统性能的提升可以完全依赖于芯片本身制程提升,通过缩小单个晶体管特征尺寸,在同等芯片面积(Die size)水平下,提升晶体管集成度(同等设计框架,芯片性能/算力与晶体管数目正相关)。

但随着摩尔定律失效,芯片制程提升速度大大放缓,后摩尔时代到来,自然而然从先前“如何把芯片变得更小”的思维开始转变为“如何把芯片封得更小”,先进因能同时提高产品功能和降低成本是后摩尔时代的主流发展方向。

先进并不能改变单个晶体管尺寸,是从系统效率提升的角度提高芯片性能:一是让CPU更靠近Memory,让“算”更靠近“存”,提升每一次计算的算存效率;二是让单个芯片封装内集成更多的元件,因为元件在芯片内部的通讯效率比在板级上更高,可以从系统层面提升芯片性能。

何谓先进封装?

目前封装技术正在从传统封装(SOT、QFN、BGA等)向先进封装(FC、FIWLP、FOWLP、TSV、SIP等)转型。先进封装作为提高连接密度、提高系统集成度与小型化的重要方法,在单芯片向更高端制程推进难度大增时,担负起延续摩尔定律的重任。

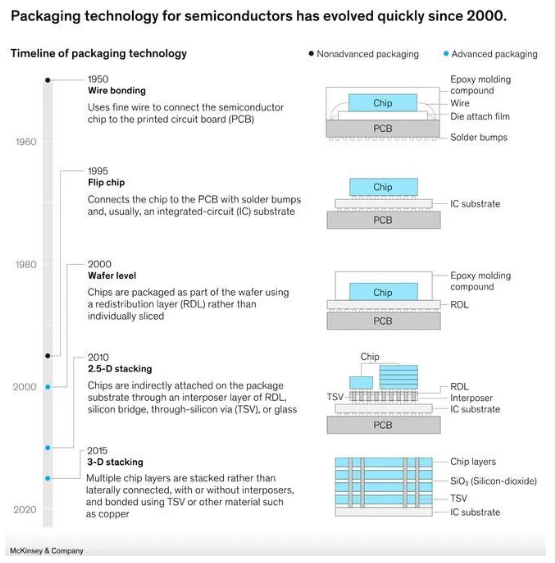

自20世纪90年代中期之后,集成电路封装体的外观(形状、引脚样式)并未发生重大变化,但其内部结构发生了三次重大技术革新:引线键合(Wire Bonding)、倒装封(Flip Chip)和晶圆级封装(WLCSP,Wafer Level Chip Scale Package)。

· 引线键合(Wire Bonding)技术开发于20世纪50年代,至今仍在使用,它是一种使用焊球和细金属线将印刷电路板(PCB)连接到芯片(包含集成电路的硅方块)的互连技术。它需要的空间比封装的芯片更少,还可以连接相对较远的点,但在高温、高湿和温度循环的情况下可能会失效,而每个键必须按顺序形成,这也增加了复杂性并减慢制造速度。

· 1995年,倒装芯片(Flip chip)是封装技术的第一次重大演变,使用了一个面朝下的芯片,其整个表面区域通过将PCB与芯片粘合的焊料“凸块”进行互连。倒装芯片封装是目前最常见、成本最低的技术,主要用于CPU、智能手机和射频系统封装解决方案。倒装芯片允许更小的装配,可以处理更高的温度,但必须安装在非常平整的表面上,同时也不容易更换。

· 2000年出现了晶圆级封装(WLCSP),是对整片晶圆进行封装测试后再切割得到单个成品芯片的技术,封装后的芯片尺寸与裸片一致。晶圆级封装和倒装芯片在芯片配置方面的最大区别在于,WLCSP的芯片和PCB之间没有基板,重新分布层(RDL)取代了基板,从而缩小了封装并增强了导热性。

晶圆级封装主要分为两种类型:扇入式(Fan-in)和扇出式(Fan-out)。扇入型利用RDL层将电信号向内扩展至芯片中心;扇出型则将电信号向外扩展至芯片外的区域,可连接更多引脚。

2010年堆叠式晶圆级封装得到了发展,它可以在同一封装中实现多个集成电路,被用于整合逻辑和存储芯片的异质结合,以及存储芯片堆叠。其中2.5D封装技术是通过中介层将不同芯片进行电路连接,电路连接效率更高、速度更快;而3D封装技术是直接实现硅片或者芯片之间的多层堆叠。

先进封装分为两个方向:

i. 小型化:3D封装突破传统的平面封装的概念,通过单个封装体内多次堆叠,实现了存储容量的倍增,进而提高芯片面积与封装面积的比值。

ii. 高集成:系统级封装SiP能将数字和非数字功能、硅和非硅材料、CMOS和非CMOS电路以及光电、MEMS、生物芯片等器件集成在一个封装内,在不单纯依赖工艺缩小的情况下,提高集成度,以实现终端电子产品的轻薄短小、低功耗等功能,同时降低厂商成本。

先进封装释放先进制程产能

在芯片短缺和地缘政治紧张的局势下,先进封装变得更加重要。2022年先进封装市场约占整个集成电路封装市场的48%,市场份额还在稳步提升。先进封装将成为全球封测市场的主要推动力和提升点,而且先进封装相较于传统封装具有更高的附加值。

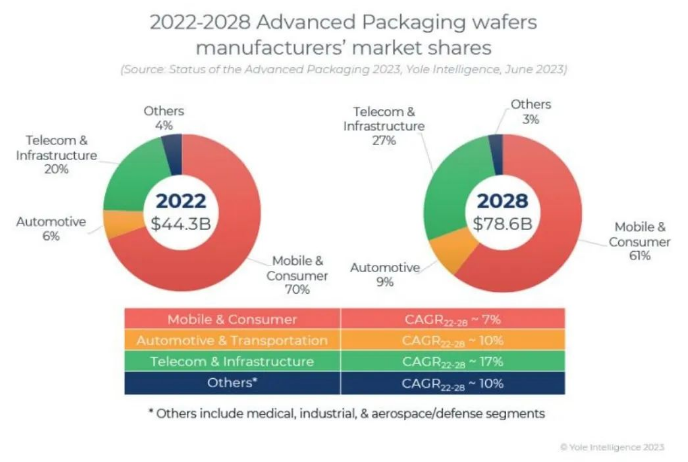

Yole Group最新的Advanced Packaging Market Monitor(先进封装市场监测)显示与上一年相比,2022年的先进封装收入为443亿美元,增长了约10%。预计2022-2028年复合年增长率(CAGR)为10.6%,到2028年达到786亿美元。相比之下,传统封装市场预计从2022-2028年的CAGR将放缓至3.2%,达到575亿美元。

尽管传统封装目前主导晶圆生产,到2022年将占总产量的近73%,但先进封装市场的份额正在逐渐增加。先进封装晶圆的市场份额预计将从2022年的约27%增长到2028年的32%。

随着运算需求的日益复杂,异构计算大行其道,更多不同类型的芯片需要被集成在一起,先进封装通过提升了芯片集成密度和互联速度的做法,大幅提升了相关产品的内存容量和数据传输速率。而在5G、自动驾驶汽车、物联网技术以及XR等领域,这些新兴的应用同样对先进封装需求十分旺盛。

从芯片结构来看,这类芯片需要满足高性能、小尺寸和低功耗等特性,因此需要实现更高密度的集成。相较于传统封装,先进封装尤其是3D封装在功能和性能上具有非常多的优势;另一方面,随着半导体应用愈发丰富,先进封装技术还需要承担一些辅助手段,为芯片设计公司提供思路,降低晶圆厂的制造门槛。

芯片面积越大工艺良率越低,在实际制造中得到的单颗芯片的制造成本就越高,同时在先进制程制造困难的背景下,通过芯片堆叠的方式,可以一定程度减少算力劣势。比如,通过14nm的两颗芯片堆叠,去达到同样晶体管数目的7nm芯片性能;通过多颗28nm的芯片堆叠,去达到14nm芯片性能。但是堆叠更多芯片,就意味着需要更大的IC载板、更多的Chiplet小芯片、更多的封装材料,导致功耗增大、体积/面积增加、成本的增加。

所以,此种堆叠方案在HPC(服务器、AI计算)、基站类大芯片领域更有适用价值,而对于消费电子领域如手机AP芯片和可穿戴芯片,在其应用场景对空间体积有严苛约束的条件下,芯片堆叠则较难施展。

先进封装可以释放一部分先进制程产能,使之用于更有急迫需求的场景。通过芯片堆叠,能够在体积空间限制、芯片成本以及功耗限制不敏感的使用场景下,减少对先进制程的依赖。让当下有限的先进制程产能,以更高的战略视角,应用在更需要先进工艺的应用需求中。

半导体大厂成为先进封装玩家

相比较于芯片设计以及芯片制造而言,芯片封装技术门槛较低,但这并不意味着先进封装技术更容易实现。拥有得天独厚优势的晶圆厂商们也“嗅”到了先进封装市场的机遇,纷纷开始大力布局先进封装领域,以、、为代表的晶圆厂商们,都在不断加大在先进封装领域的投资力度,频频推出在先进封装领域的创新技术。

2015年凭借InFO封装技术独揽了苹果的大单。在接下来的几年中,台积电也在先进封装领域不断发力,接连推出了CoWoS、SOIC 3D等技术,完善其在先进封装领域的布局。2020年台积电将其旗下SoIC、InFO及CoWoS等3D IC技术平台进行了整合,命名为3D Fabric,在产品设计方面3D Fabric提供了最大的弹性,整合逻辑Chiplet、高带宽内存(HBM)、特殊制程芯片。

最近台积电新开了一家3D Fabric封装厂Fab6,这是台积电首个一体式的先进封装测试工厂,该厂已准备好量产台积电SoIC封装技术。由于目前AI芯片订单的高需求,台积电的先进封装需求已经远大于现有产能。

作为台积电在晶圆代工领域的劲敌,竞争从制程扩展到了先进封装领域,在先进封装的布局三星也毫不示弱。按照三星先前公布的计划,其目标是在2027年将先进制程产能较2022年提升3倍以上,还专门成立了先进封装部门(AVP)。

尽管起步较晚,但三星近年来一直坚持不懈地更新异质封装技术,沿着水平集成和垂直集成两种方向,先后研发出三大先进封装技术:I-Cube、X-Cube和H-Cube。2018年,推出首款I-Cube2方案;2020年,推出X-Cube方案的3D堆叠设计;2021年11月,宣布已与Amkor联合开发出混合基板立方体(H-Cube)技术,这是三星最新的2.5D封装解决方案,大大降低了高性能计算等市场的准入门槛。

近年来,在先进工艺的研发方面频频遭遇“难产”,与台积电、三星逐渐拉开差距。因此,英特尔愈发看重先进封装的研发,开始不断发力先进封装技术。英特尔计划在2025年之前重返产业巅峰,将先进封装技术视为其重振旗鼓的关键。2021年12月,英特尔表示将投资70亿美元,以扩大其在马来西亚槟城的先进半导体封装工厂的生产能力。

英特尔主推的先进封装工艺有EMIB和Foveros。EMIB是2.5D硅中介层的替代方案,与传统2.5D封装的相比没有TSV,因此具有正常的封装良率、无需额外工艺和设计简单等优点;Foveros是高于EMIB的3D芯片堆叠技术,利用晶圆级封装能力,与EMIB封装方式相比,Foveros更适用于小尺寸产品或对内存带宽要求更高的产品。

先进封装将成为核心竞争力

由于先进工艺研发难度巨大,且研发成本投入巨大,因此一家晶圆制造厂不太可能有在性能、功耗、成本等领域全方位大幅领先于其他晶圆制造厂的情况,更多的是在不同的设计领域,不同的晶圆厂各有所长。同样,不同的厂商擅长不同领域的先进封装技术,例如台积电擅长高性能计算,三星擅长存储相关领域等。

值得注意的是,先进封装可能将改变半导体大厂在先进制程领域的竞争格局。因为先进制程芯片离不开先进封装技术,而且更关键的是先进封装技术将会和先进制程越来越紧密地结合,而掌握这些先进封装技术的也恰恰是台积电、三星和英特尔这样的先进制程晶圆制造厂,而不是第三方封测厂。

在未来,先进封装的重要性甚至不亚于先进制程的优化能力,未来的晶圆制造厂竞争力将会取决于半导体工艺和先进封装技术的综合实力。例如,目前台积电能获得英伟达H100 GPU订单的一个重要因素,就是因为台积电同时拥有最先进的4nm半导体制造工艺以及CoWoS先进封装技术。事实上,由于先进封装和先进制程供货商互相重合,代工大厂可以利用其在先进封装领域的优势来弥补在先进制程上的劣势来撬动市场。