多简单,无非就是读写擦,像我们这款nand数据位宽8bit,一个周期绰绰有余。但地址就不一样了,比如此款nandflash容量256M = 2^28,那么需要28根数据线来传输才能一个周期传输完,但这款nandflash的数据总线位宽只有8bit, 只有8根数据线,所以需要把地址拆分成多次发送,先发送col地址,再发送row地址,此款nandflash是用了5个周期发送地址。

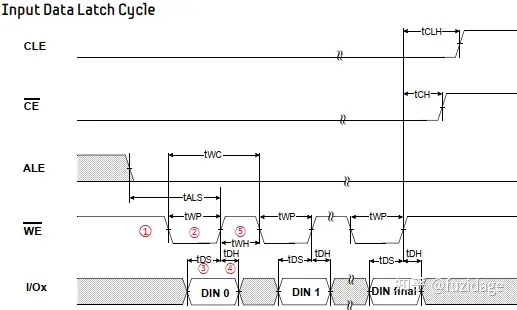

2.数据锁存时序(写数据)

从前面的命令地址锁存时序图中我们得知,CLE信号拉高,ALE信号拉低时,表示发送的命令;当CLE信号拉低,ALE信号拉高时,表示发送的地址;那么当CLE、ALE都拉低时,表示发送的数据,如下图,nCE, CLE, ALE都拉低了,表示传输的是数据。

1)当到达①时,nWE还是高电平,写使能没有开启;

2)当到达②,③时,那么经过了tWP时间(TDS时间),数据开始被锁存;

3)到达④,经过tDH时间,数据锁存完成;

4)到达⑤,也就是数据开始锁存后再过了tWH时间后释放nWE信号;

5)重复②③④⑤过程。

根据上面这三个图(手册上的命令、地址、数据锁存时序图),下面详细解释各个时间参数的含义:

3.顺序访问周期(读数据)

1)①处,表示要过tRR后才能发送读使能信号nRE进行访问(上一次的访问结束后,需要等待ready状态稳定后才可以进行下一次访问);

2)当到达②,需要经过rREA时间后nRE信号才有效(待nRE稳定);

3)当到达③,DATA总线上的读取被读取;

4)当到达④,nRE释放tREH时间后才允许下一次读使能

我们看到连续顺序访问时,单次访问的时间为tRC,那么这些时间参数的值也可以从K9F2G08U0C datasheet中找到:为25ns