2024年3月26日,(STMicroelectronics,简称ST)宣布了基于 18 纳米全耗尽绝缘体上硅() 技术并整合嵌入式相变存储器 (ePCM)的先进制造工艺,支持下一代嵌入式处理器升级进化,并将此技术应用在通用32位市场领先的系列产品。作为技术的主要贡献者,这次联合三星晶圆代工厂共同开发新技术,助力嵌入式处理应用的性能和功耗实现巨大飞跃,同时可以集成容量更大的存储器和更多的模拟和数字外设。据悉,基于新技术的下一代 中端微控制器的首款产品将于 2024下半年开始向部分客户提供样片,2025 年下半年排产。

作为同为胡正明团队研发的技术,平面的和3D的FINFET各有特点,传统的美系半导体厂商选择了FINFET提升集成电路密度,为了寻求差异化道路,以为主的欧洲公司则尝试FD-SOI技术以寻求差异化竞争之路。由于其高性能、低功耗、高集成度和良好的热稳定性,FDSOI在移动设备、物联网和人工智能等领域具有广泛的应用前景。此次ST将FD-SOI率先引入领域,很重要的一个原因得益于ST在FD-SOI技术上拥有丰富的设计开发经验。ST于2012年推出了28纳米FD-SOI的手机AP产品,该工艺来自于ST自有的Crolles II–300mm晶圆厂。与ST Micro的28纳米体工艺相比,28纳米FD-SOI工艺的性能提高了32%-84%,当年基于该技术的那颗ST-Ericsson的AP相比其他同期产品性能提升高达20%以上。

在FDSOI的产业链条中,ST拥有足够的话语权和产品经验

那么这次将FD-SOI技术带入MCU又将给系列MCU带来哪些优势呢?按照ST官方的解读,与目前在用的 ST 40nm 嵌入式非易失性存储器 (eNVM) 技术相比,集成 ePCM 的18nm FD-SOI制造工艺极大地提高了关键的品质因数:

· 性能功耗比提高 50% 以上;

· 非易失性存储器 (NVM)密度是现有技术的2.5 倍,可以在片上集成容量更大的存储器;

· 数字电路密度是现有技术的三倍,可以集成人工智能、图形加速器等数字外设,以及最先进的安全保护功能;

· 噪声系数改善 3dB,增强了无线 MCU 的射频性能。

该技术的工作电源电压是3V,可以给电源管理、复位系统、时钟源和数字/模拟转换器等模拟功能供电,是20 纳米以下唯一支持此功能的半导体工艺技术。该技术的耐高温工作、辐射硬化和数据保存期限已经过汽车市场的检验,能够满足工业应用对可靠性的严格要求。

基于以上官方的解读,我们大胆对ST选择将FDSOI引入MCU的理由进行一些自己的分析理解。

最直接的原因就是技术优势,众所周知半导体工艺每前进一代性能都会有所提升。如果按密度来算,目前ST所采用的40nm算是45nm的半代工艺节点,而最先进的28nm工艺是32nm工艺的半代节点,两者恰好相差一代。目前从45到28是主流MCU最常见的工艺节点,一方面是技术非常成熟制造成本比较低,另一方面是性能比较稳定适合SoC的多单元集成。而18nm理论上是22nm的半代节点,相比于28nm又前进了一代,从工艺上说要比现在的40nm提升了两代,无论是密度还是功耗都会有明显的提升。如果能把成本控制好,2代工艺差带来的性能和功耗优势无疑是显而易见的。虽然这次是和三星共同开发的技术,但ST在整个FDSOI产业链的重要性几乎是无可取代的,而目前ST拥有在产量最大的FDSOI芯片,现在加上目前几乎年出货量接近20亿颗的STM32系列,即使只有五分之一的STM32未来转向采用18nm的FDSOI,这种级别的产能足够填满一条300mm晶圆线。我认为,ST是经过了详细的评估才会决定迈出这一步的,毕竟平面工艺的成本提升要比采用3D工艺小很多,因此成本方面带来的提升应该足够被性能和功耗方面的优势抹平。毕竟按照ST官方公告,新工艺的性能功耗比可以提升50%,这个优势带来的市场影响力有多震撼可想而知。

第二个原因是差异化和无奈的选择。由于大部分代工厂追求先进工艺,因此传统平面工艺几乎到了28nm就截止了,再继续深入到22或者14这些节点主流采用的都是FINFET工艺。MCU因为其特殊性和成本压力,短期内是无法支撑起FINFET的高价格和对模拟与存储单元的排斥性。从制程工艺成本和分布来看,FD-SOI可能是MCU工艺前进到1xnm级别无奈的选择。我相信当2021年STM32即将登顶32位通用MCU市场份额之际,ST就已经开始布局如何在差异化并不明显的Arm核MCU市场中寻找全新的差异化手段了,而选择自己最擅长的FD-SOI进军1xnm级别工艺,这看似无奈的选择反而可能会更加巩固STM32在MCU市场的优势,毕竟身后几个竞争对手短期内可能没有如此成熟的应对FDSOI的经验。

第三个原因应该说符合MCU发展的客观趋势。随着MCU内核性能不断提升,在中高端MCU市场的差异化和主流发展趋势就是更大的存储容量和更多的模拟功能外设集成,特别是对集成无线功能的MCU来说简直是如虎添翼。恰好FD-SOI技术一个特点就是拥有更好地模拟和射频技术亲和力,并且在ST的官方介绍中,eNVM到ePCM的进化能大幅提升片上存储的容量,这会再次提升STM32 MCU的竞争力,以及在部分需要配合模拟功能的场合拥有更好的先天优势,比如电机控制系统、数字电源和安全系统。另一个关键点是,FDSOI工艺在抗高温和抗辐射方面也有出色表现,毫无疑问会增加STM32系列在苛刻的工业应用甚至汽车和航空航天应用的竞争优势,对刚刚将汽车微控制器和通用微控制器部门合并的ST来说未来FDSOI应用于汽车MCU并不遥远。当然,能够集成更多片上存储空间的消息可能对跟ST直面竞争的国内MCU老大并不友好,毕竟这家国内巨头一个竞争优势就是在存储容量方面拥有不小的领先。

如果说STM32系列的成功是借Arm核MCU生态优势的东风乘势而起,那么站稳市场老大地位并且刚刚合并了通用和汽车MCU的ST下一步要巩固市场优势就必须要寻求差异化,从而继续巩固并扩大自己的市场领先优势,目前看ST给出了一个最值得市场震撼的选择,这个选择短期内甚至让其竞争对手都很难跟进。既然ST可以用40nm工艺将M0+内核的功耗做到14nA级别,那么我们是否可以期待18nm工艺的STM32再次刷新32位MCU的各种数据极限呢?

FDSOI适合更多的集成和模拟、功率应用

附录

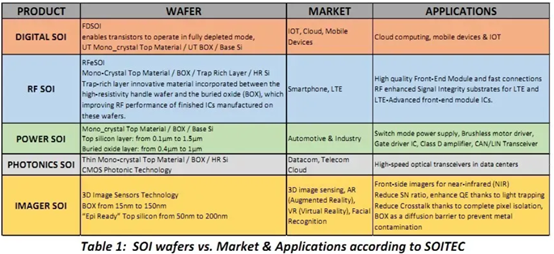

FDSOI技术简介

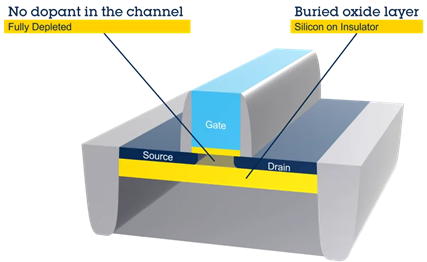

FD-SOI是一种平面工艺技术,依赖于两项主要创新。首先,在基底硅的顶部放置一层超薄绝缘体,称为掩埋式氧化物。接着,通过超薄的硅膜实现晶体管沟道。由于其厚度超薄,无需掺杂沟道,即可使晶体管完全耗尽。这两项创新的结合被称为“超薄体和掩埋式氧化物全耗尽型SOI”或UTBB-FD-SOI。

图FD-SOI结构示意图(来源意法半导体官网)

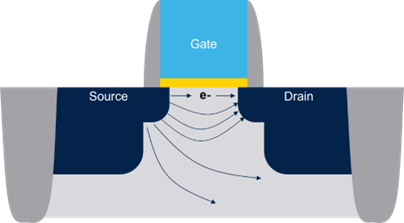

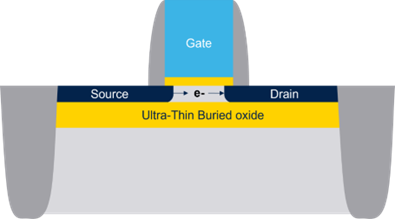

和体硅技术相比,FD-SOI可以实现对纳米节点工艺制程下晶体管电流的有效控制和阈值电压的灵活调控。FD-SOI通过构造实现了比传统bulk技术更好的晶体管静电特性。掩埋式氧化物层降低了源极和漏极之间的寄生电容,并且有效地限制了从源极流向漏极的电子,显著降低了性能下降的漏电流。

BULK

FD-SOI

图BULK和FD-SOI对比示意(图源意法半导体官网)

FD-SOI能实现有效的晶体管控制

在bulk技术中,由于寄生电流泄漏和晶体管几何尺寸缩减会降低效率,体偏置非常有限。全赖FD-SOI中的晶体管结构及其超薄绝缘体层,偏置效率得到了显著的提升。此外,掩埋式氧化物的存在使偏置电压得以进一步增强,从而形成了对晶体管的突破性动态控制。当基板的极化为正时,即正向体偏置 (FBB),此时可以加快晶体管的切换速度。由此提供了一种能够优化性能和功耗的强大技术。易于实现的FBB可在晶体管操作期间动态调制,为设计者带来极大的灵活性,从而能在需要时更快地设计电路,并在性能要求较低的场景中实现节能。

无论任何级别,均能高效表现

模拟和射频设计的优势

FD-SOI为模拟设计带来诸多优点。通道的总介电隔离允许较低的栅极电容和漏电流,以及闩锁抗扰性。此外,与bulk技术相比,全耗尽型晶体管中不存在沟道掺杂和口袋型离子注入,因此产生的噪声更低,且增益更高(高达+15dB)。

最终,这些特性都将转化为更小巧、更简单的模拟电路,在更低的工作功率下具有更高的性能。

卓越的功率效率

FD-SOI中改进的静电特性和介质隔离带来了两大主要优势。首先,可在低电压下维持具有竞争力的运行速度。其次能实现更有效的体偏置,提供对通道的深度控制,并能优化被动和动态功耗

辐射抗扰度

由于其超薄的机身和掩埋式氧化物,FD-SOI技术凭借其构造,能够有效应对辐照错误(如位翻转或锁存),为高性能的片上系统带来额外的可靠性,同时节省了面积(如简化SRAM的ECC策略)。

除了FD-SOI技术的固有优势外,20多年来,意法半导体一直在开发一整套用于 设计抗辐照电路的技术。我们在辐照建模、设计和测试方面积累了丰富的专业知识,能帮助客户针对安全、 汽车ADAS、航天、工业、医疗和网络等高要求细分市场提供准抗扰电路。

存储器优势

FD-SOI与意法半导体获得专利的“单孔”位单元架构相结合,极大地提高了SRAM存储器性能,能够在低电压和极低泄漏下运行,同时保持与传统bulk SRAM相似的读/写速度。

相关文章

技术咨询

技术咨询 代买器件

代买器件 商务客服

商务客服 研发客服

研发客服