基于C8051单片机和FPGA实现导纳测量仪的系统设计

虚拟仪器的广泛应用,使得用户可以根据需求,设计自己的仪器系统。无源网络导纳测量仪即是虚拟仪器设计思想的一种具体运用,旨在实现对端口网络的导纳进行自动测量。测量仪是以C8051单片机为控制和处理核心,采用可编程逻辑器件EPF10K10,根据DDS原理产生信号源,将信号源连接到待测的网络上,对网络两端的电压和电流进行差分放大,使其输出电压尽可能达到ADC的最大输入电压,然后进行A/D采样,采样时,频率随信号频率而改变,一个周期内固定采32个点,用单片机的P1、P2直接接收数据,边采样边接收。对采样所得的电流、电压数据进行快速傅立叶变换(FFT),并分别求出其模值和相位,则导纳的模值为电流模值与电压模值之比,相位为电流与电压的相位之差。实验证实,导纳测量仪可根据不同的被测对象,选择合适量程,可步进改变信号频率(频率呵由键盘直接键入),实现精确测量。

系统功能与指标

1.制作正弦波信号发生器,技术指标如下:

a、能产生100Hz、:300Hz、1kHz、3kHz、10kHz频率,频率误差的绝对值小于所要求频率的1%:

b、输出电压峰-峰值为1V,输出电压误差的绝对值小于20mV;

c、输出电阻小于1Ω,输出波形无明显失真。

2.实现端口网络N0的电导Re[Y]、电纳Im[Y]、导纳模|Y| 和导纳角φY的测量电路,技术指标如下:

a、电导Re[Y]的测量范围为0.1mS~10mS,分为若干量程,测量误差的绝对值小于

理论计算值的10%;

b、电纳Im[Y]的测量范围为0.1ms~10ms,分为若干量程,测量误差的绝对值小于理论计算值的10%:

c、导纳模|Y|测量误差的绝对值小于理论计算值的10%;

d、导纳角φY的测量范围为±90°,测量误差的绝对值小于理论计算值的5%。

发挥部分

1.将Re[Y]和Im[Y]的测量范围扩展到0.01mS~100mS,测量误差要求不变。

2.自动测量功能

a、正弦波信号发生器的

频率可以从100Hz开始,以100Hz的步进增加,最后到达10kHz结束;

b、能在上述各频率点对网络的Re[Y]和Im[Y](或|Y|和φY)进行连续的测量、存储和回放显示,其中,Re[Y]和Im[Y](或|Y|)的测量具有量程自动转换功能;

c、能分别显示上述4个参数的频率特性曲线。

系统方案设计与实现

本系统利用FPGA芯片制作正弦波信号源V(t)=Vmcos2πft,通过电压测量电路和电流测量电路,输入端口网络,分别对端口两端的电压V(t)=Vmcos2πft和电流i(t)=Imcos(2πft+φ)进行采样,将采样数据存入存储器。然后对采样所得的电压V(n)和电流i(n)数据进行 幅值判断,根据电压、电流的幅度值V(n)max、i(n)max来确定相应的测量量程;对采样数据进行快速傅立叶变换,得出采样电压和电流的幅度谱和相位谱,计算对应频率处的电压模值|V|和相位φv,及电流的模值|I|和相位φi,则电流模值与电压模值之比|I|/|V|即为被测网络的导纳模值|Y|,电流与电压的相位之差 φi-φv为网络导纳的相位φY。自动改变信号源的输出信号频率f,分别计算不同频率的网络导纳值,可绘出网络导纳随频率的变化曲线。实现原理如图1所示。

正弦信号发生器设计

正弦信号产生采用DDS技术,以FGPA方式实现,DDS的基本结构由参考时钟、相位累加器、存储器(ROM)、DAC和滤波器(LPF)组成,其组成如图2所示。

在用FPGA设计DDS电路的时候,相位累加器是决定DDS电路性能的关键部分,设计中采用相位累加器,通过进位链和流水线技术相结合的办法来实现,这样既能保证较高的资源利用率,又能大幅提高系统的性能和速度。

相位/幅度转换电路是DDS电路中的另一个关键部分,设计中面临的主要问题就是资源的开销。该电路通常采用ROM结构,相位累加器的输出是一种数字式锯齿波,通过取它的若干位作为ROM的地址输入,而后通过查表和运算,ROM就能输出所需波形的量化数据。

在FPGA(针对Altera公司的器件)中,ROM一般由EAB实现,并且ROM表的尺寸随着地址位数或数据位数的增加成指数递增关系,因此,在满足信号性能的前提条件下,如何减少资源的开销就是一个重要的问题。在实际设计时充分利用了信号周期内的对称性和算术关系来减少EAB的开销。

基于FPGA的DDS技术可以实现频率范围为1kHz~1MHz、频率稳定度优于10-4的要求,且容易实现频率步进100Hz的功能。在其外围电路设计中利用LF356接成射随器,可以保证输出电阻小于1Ω,满足设计要求,同时通过调节电位器可改变正弦波信号的峰峰值,便于系统调试。

数据采集系统设计

数据采集系统选用两个ADC,在A/D采样的时候,单片机同时进行数据的接收和存储。

ADC选用TLC5510,其采样速率为20MSPS,在满足要求指标的同时,无须增加外围存储器。

在数据存储过程中,假设采集点数为16,对于最高频率10kHz来讲,采样频率则为160kHz,采样周期即为1/(160×106)=6μs,而C8051F020的系统时钟频率为24MHz,为单指令周期,则系统时钟为1/24×106=50ns,其70%的指令是在1~2个系统时钟内完成,这里假设为两个系统时钟,考虑到存数过程为寻址存储,大约耗费10个系统时钟,对应时间为50×10=500ns=0.5μs,完全可以跟得上TLC5510的转换速度。经测试,指令执行时间为1.5μs,可以在一个周期内采样32个点,因此无需增加外围存储器,充分利用现有单片机资源,简化电路。

自动量程转换系统设计

由于所测量的网络不同,对应的采样电阻也需进行适当调整,才能保证采样的准确性,系统必须具有自动量程转换功能。采用继电器并接若干电阻,通过单片机控制继电器的通断达到量程转换的目的。

量程确定过程如下:

就电流采样电路而言,TLC5510驱动电压为750mV~250mV,则须保证电流采样电压必须在此范围内,方可保证采样的准确(考虑指标输出电压峰-峰值为1V,输出电压误差的绝对值小于20mV),故有:

3/4 》 Vi 》 1/4 (1-1)

而Vi = Rs/(Rs+Z),故有:

3/4 》 Rs/(Rs+Z) 》 l/4 (1-2)

简化可得下式:

3 Rs》 Z 》 Rs/3 (1-3)

考虑指标要保证电导Re[Y]的测量范围为0.1mS~10mS,故Z在100Ω~10KΩ范围内,对应如下量程:

第一档:Rs=30Ω,可以测量: 90Ω 》 Z 》10Ω;

第二档:Rs=270Ω,可以测量: 810Ω 》 Z 》 90Ω;

第三档:Rs=2.430KΩ,可以测量: 7.290KΩ 》 Z 》 810Ω;

第四档:Rs=21.870KΩ,可以测量: 65.610KΩ 》 Z 》 7.290 KΩ;

第五档:Rs=196.830KΩ,可以测量: 100KΩ 》 Z 》 65.610 KΩ。

量程判断标准如下(采样后电压峰值为max_v_c,采样后电流峰值为max_j_c):

如果max_v_c》3 max_i_c,则档位应自动掷低;

如果max_v_c

其他情况即设在当前正常量程,不改变档位。实际调试中,采用此档位划分,取得比较满意的测量结果。

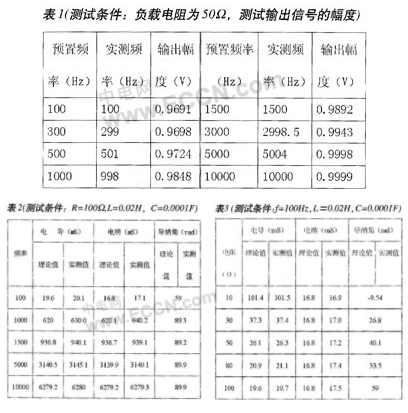

单片机控制

导纳测量仪是以C8051单片机为控制和处理核心,基于VC编程,主要实现电流、电压采样数据的存储,对存储数据进行FFT运算,获得导纳模值、相位值,同时进行自动量程判断;实现扫频功能,同时存储扫频数据,显示测量结果和波形等。各项参数的试验结果如表1、表2和表3所示。

结语

设计中充分利用了单片机和FPGA的强大功能,用软件代替了大量的硬件,简化了系统的安装和调试,采用多点FFT,使测量精度更高。测试各项指标均达到或高于设计要求。如果条件允许,外围电路可制成印刷电路板,放大器可以选用性能更高但相对昂贵的芯片,如AD620,进一步减小误差,提高测量精度。

系统在实现上述功能的同时,借助RS-232实现了系统与PC的通信,以VC实现虚拟的图形化界面,可在PC上实时显示网络导纳值以及其他相关的测量指标。

本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。