1. 引言

本文引用地址:Field Programmable GateArray(简称,)于1985年由XILINX创始人之一Ross Freeman发明,第一颗芯片XC2064为XILINX所发明,一经发明,后续的发展速度之快,超出大多数人的想象,近些年的FPGA,始终引领先进的工艺。在通信等领域FPGA有着广泛的应用,通信领域需要高速的通信协议处理方式,另一方面通信协议随时都在修改,不适合做成专门的芯片,所以能够灵活改变的功能的FPGA就成了首选。并行和可编程是FPGA最大的优势。

2.核心板设计

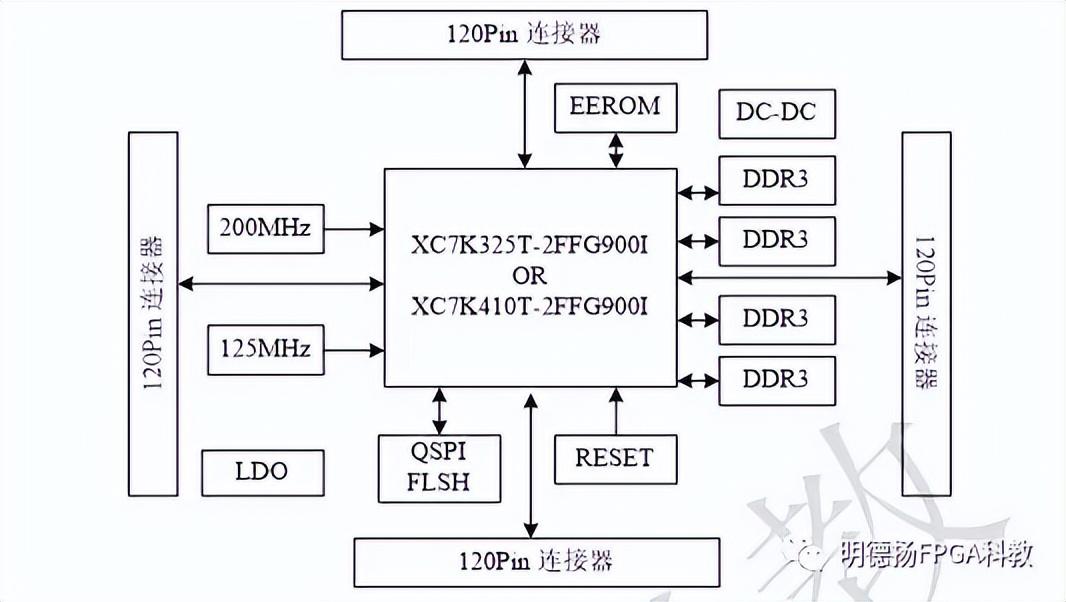

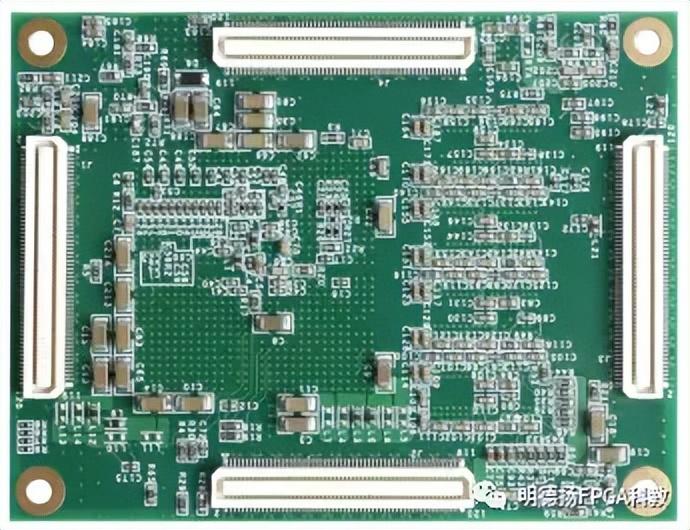

今天分享的核心板是明德扬公司研发的K7核心板,命名为MP5650。采用XILINX 系列的XC7K325T-2FFG900I/XC7K410T-2FFG900I作为主控制器,在FPGA 芯片的HP 端口上挂载了4片DDR3存储芯片,每片DDR3 容量高达512M 字节,每片16bit组成64bit 位的数据位宽。1片128Mb 的QSPI FLASH 芯片用来静态存储FPGA 芯片的配置文件或者其它用户数据。核心板采用4个0.5mm间距120Pin 镀金连接器与底板连接,核心板四个脚放置了4个3.5mm固定孔,此孔可以与底板通过螺丝紧固,确保了在强烈震动的环境下稳定运行。核心板结构尺寸为65(mm)× 85(mm)。整个开发系统的结构如图1所示,实物图如图2所示。该板很适合高速数据通信;视频采集、视频输出、消费电子;机器视觉、工业控制;项目研发前期验证;电子信息工程、自动化、通信工程等电子类相关专业开发人员学习等领域及人群。

图1 核心板结构图

图2 核心板实物图

2.1主要

2.1.1 FPGA芯片选择

核心板使用的是Xilinx公司的KINTEX-7 FPGA芯片,芯片型号为XC7K325T-2FFG900I/XC7K410T-2FFG900I,二者除片上资源不同外,管脚完全兼容。速度等级为2,温度等级为工业级。此型号为FFG900封装,900个引脚,引脚间距为1.0mm。

2.1.2 DDR3 SDRAM

板上配有四片Alliance Memory 的256MB的DDR3芯片,型号为AS4C256M16D3B-12BCN (兼容MT41J256M16XX-125)。每片DDR3 SDRAM数据位宽为16bit,共组成64bit的数据总线宽度。因为4片DDR3芯片连接到FPGA的HP口,DDR3 SDRAM的最高运行速度可达800MHz(数据速率1600Mbps),四片DDR3存储系统直接连接到了FPGA的BANK32, BANK33,BANK34的接口上。核心板采用高速布线,DDR3 的硬件设计需要严格考虑信号完整性,开发板的电路及PCB 设计已经充分考虑了匹配电阻/终端电阻,走线阻抗控制,走线等长控制,以确保DDR3 稳定工作。

2.1.3 QSPI Flash

板上配有一片128Mbit大小的Quad-SPI Flash芯片,型号为N25Q128,它使用3.3V CMOS电压标准。由于QSPI FLASH的非易失特性,在使用中,它可以存储FPGA的配置Bin文件以及其它的用户数据文件。

2.1.4 核心板时钟

核心板上为了准确适配不同用途的时钟频率,板载多个时钟源。其中包括200MHz的系统差分时钟源SiT9102差分晶振,还包括125MHz的GTX差分时钟源SiT9102差分晶振。SiT9102是一款高精度、超低相噪的晶振,非常适合作为高速信号处理系统的时钟源最后,为了缩短大容量FPGA芯片的下载配置时间,板卡还配有66MHz的EMCCLK,用户可以配置使用该时钟,配合QSPI×4模式,从而大大提高FPGA的配置效率。

2.1.5 核心板电源

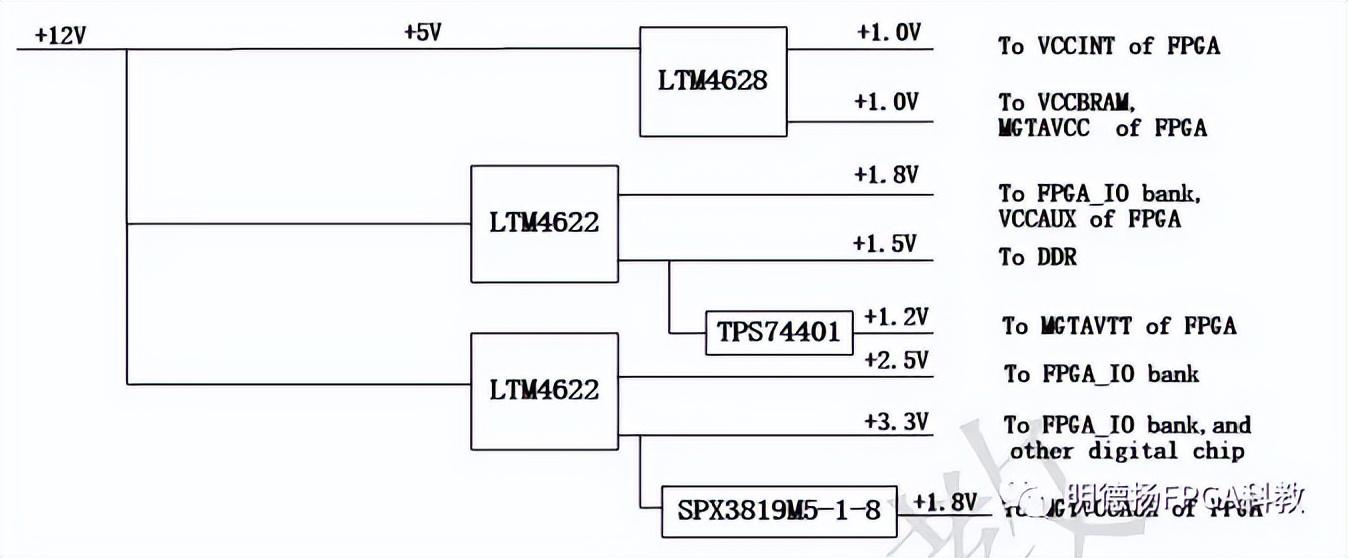

核心板集成电源管理,+5—+12V电源输入通过TI 电源芯片LTM4628 产生两路 1.0V 的电源,其中一路为FPGA的核心提供稳定的电源,另一路为GTX的MGTAVCC提供稳定的电源,LTM4628输出电流高达8A,满足FPGA电流需求。+5—+12V电源输入通过TI 电源芯片LTM4622分别产生+1.5V、+1.8V、+2.5V、+3.3V电压,单片LTM4622有两路电源输出,所以需要2片LTM4622。LTM4622为VCCAUX、VCCIO、DRR3、晶振、FLASH等供电。+1.5V电压经过TPS74401RGWT转换为1.2V直流,为MGTAVTT提供1.2V的电压。+3.3V 电压经过SPX3819M5-1-8转换为1.8V直流,为MGTVCCAUX提供1.8V的电压。按XILINX官方手册提供的上电顺序依次上电,官方上电时序要求如图3所示。核心板供电架构如图4所示。

图3 FPGA上电顺序

图4核心板供电框图

3.总结

通过以上描述,我们能够清晰看到这个核心板所含有的接口和功能。这款核心板的4个板对板连接器扩展出了276个IO,其中BANK12、BANK13、BANK15、BANK16、BANK17、BANK18的全部IO的电平可以通过更换核心板上的磁珠来修改,满足用户对+3.3V、+2.5V、+1.5V电平接口的需求;另外核心板也扩展出了16对高速收发器GTX接口。对于需要大量IO的用户,此核心板将是不错的选择。而且IO连接部分,同一个BANK管脚到连接器接口之间走线做了等长和差分处理,对于二次开发来说,非常适合。