前言

使用过51单片机的朋友会清楚:51单片机在烧写程序的时候需要断一下电再上电;使用过STM32单片机的朋友会清楚:烧写程序时需要设置Boot模式。ESP8266在烧写程序时也需要手动设置模式,STM32的ISP自动下载电路都有了,那么ESP8266有没有自动下载电路呢?答案是有的。下面来分析。

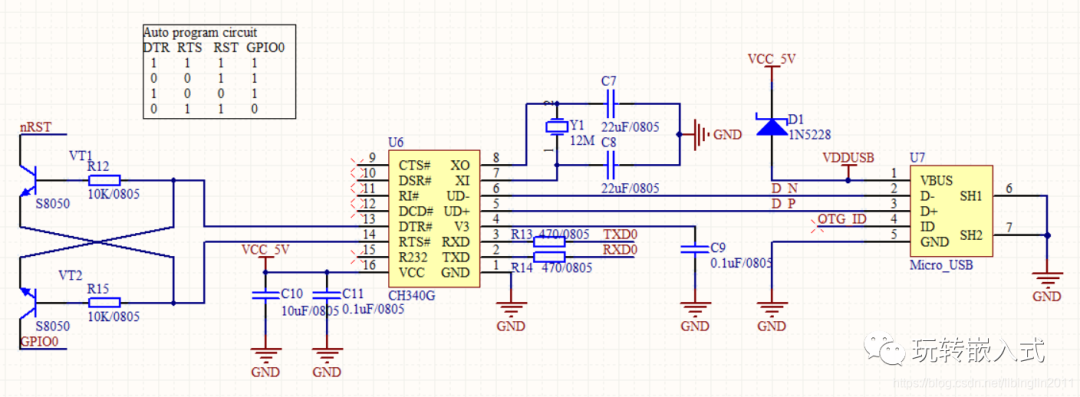

自动下载电路设计

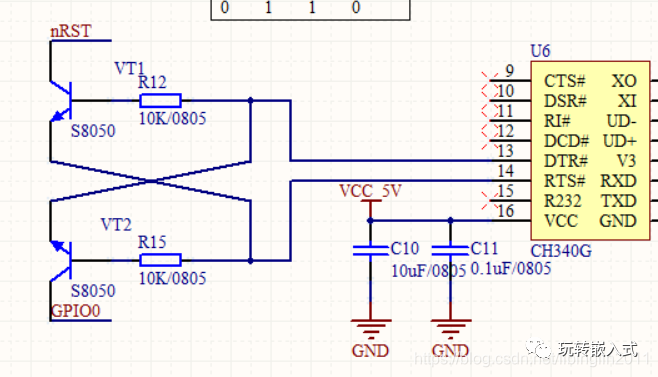

ESP8266下载过程中发现每次都需要去设置GPIO0的状态,如何实现自动给实现GPIO0电平状态的切换呢?看下面的电路。

可以看到这个下载电路相对于普通的CH340G下载电路,这个电路是把CH340G芯片中的DTR和RTS引脚引出到两个S8050的三极管上,去控制nRST和GPIO0的电平。

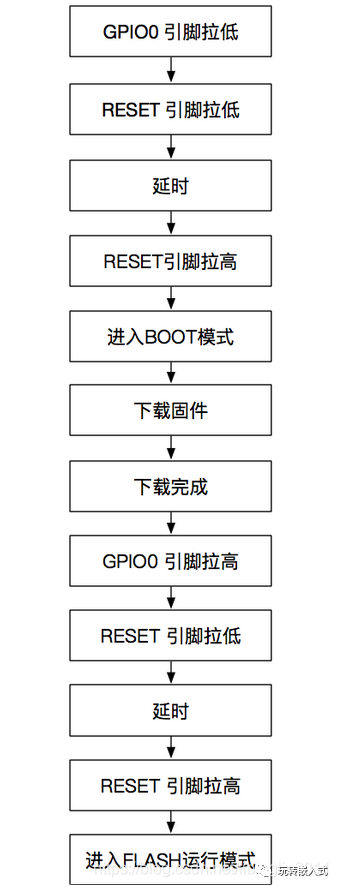

ESP8266下载模式

根据ESP8266芯片资料要求的下载流程,必须在GPIO0为低电平的状态下,复位芯片,才会进入USART下载模式。

我们看看该自动下载电路是怎么实现这个流程时序的,首先我们还是得从核心器件CH340G分析入手。

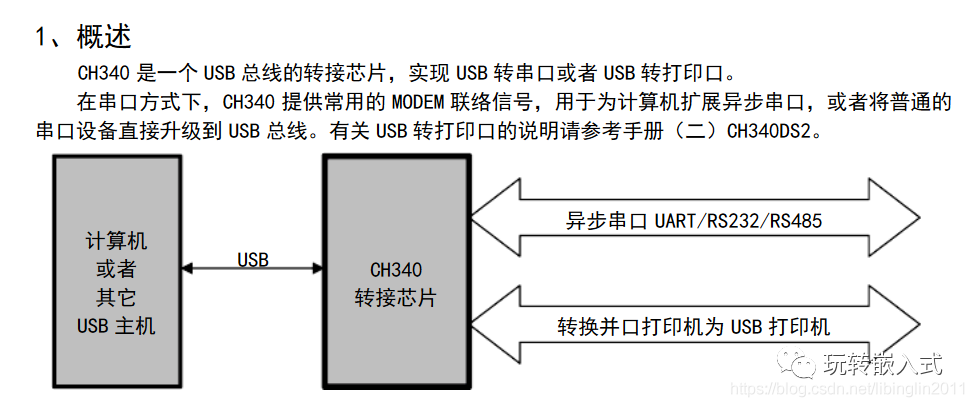

核心器件CH340系列

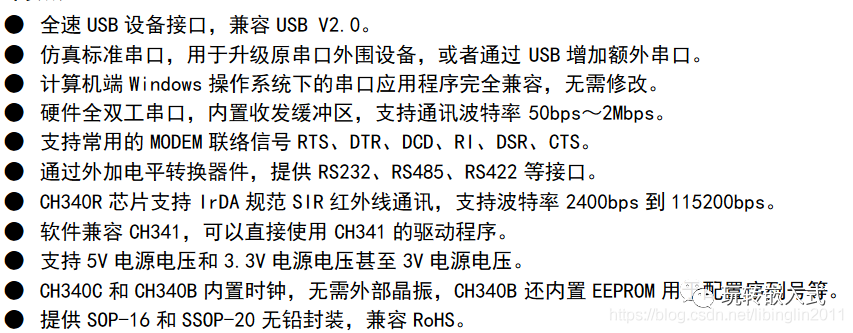

CH340G 是一个USB转串口的集成芯片,关键性能参数如下:

可以看到数据手册中的引脚描述:DTR#引脚是MODEM联络输出信号,数据终端就绪,低(高)有效,在USB配置完成之前作为配置输入引脚,可以外接4.7KΩ的下拉电阻在USB枚举期间产生默认的低电平。RTS#引脚MODEM联络输出信号,请求发送,低(高)有效。这两个MODEM联络信号是由计算机应用程序控制并定义其用途的,在软件下发点击下载按钮后,通常会给DTR#拉低、RTS拉高,然后延时一段时间后,拉高DTR#,RTS#恢复到低电平。

注意:新设计的电路板可以选用CH340C,内置晶振,无需外接晶振。

从原理图中可以看到这个两个引脚连接的逻辑电路如下:

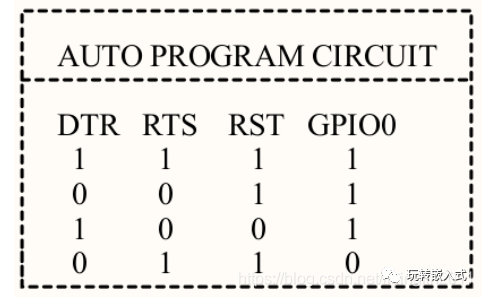

端口真值表

根据该电路,可以知道当 DTR为1, RTS为0时, nRST复位引脚拉低,反之,GPIO0 引脚拉低,得到的逻辑关系图如下:

这样的化,在点击下载按钮后,CH340G芯片的DTR处于低电平,RTS处于高电平,此时ESP8266的GPIO0被拉低,复位RST信号为高,ESP8266进入下载模式,CH340G的DTR和RTS电平翻转后,RST为0,GPIO0变1,ESP8266进入Flash运行模式,程序正常运行。这样就实现了ESP8266自动下载。