1. 突发!美国瞄准中国成熟制程芯片将启动供应链调查

商务部长雷蒙多(Gina Raimondo)表示,过去数年来,中国以令人忧心的做法扩大国内传统芯片产能,令美国业者更加难以与之竞争。

美国商务部指出,调查将在2024年1月展开,目标是降低中国「构成的国家安全风险」,焦点放在美国关键产业供应链所使用、采购的中国制传统芯片。

美国商务部21日发布报告指出,过去10年来,中国政府为国内半导体产业提供约1,500亿美元的补贴,对美国及其他外国竞争者带来了不公平的商业环境。

北京半导体行业协会付祕书长朱晶的评论

1),对设计公司的影响。对有计划带着高性价比国产芯片出海(到美国)的设计企业,可能要完全跟国内产能切割了。如果转国内产能的芯片公司,就专心做好国内市场。

2),对国内成熟工艺产能的影响。首先肯定拿不到美国设计企业客户成熟工艺的订单了,再有就是可能会让一部分国内设计企业客户放弃全面转产国内产能。国内大规模上成熟工艺确实要考虑一下产能过剩的风险。

利好UMC和GF,还有Tower,对国内Foundry短期内还不会有太大影响。而国内设计企业,想出海的,真的要考虑“planB”了~

2. 灿芯躺枪美国议员呼吁制裁

卢比欧写给美国商务部长雷蒙多(Gina Raimondo)的信指出,灿芯半导体例子显示,要快速采取行动避免中国芯片产业基础更强大。

美国共和党籍参议员卢比欧(Marco Rubio)20 日呼吁政府,应制裁灿芯半导体(Brite Semiconductor)。

路透社指出,灿芯半导体仍可取得美国投资与技术,包括从加州企业Synopsys和Cadence Design获芯片设计软件。

灿芯股份前身灿芯有限设立于2008年7月,系由香港灿芯出资设立的有限责任公司,设立时注册资本为300万美元。

需要指出的是,灿芯股份无国有股东,公司有6个外资股东,分别为NVP、BRITE EAGLE、庄志青(美国国籍)等。其中,庄志青任公司董事及总经理,直接持有公司3.44%股份。

2017年,灿芯股份拆除境外架构后,中芯国际全资子公司中芯控股持有灿芯股份的股权比例一度高达46.6%,后续随着多轮增资和股权转让,中芯控股持有灿芯股份的股权比例降至18.98%。与此同时,灿芯股份现任董事长赵海军,其曾在2017年10月至2022年8月期间担任中芯国际执行董事兼联合首席执行官时,还兼任灿芯有限董事长。

另外,灿芯股份与中芯国际的深度绑定还体现在关联采购方面。2019-2022年1-6月,公司主要向中芯国际采购,各期采购金额分别为3.03亿元、3.34亿元、7.12亿元和4.51亿元,占当期采购总额的比例分别为80.4%、69.02%、77.25%与86.62%。

3. 下一代晶体管结构小荷已露尖尖角

在刚刚落下帷幕的2023年IEEE国际电子器件会议(IEDM2023)上,台积电、三星和英特尔各自秀出了在下一代晶体管结构领域的尖端技术。图中这款被称为“互补场效应晶体管(CFET)”的晶体管结构,被视为1nm以下制程的关键要素,是继FinFET和GAA之后的新一代的晶体管技术。它的出现,将为半导体行业带来哪些不一样的图景?

CFET与此前晶体管结构的最大不同之处,在于采用晶体管垂直堆叠结构,这或将开启三维晶体管结构新纪元。

由于晶体管结构从平面转换到了立体结构,难以继续通过等比例缩小晶体管尺寸来增加芯片上器件密度。随着摩尔定律的不断发展,芯片制程也愈发接近物理极限,为了能够进一步增加单位面积上的器件数量,业内开始尝试将原本的立体结构晶体管再进行堆叠,提出了采用垂直堆叠结构的CFET。

台积电最新资料显示,采用CFET垂直堆叠架构的芯片,相较采用Nanosheet(GAA)架构的器件,面积最多能缩小50%。

台积电指出,CFET晶体管现已在台积电实验室中进行性能、效率和密度测试,并已经实现了48nm的栅极间距

台积电在其CFET晶体管工艺中,尝试将纳米片中和锗的交替层进一步隔离。例如,台积电通过特定的蚀刻方法去除纳米片中的锗材料,从而释放硅纳米线。为了能将纳米片中硅和硅锗的交替层进一步隔离,台积电使用了锗含量异常高的硅锗。这种材料比其他SiGe层蚀刻得更快,因此可以在释放硅纳米线之前构建隔离层。

公开资料显示,台积电或将在其2032年量产的A5工艺中,采用CFET架构。

三星将CFET晶体管结构称为3DSFET,目前的栅极间距为45/48nm。在技术创新方面,三星实现了对堆叠式pFET(P沟道场效应管)和nFET(n沟道场效应管)器件的源极和漏极进行有效的电气隔离。这种隔离可以有效地减少漏电流,提高器件性能和可靠性。此外,三星还通过将湿化学物质的刻蚀步骤替换为新型干法刻蚀,以此让芯片中CFET器件的良率显著提升。

英特尔展示了将CFET晶体管结构与背面供电技术相结合的新技术,并利用该技术实现了60nm的栅极间距。英特尔表示,此次在CFET方面的创新之处,在于将PMOS(P型金属氧化物半导体)和NMOS(N型金属氧化物半导体)结合在了一起,使得开关速度和驱动能力具有互补性,从而提升了晶体管的整体性能。将PMOS和NMOS与其PowerVia背面供电器件触点相结合,以此更好地控制电流的流动,提高电源效率。

4. 基辛格:英特尔18A略优于台积电N2,两年内实现技术领先

英特尔CEO基辛格(Pat Gelsinger)近日受访时指出,英特尔18A制程及台积电N2制程的晶体管似乎差不多、没有哪家具备显著优势,但不错的晶体管、极佳的背面供电让18A制程稍稍领先N2。他还称英特尔将在两年内实现技术领先,未来甚至有希望为英伟达代工芯片。

报道称,英特尔的未来取决于重新获得半导体制造领域的技术领先地位,基辛格相信这将在两年内实现。

基辛格表示,英特尔18A制程及台积电N2制程没有哪家具备显著优势,但多数人都说英特尔的背面供电技术更加优秀,这让硅晶片拥有更好的面积效率、意味着成本降低,供电较佳则代表效能更高。

5. 真正看懂国产CPU:6种指令集,N家公司,谁能自主可控?

国产CPU,除了兆芯和海光采用了X86指令集之外,其余的都采用了简单指令集,如ARM、MIPS、alpha、RISC-V等。简单指令集相比复杂指令集,指令数量较少,功能较简单,但也带来了CPU的设计和制造难度较低,成本较低,功耗较低的优势。

指令集、芯片架构和IP之间的关系。指令集,就是CPU运行的指令的格式和规范,是软件和硬件之间的接口“语言”,是交互的一种标准规范。芯片架构,就是CPU的内部结构和组织,是指令集的具体实现方式,是硬件的设计和制造方案。IP,就是Intellectual Property,即知识产权,是指一些CPU的核心部件或功能模块,如算术逻辑单元、缓存、总线、控制器等,是芯片架构的组成元素,是硬件的具体实现细节。

指令集是26个字母,芯片架构则是由这些字母组成的单词,而IP则是由单词组成的文章提纲。

如果获得了永久的指令集授权,那么自己可以根据这26个字母,随便组成单词,再随便写成文章,自由度非常高。

如果只获得架构授权,那么只能用固定好的单词,来写文章,不能自己组装出新的单词。

如果获得了架构和IP,那么就只能按照对方给的提纲,在提纲的规定范围内,用对方提供的单词写文章。

通过以上的分析,我们可以看出,国产CPU的自主可控能力,是有高低之分的。从指令集的角度来看,龙芯应该是排第一的,它完全自主研发了LoongArch指令集,不受任何外部的限制和影响。其次是RISC-V、申威、海光,它们都有较高的自由度,可以基于开源或自拓展的指令集,设计和制造芯片。最后是鲲鹏、飞腾,它们只能基于ARM的芯片架构,开发出与ARM相似的CPU,不能自由地修改或拓展指令集。

从芯片架构的角度来看,海光应该是排第一的,它获得了AMD的Zen1芯片架构的授权,可以开发出与AMD相似的CPU,性能和效率都有较高的水平。其次是鲲鹏、飞腾、龙芯、申威,它们都有自己的芯片架构,可以根据自己的需求和特点,设计和制造芯片。最后是RISC-V,它的芯片架构还不够成熟和统一,需要不断的优化和完善。

从IP的角度来看,鲲鹏、飞腾、海光应该是排第一的,它们都获得了一些CPU、GPU核的IP授权,可以提高芯片的功能和性能。其次是龙芯、申威,它们都有自己的IP,可以根据自己的需求和特点,设计和制造芯片。最后是RISC-V,它的IP还不够丰富和完善,需要不断的开发和创新。

6. 6台已抵达,7nm芯片量产提上日程?外媒:围堵计划已落空

不久前上海积塔半导体公司宣称已有6台抵达,而业内透露国产7nm芯片有望实现量产,引得外媒直呼“围堵计划已落空”。

而在此之前,美方要求对华断供,从而拖慢“国产芯”的发展进程。然而他们万万没想到,荷兰光刻机巨头阿斯曼“擅作主张”,偷偷对华提供6台光刻机。这究竟是怎么回事呢?

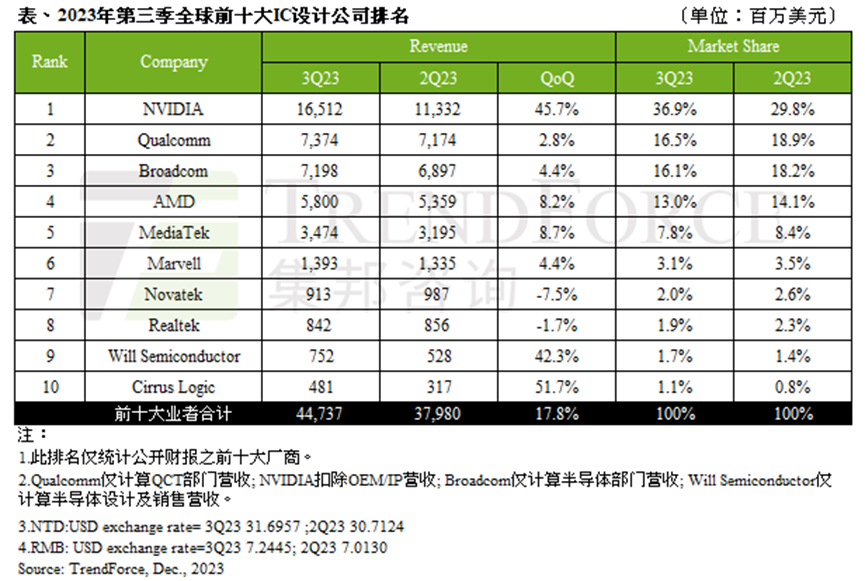

7. 2023年第三季全球前十大IC设计业者营收季增17.8%

TrendForce集邦咨询表示,受惠于智能手机、笔记本电脑供应链库存落底并且进入季节性备货旺季,加上生成式AI相关主芯片与零部件出货加速,第三季全球前十大IC设计公司营收环比增长17.8%,以447.4亿美元创下历史新高。其中,NVIDIA(英伟达)在AI热潮下,营收、市占率表现均居冠;第十名则因智能手机备货推动,由模拟IC供应商Cirrus Logic取代美系PMIC厂MPS。从各家营收表现来看,受惠生成式AI、LLM(大型语言模型)热潮持续,带动NVIDIA第三季营收成长至165.1亿美元,环比增长45.7%。其中,数据中心业务已占近八成营收,是NVIDIA业务成长的关键动能。

8. ASML2024年推出2nm芯片制造的高NA光刻机价格高达3亿欧元

目前,EUV光刻机可以支持芯片制造商将芯片工艺推进到3nm左右,但是如果要继续推进到2nm甚至更小的尺寸,就需要更高数值孔径(NA)的High-NA光刻机。

据悉,用于2纳米芯片的光刻机型号为High-NA量产型EUV光刻机EXE:5200,将采用不同的镜头系统,NA更大。ASML发言人曾透露,EXE:5200是ASML下一代高 NA 系统,具有更高的光刻分辨率,可将芯片缩小1.7分之一,同时密度增加至2.9倍。

目前,ASML官网列出的EUV光刻机仅有两款——NXE:3600D和NXE:3400C,均配备0.33 NA的反射式投影光学器件及13.5nm EUV光源,分别适用于3/5nm和5/7nm芯片制造。

此前有媒体报道,ASML第一台0.55 NA EUV光刻机计划于2025年后量产,第一台将交付给英特尔。而最近有消息称,ASML在2024年规划产能仅有10台,而英特尔已经预订了其中6台,不过ASML计划在未来几年内将此设备产能提高到每年20台。

英特尔此前就曾对外表示,其将率先获得业界第一台High-NA EUV光刻机。同时,英特尔还透露,公司已完成Intel 18A(1.8nm)和Intel 20A(2nm)制造工艺的开发。其中,Intel 20A计划于2024年上半年投入使用,进展良好的Intel 18A制造技术也将提前到2024年下半年进入大批量制造(HVM)。上述芯片工艺或将有部分利用High-NA EUV光刻机。

目前,三星电子一直在努力确保采购更多EUV光刻设备,目标是在2024年上半年进入3nm世代的第二代工艺,在2025年进入2nm工艺,在2027年进入1.4nm工艺。

而台积电也很早就表示,将在2024年取得ASML新一代High-NA EUV光刻机,同时将在2025年实现2纳米芯片的量产。

据悉,ASML最新的High-NA EUV光刻机设备的价格将在3亿至3.5亿欧元之间,当前热销的EUV光刻机单价则为1.5亿-2亿美元。

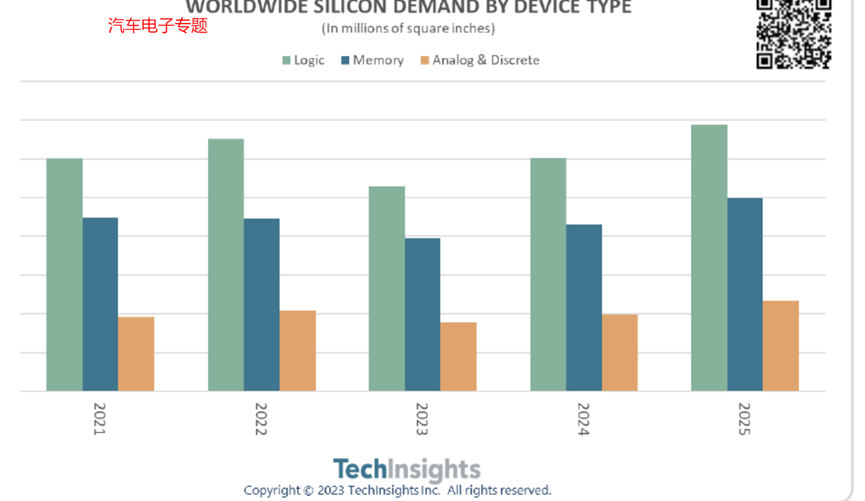

9. 全球硅需求将在2023年下降15%

TechInsights预计,2023年全球对硅的需求将下降15%(低于我们之前预测的下降11%)。

这种下降是由疲软的半导体市场推动的,自2022年下半年以来,半导体市场一直在努力应对库存过剩和需求低迷。这种疲软在很大程度上是由供应过剩驱动的,而供应过剩是由新冠疫情期间需求的异常拉动造成的。由于这一具有挑战性的背景,预计2023年IC销量将下降12%,而作为硅消费主要驱动因素的IC出货量预计将下降14%。

尽管出现了季节性低迷,但TechInsights预测半导体行业将在长期内继续增长,硅需求预计将以8%的复合年增长率增长。人工智能兴起、电动汽车市场的扩大和数据经济的增长推动了这一增长。

10. 投资155亿元,格科微12英寸CIS厂投产

12月22日上午,国内CMOS龙头企业格科微举办20周年庆典暨临港工厂投产仪式。格科微临港工厂一期总投资达155亿元;规划产能2万片。

格科微董事长兼首席执行官赵立新表示,当前公司正迎来成立20年来的最佳经营局面,Fabless向Fab-lite转型的战略目标已成功实现。未来,格科微将以此为基,努力实现新战略,暨紧扣客户需求,推动核心技术产品化,跨越30亿美元收入台阶。

该项目于2020年3月签约,同年11月正式开工,2021年8月厂房主结构封顶,2022年9月投片成功,2023年2季度首批产能正式量产。

GC32E2是公司此前发布的GC32E1“升级版”,在单芯片高像素技术平台上搭载DAG HDR技术和AON低功耗技术,支持前摄相位自动对焦,也定位于主流旗舰手机前后摄;GC50E0是公司推出的第一颗5000万像素产品,也是市场上首颗单芯片5000万像素产品;在推出0.7μm的GC50E0的同时,格科微重磅推出1.0μm大底的5000万像素产品GC50B2,同样在单芯片基础上搭载专利DAG HDR技术,适用于中高端智能手机主摄。这三款产品的发布体现了公司的研发能力与效率,极大拓宽公司在高像素产品领域的市场空间。

赵立新在产品分享会上表示,公司在16M像素以下产品领域已经具有市场领先地位,并且此前推出的单芯片高像素产品GC32E1赢得了客户的高度认可,而此次推出的三款单芯片高像素产品将助力公司进一步拓展中高端市场。