作者: 付斌

随着摩尔定律不断推进,晶体管越来越小,密度越来越高,堆栈层数也越来越多。此时,细节就更能为芯片挤压更多性能,背面供电就是一个。与此同时,它可能也是实现1nm的关键。

纵观目前行业,英特尔先发制人,台积电、三星加码跟进,在IEDM2023上,英特尔继续推进这项技术,这次英特尔又放出了背面触点这样的“王炸”新技术,同时将3D堆叠与PowerVia和背面触点三种技术结合在了一起,证明了这项技术最终可能在晶体管密度微缩发挥作用。

为什么是背面供电

背面供电(BSP/BS-PDN),就是将原先和晶体管一同排布的供电网络直接转移到晶体管的背面重新排布。

想了解背面供电网络的价值,就需要从芯片制造开始。

芯片内部的功率传输网络需要从蚀刻晶体管的第一层开始,这是芯片上最小和最复杂的层,也是最需要EUV和多重曝光等高精度工具的地方。简而言之,它是芯片中最昂贵和最复杂的层,对芯片的构造方式和测试方式都有重大影响。

在此之上,逐渐搭建各种金属层,以将电子传输到不同晶体管(包括缓存、缓冲器、加速器)之间所需的所有布线,并进一步为更上层的电源提供路由,就像制作比萨饼一样。现代高性能处理器通常有10~20个金属层。在其之上还有另外两个“巨型金属”层,仅用于电源布线和放置外部接口。

芯片制造完成后,就会被翻转过来倒装,然后所有的连接部分,包括电源和数据接口就变到了芯片底部,晶体管在芯片顶部。倒装的好处是芯片调试和冷却可以从顶部接触,从而变得更为方便。

然而,前端供电的缺点在于,电源线和信号线都位于芯片的同一侧。两条线都必须向下穿15层以上才能到达晶体管,既要争夺空间,同时还要避免干扰,并且距离越长,电阻越大,效率越低,这被称为IR Drop/Droop效应。

既然如此,放到背面就好了。

一方面,既能将大截面、低电阻线用于背面互连线,而将正面主要用于信号传输,并对它们分别进行独立优化;另一方面,能够带来性能提升,将供电线从前面转移至背面,因此原本拥挤的前部,现在释放了更多空间;此外,将导线分开,这对降低工艺、复杂性和成本都有重要意义。

其实,在过去,这并不是一个大问题。但随着芯片尺寸越来越小,这一问题越来越明显。前端功率传输没有明显的硬性限制,但考虑到每一代芯片都越来越难缩小,这个问题已经变得太大,或者更确切地说太昂贵而无法解决。

背面供电则是将信号和电源传输网络分开,一侧是信号,另外的一侧(背面)是电源。

当然,背面供电并非简单粗暴地倒转,而是存在诸多难题,包括测试难题和制造难题。

PowerVia:英特尔的答卷

根据之前的信息,英特尔的背面供电技术名为PowerVia,将于2024年上半年在Intel 20A制程节点上推出。

作为延续摩尔定律的关键技术,英特尔将PowerVia技术和RibbonFET晶体管的研发分开进行,以确保PowerVia可以被妥善地用于Intel 20A和Intel 18A制程芯片的生产中。

PowerVia和RibbonFET的组合,尤其是PowerVia被英特尔视为新的“FinFET”时刻,PowerVia是绝对领先的,预计台积电在2026年底或2027年初的N2P节点之前不会部署这项技术。

不止如此,PowerVia被英特尔拿来与如应变硅(strained silicon)、高K金属栅极(Hi-K metal gate)和FinFET晶体管的创新相提并论,这几项技术都是英特尔率先在业界推出的。

“这是英特尔迎接埃米(angstrom)时代的创举”,更重要的是Intel 20A和Intel 18A制程不只是面向英特尔产品,同时也对英特尔代工服务(IFS)具有深远意义。

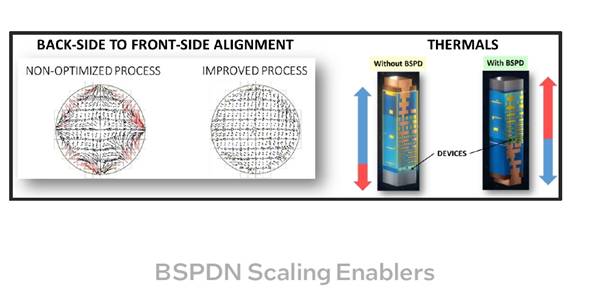

首先,背面供电对简化芯片的构造具有重要影响。可以放宽金属层的厚度,比如说,Intel 4 + PowerVia的测试节点允许36 nm间距,而不是在Intel 4上要求30 nm 间距,直接简化了整个芯片最复杂和昂贵的处理步骤,使其更接近Intel 7的工艺尺寸。

其次,背面供电网络也为芯片提供部分性能改进。通过更直接的方式缩短晶体管的功率传输路径有助于抵消 IR Droop 效应,从而更好地向晶体管层传输功率,并且消除干扰,解决了数十年来的互连瓶颈问题。

从数据上来看,利用了PowerVia,IR drop可减少30%,Fmax可提高6%。这意味着,对于工程师是绝对的利好,EM、IR供电等问题将da大减少,也可以将将单元利用率大大提高至90%,有助于实现晶体管的大幅微缩,让芯片设计公司能够提升产品性能和能效。

背面触点:为背面供电带来更多可能

IEDM 2023上,英特尔将发表题为《通过背面供电和3D堆叠实现面向未来制程节点的技术创新》(Process Innovations for Future Technology Nodes with Back Side Power Delivery and 3D Device Stacking)的论文,对超越PowerVia的背面供电系列创新研究成果进行详尽的解读。

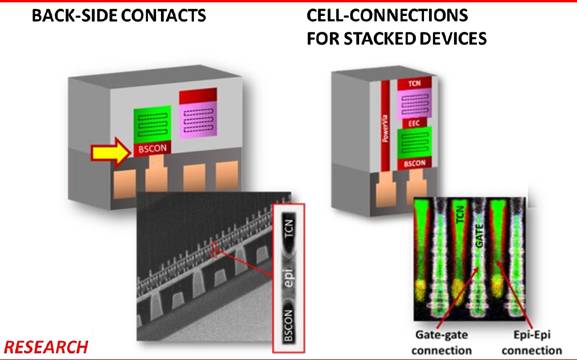

此次研究成果主要是背面触点这一全新技术,让英特尔首次拥有单一器件层,可从上面或下面,亦或在需要的时候从上下同时连接到晶体管。它可以与 PowerVia 一起部署,也可以单独部署。也就是说,背面供电技术发展有了更多可能。

背面触点有什么作用?

第一,可以从背面,通过大截面导线直接向晶体管供电,而不必绕路,这在供电上大大提高了性能。

第二,因为没有PowerVia,单元内金属数量减少,电容及电容自旋也就随之减少,因此开关速度加快,同时功耗降低。

第三,不需要为PowerVia预留空间,可以将所有东西更紧密地固定在相同的区域内,就意味着可以在单位面积内放入更多晶体管。

总结起来就是,背面触点不仅保留了背面供电技术所有优点,还带来了更多性能或能效比方面的优势,并有助于进一步实现微缩面积。

背面触点技术可以为晶体管堆叠的互连需求带来改变。

之前,大多数互连都是针对单层晶体管需求而生,但当开始堆叠晶体管,关键思路就是通过PMOS晶体管上叠加NMOS晶体管,在单位面积上增加晶体管数量。堆叠晶体管为互连创造了一个非常有趣的拓扑结构,需要同时为顶部和底部的晶体管提供电力和信号,无法选择只向其中一个进行供电。

此时,便可以通过使用PowerVia和背面触点来实现供电,当同步使用两种技术,就能实现非常高效的晶体管堆叠。除了这两个关键技术外,还需要栅极之间的连接及一对NMOS 和 PMOS 堆栈的源极之间的连接,这都需要新的垂直互连,被称为栅极连接和 Epi-Epi连接,英特尔已经能够制造出这种连接。

也就是说,英特尔新的垂直互连技术已经开始设备化。接下来英特尔将继续微缩互连尺寸,因此英特尔需要确保上述所有功能在更小的尺寸下有一致性,以更小的尺寸制造它们,连接它们。

在热效应方面,PowerVia已经证明,在同等功率密度下,背面供电的热性能和响应与没有背面供电的标准设计基本一致。值得一提的是,研究发现,使用背面触点不会影响热性能。

在此研究中,英特尔找到了在 PowerVia 的基础上进一步拓展背面供电技术并实现晶体管微缩的途径。这些技术与晶体管堆叠相兼容,这对于在实践过程中以较高的面积效率实现晶体管堆叠而言至关重要。

3D堆叠与背面供电的双向奔赴

在IEDM 2023上,英特尔还发表了题为《60 纳米栅极间距堆叠式 CMOS 逆变器的实现,结合PowerVia和直接背面触点技术》(Demonstration of a Stacked CMOS Inverter at 60nm Gate Pitch with Power Via and Direct Backside Device Contacts)的论文,超越RibbonFET进一步推进晶体管微缩。

简单来说,这篇论文就是将IEDM2021发表的3D堆叠技术与PowerVia和背面触点结合,关注的是实现一种协同效应,将器件堆叠与通过使用背面供电技术进行设备互连的高效方式相结合。

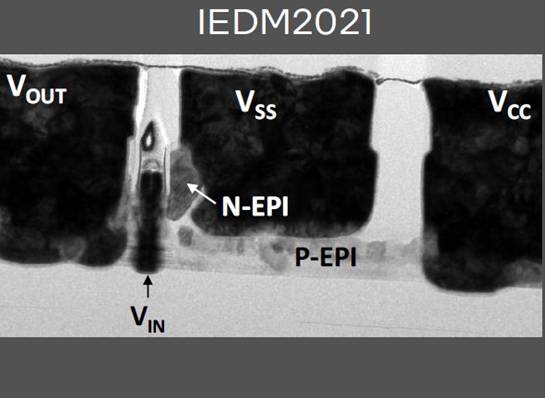

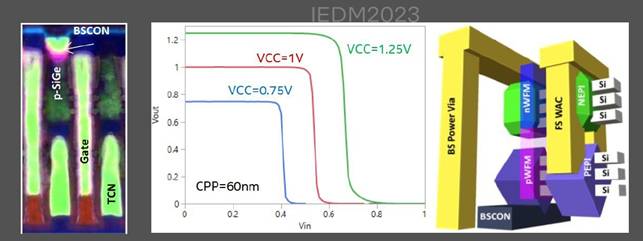

回顾IEDM 2021上,英特尔发表的CMOS晶体管3D堆叠早期研究,当时英特尔只能使用正面处理技术,意味着必须引出额外触点,比如远离晶体管栅极的标有Vcc触点,从而占用额外的面积,这将削弱晶体管堆叠所带来的优势。彼时,透射电子显微镜(TEM)图像显示了一个非常薄的栅极,位于左侧大约三分之二的位置,需要独立接触顶部和底部晶体管的大型触点。

IEDM2023上,英特尔成功地将单片NMOS和PMOS与PowerVia以及背面触点相结合,演示了这种紧凑、高密度器件堆叠的方法,是一种最终可能在晶体管密度的微缩中发挥作用的技术。

具体而言,两组RibbonFET叠在一起,PMOS在底部,NMOS在顶部,每个都有三个Ribbon以最大化器件的驱动电流。

传统技术中,设备是并排的,图案化(vertically pattern)是直截了当的,但当晶体管堆叠时,必须以垂直方式进行图案化。虽然很难,但是英特尔可以实现垂直的图案化,沉积源极和漏极,用于底部器件的PEPI,通常由硅锗制成,顶部的NEPI通常由硅制成。

相同的操作需要在器件栅极部分进行,同样必须以垂直方式沉积金属。同时,还要提供背面触点,单独接触底部设备,因为没有其它能够接触的空间,以及PowerVia背面供电,将顶部晶体管与晶圆背面连接。

环绕式触点技术是一种在反相器内部节点,或其它需要将两个晶体管源极包裹在一起的触点,它可以让同一轨道接触NEPI和PEPI,与使用PowerVia和背面触点连接进行某种包围相比,这种方式同样提供了一种高效的方法。

值得一提的是,与在传统技术中两个晶体管(NMOS和PMOS)必须并排放置的情况非常不同,英特尔能够以微缩至60纳米的栅极间距垂直地堆叠互补场效应晶体管(CFET)。与此同时,从电压传递曲线来看,三种技术叠加后的曲线与RibbonFET或FinFET技术中的反相器(仅由一个NMOS和一个PMOS组成的CMOS)一样。

明年,PowerVia将生产准备就绪,在业界率先实现背面供电,英特尔正在研究如何微缩这项技术,让它真正提升性能。与此同时,英特尔正在积极推进‘四年五个制程节点’计划,并致力于在2030年实现在单个封装中集成一万亿个晶体管,PowerVia对这两大目标而言都是重要里程碑,可见,一个全新的、令人兴奋的互连新纪元正在走来。