首先来手册里的一段话。

三种不同的时钟源可被用来驱动系统时钟 (SYSCLK)

· HSI振荡器时钟

· HSE振荡器时钟

· PLL时钟

一般用的是PLL时钟,后面有证据。

我们可以通过库函数获取各时钟值

void RCC_GetClocksFreq(RCC_ClocksTypeDef* RCC_Clocks)

在我的系统里,把时钟值打印信息如下:

SYSCLK:0x44aa200 //72000000, 72MHz

HCLK:0x44aa200 //72000000, 72MHz

PCLK1:0x2255100 //36000000, 36MHz

PCLK2:0x44aa200 //72000000, 72MHz

ADCCLK:0x2255100 //36000000,36MHz

RCC-》CFGR:0x001D040A //PLL输出作为系统时钟

可推测几个预分频值为

AHB prescaler = 1

APB1 prescaler = 2

APB2 prescaler = 1

ADC prescaler = 2

根据读取RCC-》CFGR寄存器值为:0x001D040A,上面推测完全正确。

CFGR寄存器的SWS段也说明:PLL输出作为系统时钟。

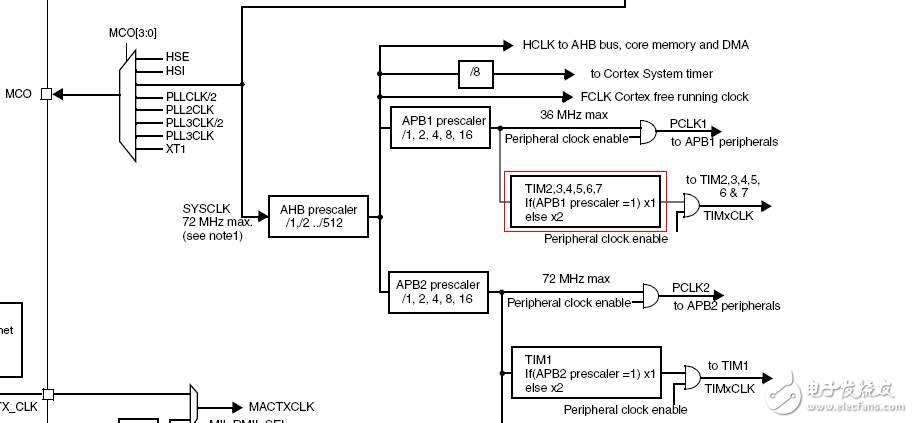

TIM2使用PCLK1,但注意时钟树里有这一段

见附图

已知APB1 prescaler=2,故TIM2CLK = PCLK1*2 = 72MHz.

所以被TIM2分频的时钟大小是72MHz。

我的程序也证明了这点

TIM_TimeBaseInitTypeDef tim2_InitStruct;

TIM_DeInit(TIM2);

RCC_APB1PeriphClockCmd(RCC_APB1Periph_TIM2, ENABLE);//Enable Timer2 clock.

NVIC_ConfigurationForTimer2();

// PCLK1=36MHz, PSC=36000-1, CK_CNT=36MHz/(PSC+1)=1000

// ARR=2000, 1s/1000 * 2000 = 2s.

tim2_InitStruct.TIM_Prescaler = 36000-1;

tim2_InitStruct.TIM_Period = 2000-1;

tim2_InitStruct.TIM_CounterMode = TIM_CounterMode_Up;

tim2_InitStruct.TIM_ClockDivision = TIM_CKD_DIV1;

tim2_InitStruct.TIM_RepetitionCounter = 0;

TIM_TimeBaseInit(TIM2, &tim2_InitStruct);

TIM_ClearFlag(TIM2, TIM_FLAG_Update);

TIM_ITConfig(TIM2, TIM_IT_Update, ENABLE);//Enables the specified TIM interrupts.

这段配置原本以为定时时间是2s,实际只有1s。看了手册才理解原因。