过去三年,存储市场波动持续影响着整个半导体行业。由于2019年DRAM和NAND的价格下跌近50%,导致收入暴跌超过30%。然而,尽管2020年全球经济遭遇新冠侵袭,但这一年DRAM和NAND市场收入分别增长了28%和6%。进入2021年,DRAM市场收入猛增40%以上至940亿美元,几乎创下历史新高。

WSTS数据显示,2022年全球存储芯片行业市场规模约为1392亿美元,占半导体行业比重约为20%,仅次于逻辑芯片,成为第二大半导体品类。存储芯片产品以DRAM和NAND Flash为主,其中DRAM为最大单一品类,其2022年的市场规模为790.61亿美元,市占率为56.8%。在该市场,三星电子、SK海力士及美光三家厂商拥有高达95%的占有率。

长期来看,DRAM和NAND市场需求将持续增长

DRAM:计算将推动需求增长

尽管2023年DRAM市场将会走向负增长,且下行速度极快。但是长期来看,DRAM市场将随着计算需求的增长而持续上扬。

据Gartner预测,2023年全球DRAM市场增幅将下降39.4%,收入总额为476亿美元。但该市场将在2024年快速复苏,DRAM收入将随着价格的回升而增长86.8%。另外,Yole Intelligence则预计,未来五年,数据中心对 DRAM 的需求将以超过30%的复合增长率增长,这将使同期整体DRAM需求每年增长20% 以上。同时,随着5G不断融入人工智能、物联网等应用之中,新的计算需求出现将长期推动DRAM市场增长。

未来半年,NAND市场行情与DRAM类似

进入2023年,NAND供应商采取行动重新平衡供需动态,他们不仅减少对市场的出货量,且大部分供应商都宣布削减晶圆厂利用率或减少晶圆开工。市场研究机构Yole分析称,所有供应商不仅削减了2023年资本支出,并推迟了路线图进程。其中,仅NAND 资本支出预计将同比下降约40%。Yole指出,随着库存水平的正常化回归以及OEM等采购信心的恢复,将为今年晚些时候的 NAND复苏提供了希望。

不过,尽管业界期望消费类电子需求下半年企稳回升,带动疲软的NAND市场复苏,但是实际上可能会被“泼冷水“。

据分析机构Gartner 今年5月预测,未来6个月NAND市场的动态将与DRAM市场类似。需求疲软和大量供应商库存将造成供过于求,导致价格大幅下跌。因此,2023年NAND收入预计将下降32.9%至389亿美元。到2024年,由于供应严重短缺,NAND收入预计将增长60.7%。

新需求成为推动NAND长期增长的驱动力

尽管市场仍在短期内受到波动,但NAND存储正迎来高速增长期。

在消费端,传统硬盘硬盘 (HDD) 需求不断被基于 NAND 的固态硬盘 (SSD)所蚕食。例如这类NAND需求的主要驱动因素包括超大规模厂商和传统企业OEM 的企业级固态硬盘 、个人电脑和游戏机越来越多地采用 SSD,以及智能手机和其他移动设备需求的持续推动。在企业需求端(B端),随着生成式AI(Generative AI 或 AIGC)以及本地、边缘和云存储需求的大幅增长,将推动NAND强劲增长。

根据预测,2022-2028 年的SSD市场总规模将从290亿美元增加至670亿美元,期间复合年增长率约为15%。据Yole指出,包括消费类个人电脑、渠道分销和游戏系统在内的客户端市场与包括服务器和存储附加驱动器在内的企业市场之间的情况将大不相同。未来几年,客户端产品的需求将疲软,但数据中心空间中高级工作负载的低延迟存储需求将推动企业级SSD的增长。

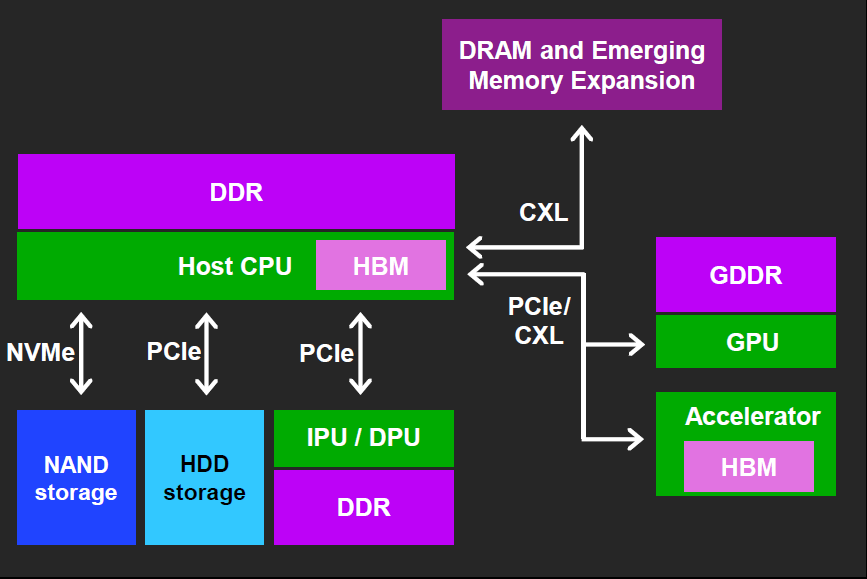

图1:数据密集型工作负载推动异构数据中心架构 ,图片来源:美光

图1:数据密集型工作负载推动异构数据中心架构 ,图片来源:美光

汽车行业成存储增长最快的细分市场

根据分析机构Yole Intelligence预测,到 2027年汽车存储器的收入将增加两倍,占汽车半导体市场的17%,2021-2027复合年增长率为20%,将超过同期全球存储器市场(8%)和汽车半导体(10%)的复合年增长率。

资料显示,目前汽车中的信息娱乐单元、仪表盘和连接性的驾驶舱是内存需求的主要集中区域;其次,为ADAS & AD 对内存的使用量,这部分需求在2021年就占整车半导体收入的24%。另外,其他关于动力总成、底盘和安全以及车身和舒适性所需的限制最多,则主要使用较为稳健的EEPROM和NOR 闪存。

预计到2027 年,Cockpit(座舱)仍将是汽车中内存的主要消耗者,但ADAS & AD的收入份额将增至36%。届时,DRAM和NAND预计将占汽车内存收入的近90%。

市场需求在变,技术也在更迭

随着各种应用场景对高速和高性能存储要求的不断提升,主流存储厂商也在积极寻求将NAND架构从平面 (2D)转变为3D结构,以及持续推进层数的增长。

所谓3D NAND,就是通过在垂直堆栈中将多组存储单元相互层叠以实现容量递增。闪存芯片内的层数越多,总存储容量就越大。目前各大厂商均在制造100层以上芯片,并已研发和量产了更高层数的存储产品。

尽管进入时间节点不同,但各主流大厂均取得了不俗成果。

比如,美系厂商美光在2020年11月推出首款176层3D NAND Flash后,又于2022年7月2宣布推出全球首款量产的232层NAND,这也是全球首款突破200层大关的固态存储芯片。

韩系厂商SK海力士自2020年12月完成176层NAND研发,至2022年8月其又宣布成功研发了全球首款业界最高层数的238层NAND闪存,并于同年展示了首款238层4D NAND。根据技术路线,SK海力士3D NAND闪存堆叠层数将于2025年达到500层,并于2030年达到800层以上。三星电子在2022年11月宣布量产236层3D NAND 闪存芯片。三星声称,到2030年将打造出1000层的V-NAND。

美日合作共同推进。2021年,日系厂商铠侠与美系西部数据共同推出了第六代 162层3D NAND技术。同年,两家公司又联合在日本投资最新的Fab7工厂,拟进一步提升铠侠的产能。今年3月,双方再宣布推出第八代BiCS 218层3D NAND,同时,双方还计划在年内展示300多层的3D NAND技术。

面对市场竞争,除技术升级之外,产能扩张也是提升竞争实力的有效手段。一种方式是投资建厂,比如三星曾宣布持续扩建韩国的平泽制造基地(Pyeongtaek),并扩大了其在中国西安的产能;甚至在面临被中国制裁禁售之下,美光依然增加了对位于中国西安的基地进行投资。另一种则是行业间的整合,比如SK海力士收购英特尔的NAND/SSD业务(更名为Solidigm),以及传闻铠侠/西部数据合并(取代铠侠独立上市)。通过收购英特尔相关业务,SK海力士不仅拥有了前者位于中国大连NAND闪存制造工厂资产,更重要的是借助于收购,其在NAND Flash领域的市场份额超越铠侠,位居世界第二,仅次于三星。不过,倘若铠侠、西部数据能成功合并,或将在市场占有率上扳回一局。

NAND和DRAM技术路线

万物互联时代,数据需求暴增,数据存储介质需求也迎来大发展。因此,为了维持NAND更好的性能,更低的成本及更高的密度,业界正在大量研究新技术解决方案,其中,包括互补金属氧化物半导体 (CMOS) 键合阵列 (CBA) 架构。例如长江存储 (YMTC) Xtacking (晶栈)方法。

通常,3D NAND 单元阵列位于其外围电路(如页面缓冲器、感测放大器、电荷泵和 I/O)旁边或之上。同时,从半导体制造的角度来看,使用相同的制造技术制造存储器和外围逻辑并不完全有效。CBA 和 Xtacking架构涉及使用最佳生产节点在单独的晶圆上生产3D NAND单元阵列和 I/O CMOS,这使其能够最大限度地提高存储阵列的位密度和I/O性能。而在Xtacking架构问世前,市场上的3D NAND主要分为传统并列式架构和CuA(CMOS under Array)架构。

2023年3月,铠侠和西部数据宣布了最新3D闪存技术的详细信息。两家公司开发了开创性的 CBA(CMOS 直接键合到阵列)技术,其中每个 CMOS 晶圆和单元阵列晶圆都在其优化条件下单独制造,然后粘合在一起以提供更高的位密度(提高50%以上)和更快的 NAND I/O速度(提高 50% 以上)。

2023年6月,SK海力士宣布已开始量产238层4D NAND闪存,并正在进行产品验证。据悉,此产品的数据传输速度为每秒2.4Gb(千兆比特),较上一代的速度快50%。

3D封装技术采用立体式封装结构,将多个芯片同层或不同层交叉封装在一个封装体,,增加了芯片之间的连通性和互联性,并显著提升了芯片电路性能。目前,业界对于下一代3D封装准单芯片基于混合键合(Hybrid Bonding),将集成密度和性能再提升10倍。为此,主流存储制造商都在使用混合键合设备进行研发。根据Yole指出,铠侠和三星等厂商正在将晶圆到晶圆键合引入到NAND路线图中。

据泛林集团(Lam Research)关于半导体3D发展趋势资料的介绍,逻辑领域的3D过渡也已经开始,FinFET(鳍式场效应晶体管)技术让位于全包围栅极 (GAA) 晶体管和互补场效应晶体管 (CFET) 架构展示出极大优势。制造方法和技术的持续进步对于实现并进一步推动下一代GAA晶体管、DRAM架构和3D NAND器件(目前已包含200多层)的微缩至关重要。

然而,在3D时代,半导体微缩非常困难。在单个工艺腔室中实现多种功能可能是一个有效途径,它需要整合不同的沉积或刻蚀技术来处理3D结构的需求,甚至需要同时整合沉积和刻蚀技术,以更好地覆盖3D外形和原位修复工艺。

不过,好在技术进程总在持续推进之中。2023年6月9日,Tokyo Electron(东京电子)宣布其开发团队(等离子蚀刻系统的开发和制造基地)已开发出一种能够生产存储器的创新蚀刻技术先进的3D NAND设备中的通道孔,堆栈超过400层。该团队开发的新工艺首次将电介质蚀刻应用带到了低温范围,产生了具有极高蚀刻速率的系统。这项创新技术可在短短33分钟内实现10μm深的高纵横比(晶圆上形成的图案的深度与宽度之比)蚀刻。

图2:蚀刻后存储通道孔图案的横截面SEM图像,以及孔底部的FIB切割图像

图2:蚀刻后存储通道孔图案的横截面SEM图像,以及孔底部的FIB切割图像

图片来源:东京电子

此外,在DRAM业务中,目前的共识是平面微缩——即使通过极紫外光刻 (EUV) 工艺——也不足以在整个未来十年提供所需的位密度改进。因此,主要设备供应商和领先的 DRAM 制造商正在考虑将单片3D DRAM(相当于3D NAND的DRAM)作为长期扩展的潜在解决方案。根据Yole推测,这种新颖的3D技术可能在2029-2030年期间进入市场。不过,在此之前,该机构预计混合键合系统开始渗透DRAM设备市场,用于制造3D堆叠DRAM,例如高带宽内存 (HBM),可能从 HBM3+ 代开始。

HBM(High Bandwidth Memory,高带宽内存)是一种新型的CPU/GPU 内存芯片,其实就是将很多个DDR芯片堆叠在一起后和GPU封装在一起,实现大容量,高位宽的DDR组合阵列。 高速、高带宽HBM堆栈没有以外部互连线的方式与信号处理器芯片连接,而是通过中间介质层紧凑而快速地连接,同时HBM内部的不同DRAM采用TSV 实现信号纵向连接,HBM具备的特性几乎与片内集成的RAM存储器一样。

目前,在HBM芯片技术积累方面,SK海力士与三星在业内领先。例如SK海力士于2014年在业界首次成功研发HBM1,至2022年其HBM3芯片已向英伟达供货。

根据SK海力士有关异构集成半导体封装技术资料的介绍,在堆叠竞争时期,SK海力士的CoC(Chip-on-Chip,芯片内建芯片)技术表现尤为突出,这项技术将凸块互联 (Bump Interconnection)与引线键合(Wire Bonding)相结合,在提高运行速度和降低成本方面实现了突破。如今,该技术已专门应用于SK海力士高密度模块的生产和量产。

图3:SK海力士最新封装技术, 图片来源:SK海力士

图3:SK海力士最新封装技术, 图片来源:SK海力士

进入融合时期,SK海力士正积极发展混合键合(Hybrid Bonding)技术采用Cu-to-Cu(Copper-to-Copper, 铜-铜)键合替代焊接。SK海力士也在研究采用Fan-out RDL(Redistribution Layer,扇出型重新分配层)技术等各种封装技术方案。混合键合技术可以进一步缩小间距,同时作为一种无间隙键合(Gapless Bonding)技术,在芯片堆叠时不使用焊接凸块(Solder Bump),因此在封装高度上更具优势。此外,扇出型RDL技术适用于多个平台,SK海力士计划将该技术用于芯粒(Chiplet)技术为基础的集成封装。线间距(Line Pitch)和多层(Multi-Layer)是扇出型技术的关键组成部分,SK海力士计划到2025年将确保1微米以下或亚微米(Sub-micron)级水平的RDL技术。