全球首个符合ASIL-D的车规级Chiplet D2D互连IP流片

随着摩尔定律放缓,Chiplet SoC近年来被视为后摩尔时代推动下一代芯片革新的关键技术。芯片巨头AMD就凭借着在Chiplet上的投入,在过去几年大大拉近了与英特尔在数据中心处理器领域的差距。特斯拉引领了智能汽车电子电器架构由域内集成演变为跨域融合及中央计算架构。近期出现的AIGC促使汽车产业将智能化向更广泛的应用领域发展。智能汽车对算力需求的飙升使得行业迫切需要平台化计算硬件来实现降本增效,Chiplet异构集成技术无疑是打破后摩尔时代算力瓶颈的关键。全球多家车厂已经在使用Chiplet技术进行下一代芯片产品的研发,实现高性能、可拓展的芯片平台,从而覆盖不同车型、不同配置的算力需求。英伟达等芯片厂商最近也宣布了Chiplet在车载领域的一些战略部署。但Chiplet在车载领域的实践不是一蹴而就的,谁能拿出既满足车载大算力需求,又满足低成本,还满足车规要求,更能为客户创造差异化价值的芯片方案,谁才能够站在后摩尔时代半导体行业的舞台中心。

决定Chiplet产品性价比和可靠性的关键技术之一:Chiplet D2D片间互连技术

从理论上来说,Chiplet就像是搭建乐高积木,通过将单芯片拆分成若干个较小的裸片(Die),再将其互连并封装成一个异构集成芯片,从而达到甚至超越采用先进工艺芯片的性价比。但是具体到车载领域,Chiplet还面临着诸多挑战,其中芯片架构和互连方式是最需攻克的两大难关。其中芯片架构上的挑战在于:将原来在单芯片上所实现的功能拆分为多颗Chiplet共同去完成时,Chiplet之间(Die-to-Die,简称D2D)通信效率的降低会造成整体性能下降。如何找到最佳拆分方式,将性能下降控制在最低程度,是芯片架构设计的关键。而互连方式的挑战也同样在于:如何在满足市场对于成本、可靠性要求的前提下,尽量减少Chiplet D2D通信效率的降低。Chiplet D2D互连技术根据工作方式的不同主要可分为并行互连及串行互连,以下是两者的对比:

并行互连

先进封装:低延迟,高成本

并行互连不仅降低了两颗芯片之间的延迟,还可以通过增加总线宽度来提升带宽。然而,并行互连面临的现实瓶颈是制造成本偏高。究其原因,是因为并行互连的I/O连接线数量较大,需要依赖诸如CoWoS、InFO一类的先进封装技术,而这会导致成本的巨大提升,也对可靠性提出了更高的挑战。

串行互连

传统封装:高延迟,低成本

串行互连技术大大减少了芯片之间通信所需的I/O连接线总数,因此不需要依赖于先进封装,可以实现相对较低的成本,也相对比较容易实现更高的可靠性。但串行互连方式通常会引起额外约50-150 ns的延迟,不能满足实时性要求较高的应用需求。

在智能汽车这样一种对性能(尤其是实时性)、成本和可靠性都非常敏感的应用场景下,如果采用常见的串行互连方式及传统封装技术,虽然可以降低成本和可靠性风险,但显然在通信延迟性能方面又远达不到实时性要求;而如果采用所谓的先进封装技术实现并行互连,其高昂的成本和未经车规检验的可靠性等风险都会让人望而却步。在满足可靠性前提下,做好性能与成本之间的平衡,是Chiplet D2D互连方式的制胜关键。

为车载中央计算而生,芯砺智能独创Chiplet D2D互连IP流片

芯砺智能全自研的Chiplet D2D 互连IP兼有并行互连技术的高带宽、低延迟和串行互连技术的高可靠性、低成本的优势。该互连IP的端到端延迟小于5 ns,和片内总线延迟在一个量级,可以很好地支持不同处理器之间,以及处理器和存储器之间的低延迟互连的要求。另一方面,当前先进封装还未能完全符合车规要求,而芯砺智能Chiplet D2D 互连IP支持车规级传统封装,可以广泛应用于车载领域。

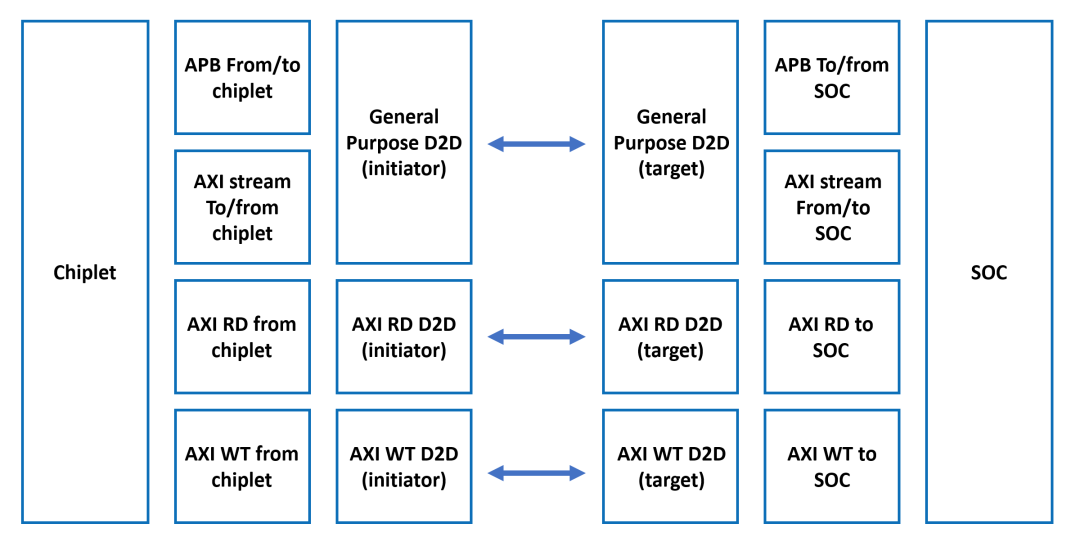

图1 Chiplet D2D 互连IP框图

芯砺智能的Chiplet D2D互连IP采用专利性的设计,通过一种用于片间互连的总线流水线性结构,做到了以较小的实际位宽来实现片间高带宽及低延迟的互连,从而可以摆脱对先进封装的依赖,用低成本的传统封装来实现片间互连。基于传统封装的Chiplet D2D互连技术更易于实现AEC-Q100的车规认证,从而达成高性价比、高可靠性的解决方案。

图2 芯砺Chiplet D2D核心优势:

并行性能,串行成本

得益于这些领先的设计,芯砺智能的Chiplet D2D互连 IP可广泛应用于各种需要高带宽、高可靠性、低延迟、低成本的应用场景,包括自动驾驶、高性能边缘计算、机器人、人工智能等领域。以先进的驾驶辅助系统和自动驾驶领域为例,这样的应用场景对系统的实时性和安全性有着非常高的要求。芯砺智能的Chiplet D2D互连 IP为这些系统提供了低延迟且高性价比的互连解决方案,可以加速信号处理流程,提高系统的反应速度。

本月初,芯砺智能全球首个符合ASIL-D功能安全等级的车规级Chiplet D2D互连IP流片。值得一提的是,该 IP所采用的核心技术已经获得了由美国专利及商标局(United States Patent and Trademark Office, USPTO)授予的独家专利,国内的专利认证流程也正如火如荼地进行着。

Chiplet D2D互连技术应用于车载领域的功能安全挑战:ASIL-D

对于汽车芯片,ISO 26262是一个不能绕过的关键标准。作为ISO 26262标准用于评估安全的等级,ASIL将汽车电子系统安全性能分为四个等级:ASIL-A、ASIL-B、ASIL-C 和 ASIL-D。其中,ASIL-D 表示最高安全等级。Chiplet D2D互连技术达到ASIL-D的级别确保能够满足复杂系统的安全性和可靠性要求。从失效影响角度,Chiplet D2D互连技术本身的失效会提升系统失效风险,而ASIL-D的Chiplet D2D互连技术可以完整覆盖互连的失效,极大的降低系统风险。此外,ASIL-D的Chiplet D2D互连技术可以应用到不同等级的安全域,而Chiplet D2D互连技术的纠错、重传机制更是可以有效提升系统的可用性。

达到ASIL-D级别的Chiplet D2D互连技术在设计、开发、测试和验证等方面都有非常严格的要求,这需要严格的安全管理体系、完备的安全架构分析和细致的安全技术实施等多方面能力的支撑。以下是达到ASIL-D安全等级的 Chiplet D2D互连技术的关键点:

安全分析和架构设计: 对Chiplet D2D互连技术的具体功能,失效模式和安全机制完整的分析是ASIL-D架构的基础。这需要IP架构师,安全架构师通过FTA,FMEA等方式对IP架构进行详尽的失效模式分析、影响分析,据此设计高覆盖率的安全机制,并通过FMEDA确认整体覆盖率(芯砺智能的Chiplet D2D互连 IP的SPFM=99.072%, LFM=90.641%)。此外,在架构设计时,不仅需要考虑高覆盖率的安全机制,也需要考虑安全机制对延迟、面积,验证,测试,易用性的影响,最终达成一个高效的IP架构。

故障后处理设计:IP若发生故障,系统通常需要进入复杂的故障恢复流程(系统重启等),从而导致系统在一段时间不可用,大大降低整体系统的可用性。为了提升整体系统的可用性,Chiplet D2D互连技术要具备高容错性,故障后处理需尽量考虑快速故障修复。在整个Chiplet D2D互连技术的架构中,需考虑多种纠错技术,包括ECC、重传等机制,并且和原有功能架构形成良好的耦合。

验证:Chiplet D2D互连技术的验证应经过仔细规划和验证。这涉及到总线、安全机制和故障后处理等多方面的协同验证。同时,也需要在各种不同的验证平台进行完备的故障注入测试,比如在RTL和门级仿真时候通过工具进行故障注入测试,在FPGA平台进行的软件故障注入测试,在流片回片后的互连故障注入测试等。

安全管理:ASIL-D的安全管理流程对于确保Chiplet D2D互连技术的安全性至关重要,这包含了完备的安全计划和每个安全活动的高质量完成。其中,每个安全要求应在安全计划中被清晰定义和记录,安全要求、设计和验证活动需被文档化,同时要确保安全活动中文档的可追溯性。

安全档案:完整的安全档案可以协助客户的产品顺利通过功能安全认证。这包括完备、规范的安全分析交付件(FTA/FMEA/FMEDA),完整、易用的安全手册,以及第三方权威机构认证证书。

今年6月初,芯砺智能Chiplet D2D 互连 IP获得了全球首个车规级ISO26262 ASIL-D Ready认证,该项认证标志着芯砺智能Die-to-Die Interconnect IP满足最高功能安全要求,可以应用在安全性要求最高的车载场景,是智能汽车算力平台芯片研发的重要里程碑,也开启了芯砺智能在智能汽车芯片市场的新阶段。

图3 ISO26262 ASIL-D Ready 认证

接棒后摩尔时代,赋能汽车“芯”生态

随着摩尔定律逼近极限,芯片设计日益复杂。芯砺智能认为,公司的Chiplet D2D 互连IP不仅为系统设计人员提供了一种灵活可扩展的互连方案,还可以帮助客户降低研发和系统成本、加速产品开发周期、提升敏捷迭代能力,并实现更强大的平台化产品开发能力。

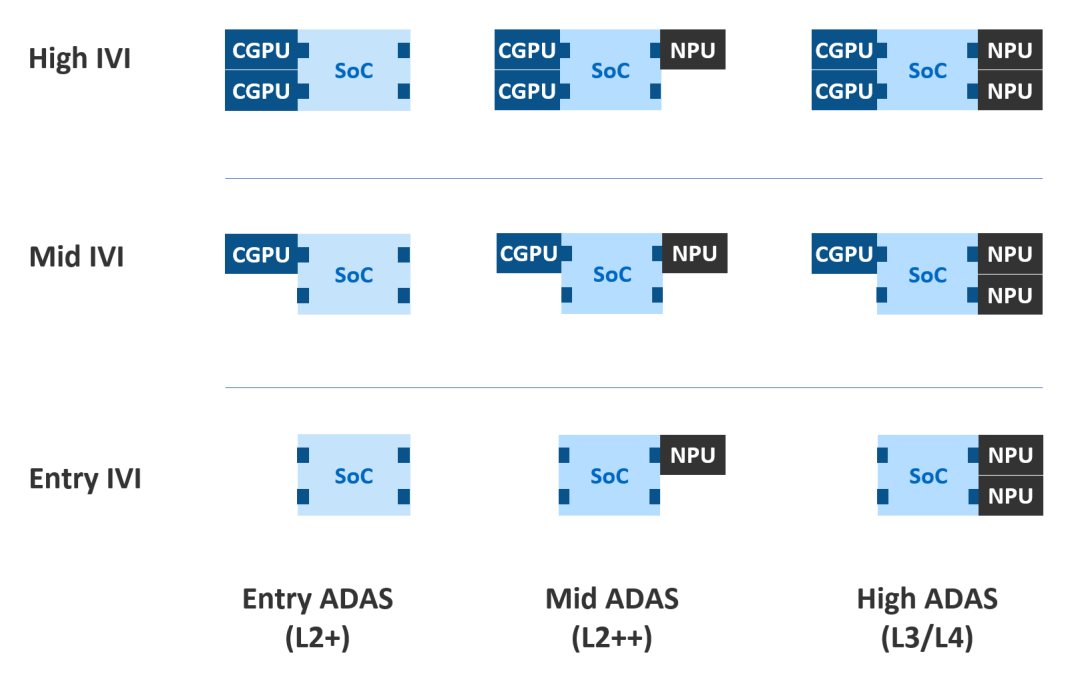

图4 Chiplet赋能:用一个平台覆盖多个应用场景

展望未来, 芯砺智能将与合作伙伴一同持续创新和突破,打造开放和共赢的生态圈,芯笃行远、砥砺前行,共创智能汽车辉煌芯世界。

本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。