大家好,我是小胡。在前面的内容我们讲国内六大CPU厂商的时候,发现了一个问题,就是国产CPU后续工艺迭代的问题。

本文引用地址:

除了华为鲲鹏以外,其余五大CPU厂商目前主力芯片的制程工艺都在10nm以上,而六大厂商当中有四家被列入实体清单,鲲鹏920虽然是7nm工艺,但这两年一直依靠库存支撑,芯片供应链问题一直是国产CPU无法回避的问题。

22年8月份之后,技术,也就是芯粒技术在A股市场中热度升高,我在看券商研报的时候发现,“超越”、“性能升级”、“弯道超车”、“产业突破”成为了研报当中的关键词。

今天我们就来跟大家聊聊芯粒技术,并挖掘A股相关的投资机会。

:后摩尔时代关键技术

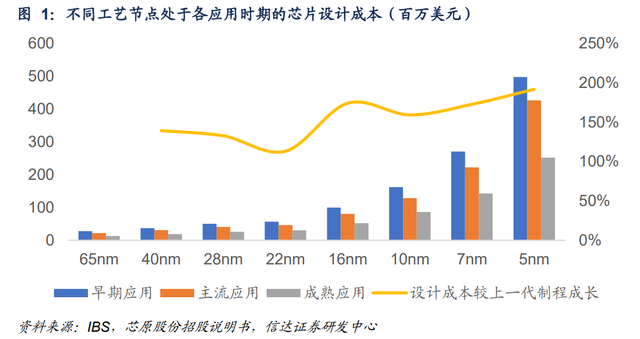

当推进到28nm以下的时候,每百万门的造价下降并不明显,甚至14nm单位晶体管的成本较28nm还略有上升。

而芯片的设计成本到28nm以下成倍地增加,这就导致工艺升级对芯片性能提升的边际收益缩窄,通常只有15%左右,也就是后摩尔时代经济效能提升出现了瓶颈。

技术就是在这个时候被美满科技得创始人周秀文博士提出来的,它的核心是降本增效。

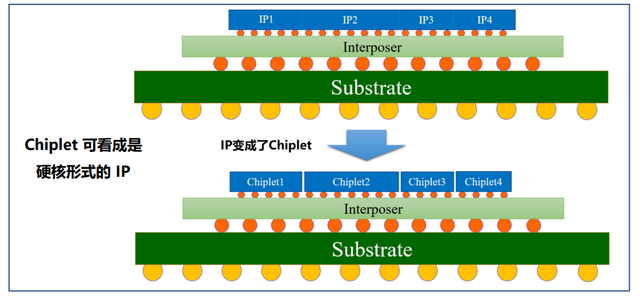

我们看传统SoC技术与Chiplet技术的对比,传统SoC芯片是把不同的IP核用相同的工艺制造在同一块晶圆上面,比如CPU、内存、显示控制这些模块都是7nm。

而Chiplet技术是在设计时就把不同IP核分开设计,按照需求选择合适的工艺分别制造,比如CPU用7nm,内存用14nm,显示控制用28nm。

最后再通过先进封装技术将各个单元彼此互联,最终集成封装成一个系统级芯片组。

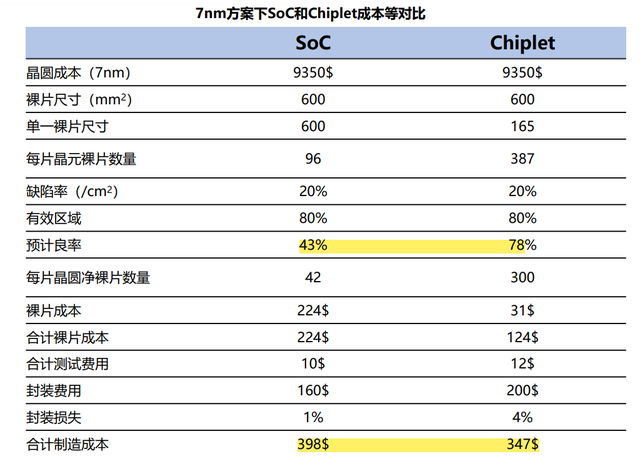

Chiplet有三大优势,首先是高良品率,SoC是大芯片,裸片的面积大,出现一点缺陷一大块都废掉了,Chiplet是多颗小芯片分开制造,将裸片的面积做小,能大幅提高良品率。

其次是Chiplet具有高设计弹性,SoC芯片采用统一的制程工艺,导致芯片上各个IP核需要同步迭代,而Chiplet芯片采用先进封装工艺,由小芯片组合构成,可以对芯片上部分模块进行选择性地迭代,研发周期更短,节省研发投入。

最后是低成本,在7nm相同方案下,Chiplet的良品率比SoC提高将近一倍,而成本下降了13%。

综合来看,Chiplet相较传统SoC具有多方面的优势,既降低了成本,又提高了经济效益,是后摩尔时代的发展趋势。

那么到这里就可以回答很多人的疑问,Chiplet能不能让国产芯片弯道超车?

答案是不能。

超大芯片与先进制程最受益Chiplet技术,国内主要产线均是成熟工艺,成熟工艺大芯片分小芯片制造,甚至用更落后的工艺制造的话,达不到降本增效目的,反倒可能增加成本,因为落后工艺单位晶体管成本本就偏高。

其实华为在19年推出的鲲鹏920芯片当时就用到了Chiplet技术,性能优异;国产芯片制造技术的提升,解决供应链问题,还是得依靠自主、先进的设备、材料,与晶圆厂共同推进,制造工艺的进步目前看没有捷径。

不过,Chiplet技术给我们带来了新的投资机遇。

先进封装迎新机遇

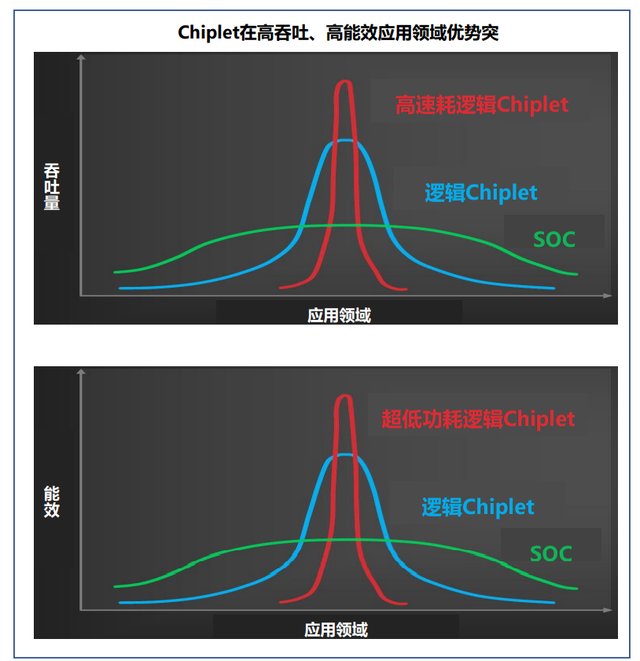

从Chiplet芯片需求来看,主要应用于服务器、高端智能手机和笔记本电脑。

从空间来看,机构预测Chiplet市场将在2024年达到58亿美元,并以每年31.5%的年复合增速,在2035年达到570亿美元,10年10倍,目前Chiplet处于发展初期,未来的增速很快,有望重新拉动封测行业增长。

Chiplet实现的核心是先进封装,用先进封装把小芯片“合”好,但光有先进封装也不行,还需要上游设计和中游制造把大芯片“分”好,上下游协同,我们主要看好先进封装及芯片测试相关的公司。

全球来看,具有前道工艺的代工厂或IDM企业在先进封装技术研发与产业化方面具有技术、人才和资源优势,利用前道技术的封装技术逐渐显现,目前支持Chiplet 技术的主流底层封装技术主要由台积电、ASE、Intel主导。

目前可用于Chiplet封装解决方案主要是SIP、2.5D和3D封装技术,其中,2.5D封装技术发展已经非常成熟,并且广泛应用于FPGA、CPU、GPU等芯片当中,近年来,随着Chiplet架构的兴起,2.5D封装成为了 Chipet 架构产品主要的封装解决方案。

为了节省芯片面积,未来,封装也将从2D/2.5D转向3D 叠,3D封装能够实现芯粒间的堆叠和高密度互联,可以提供更为灵活的设计选择,但是,3D封装的技术难度也更高,目前主要英特尔和台积电掌握3D封装技术并实现商用。