本篇应用说明介绍了RL78族有关噪声的注意事项及其对应方法。本应用说明中介绍的噪声对应方法仅作为通常的噪声处理方法,在实际使用时,请在实施本处理方法后对系统进行详细的评价。

本文引用地址:目录

1. 噪声的相关注意事项

1.1 缩短布线长度

1.1.1

![]()

引脚的布线

1.1.2 时钟输入/输出引脚的布线

1.2 在VSS-VDD之间连接旁路电容器

1.3 模拟输入引脚的布线处理

1.4 对谐振器的考虑

1.4.1 避开有大电流流过的信号线

1.4.2 避开有高速电平变化的信号线

1.5 输入/输出端口的处理

1. 噪声的相关注意事项

1.1 缩短布线长度

电路板上的布线可能会成为接收噪声信号的天线。因此,总的布线长度越短(mm单位),将噪声信号引入单片机内部的可能性就越低。

1.1.1 ![]() 引脚的布线

引脚的布线

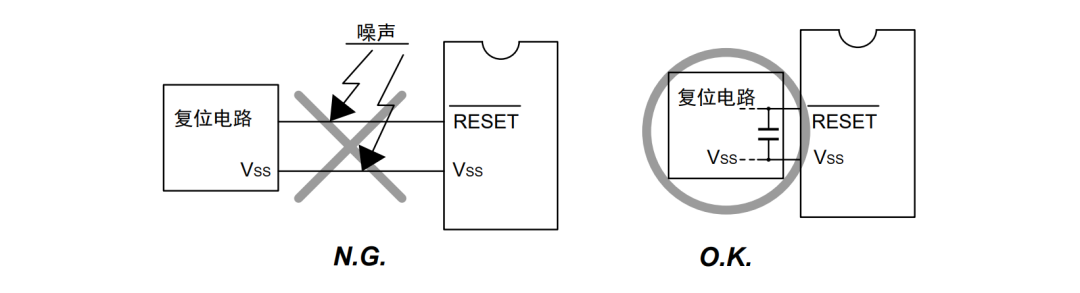

要尽量缩短连接![]() 引脚的布线。特别是在

引脚的布线。特别是在![]() 引脚与VSS引脚之间连接电容时,以及复位集成电路与对应的引脚连接时,一定要以最短的布线(20mm以内)连接。

引脚与VSS引脚之间连接电容时,以及复位集成电路与对应的引脚连接时,一定要以最短的布线(20mm以内)连接。

<理由>

输入到![]() 引脚的复位信号的脉冲宽度要求有一定的时序,如果短于正常复位脉冲宽度的干扰信号输入到

引脚的复位信号的脉冲宽度要求有一定的时序,如果短于正常复位脉冲宽度的干扰信号输入到![]() 引脚,那么在单片机完成内部初始化之前复位被解除,导致程序失控。

引脚,那么在单片机完成内部初始化之前复位被解除,导致程序失控。

图1.1 ![]() 引脚的布线

引脚的布线

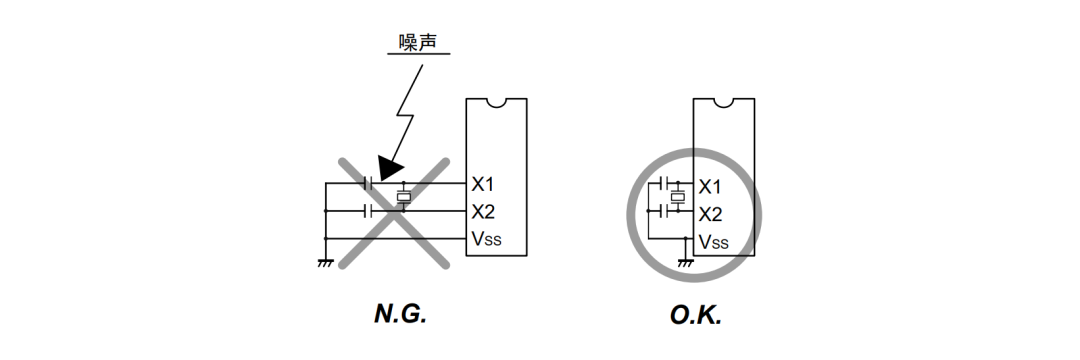

1.1.2 时钟输入/输出引脚的布线

• 要尽量缩短连接时钟输入/输出引脚的布线。

• 应该以最短的布线(20mm以内)连接谐振器电容的接地引线和单片机的VSS引脚。

图1.2 时钟输入/输出引脚的布线

<理由>

当有噪声干扰侵入时钟输入/输出引脚时,时钟的波形会发生紊乱,导致误操作和失控。另外,如果噪声使单片机的VSS电平和谐振器的VSS电平之间产生电位差,正确的时钟会无法输入到单片机。

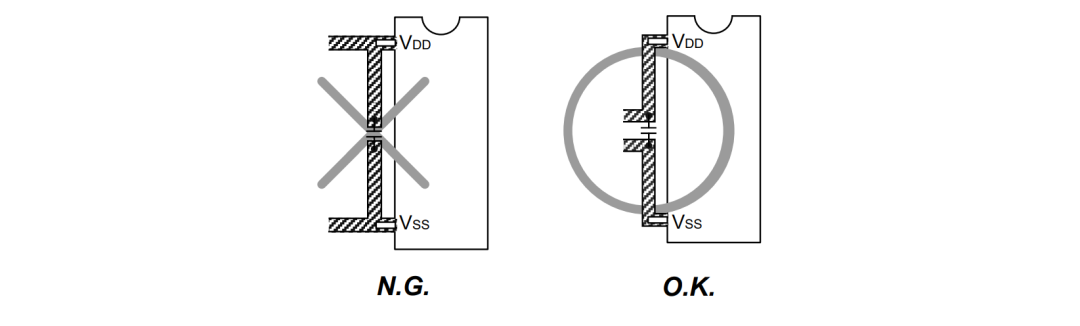

1.2 在VSS-VDD之间连接旁路电容器

请按照下列条件,在VSS-VDD之间连接0.1uF左右的旁路电容器。

• VSS引脚—旁路电容器的布线长度应该和VDD引脚—旁路电容器的布线长度相等。

• VSS引脚—旁路电容器的布线长度和VDD引脚—旁路电容器的布线长度一定要最短。

• VSS和VDD使用的布线要比其他信号线宽。

• 电源布线要经由旁路电容器连接至VSS引脚和VDD引脚。

图1.3 VSS-VDD之间的旁路电容器

1.3 模拟输入引脚的布线处理

• 请在模拟输入引脚连接的模拟信号线的尽可能靠近单片机的位置上,串联100~1kΩ左右的电阻。

• 请在模拟输入引脚与VSS引脚之间的尽可能靠近VSS引脚的位置上连接电容值在1000pF左右的电容。并且,模拟输入引脚至电容的布线长度应该和VSS引脚至电容的布线长度相等。

<理由>

一般来说,输入模拟输入引脚的信号通常都是从传感器传出来的。而用于检测运行情况的传感器,多数都设置在远离安装了单片机的电路板的位置,因此它与模拟输入引脚之间的布线必然会变长。由于较长的布线会成为接收噪声信号的天线,所以模拟输入引脚很容易接收噪声。

图1.4 模拟信号线、电阻及电容

1.4 对谐振器的考虑

谐振器生成的时钟信号是单片机运行的基础,因此要采取措施使谐振器不易受到其他信号的干扰。

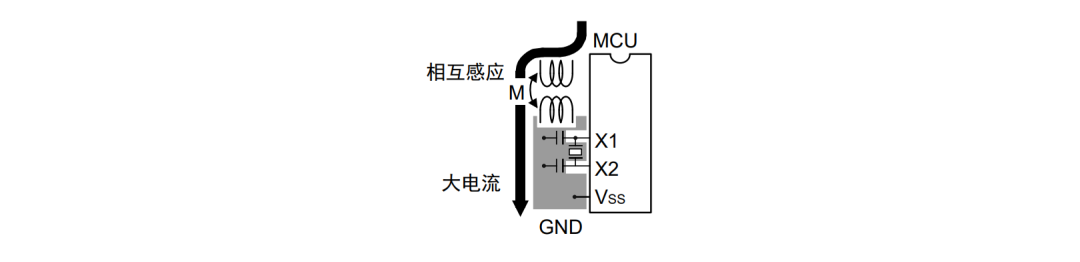

1.4.1 避开有大电流流过的信号线

如果信号线中流过的电流值超过了单片机所能处理的电流值范围,则需要将其设置在距离单片机(特别是谐振器)尽可能远的位置。

<理由>

单片机系统中分布着许多用来控制电机、LED和热敏头的信号线。当这些信号线中流过大电流时,会因相互之间的感应而产生噪声。

图1.5 有大电流流过的信号线的布线

1.4.2 避开有高速电平变化的信号线

有高速电平变化的信号线要设置在尽可能远离谐振器和谐振器的布线区域。另外,有高速电平变化的信号线不能与时钟相关的信号线和其他容易受到噪声影响的信号线平行或交叉。

<理由>

有高速电平变化的如TO01引脚的信号在发生上升或下降的电平变化时,会给其他信号线带来干扰。特别是如果与时钟相关的信号线交叉,时钟波形会发生紊乱,导致误操作和失控。

图1.6 有高速电平变化的信号线的布线

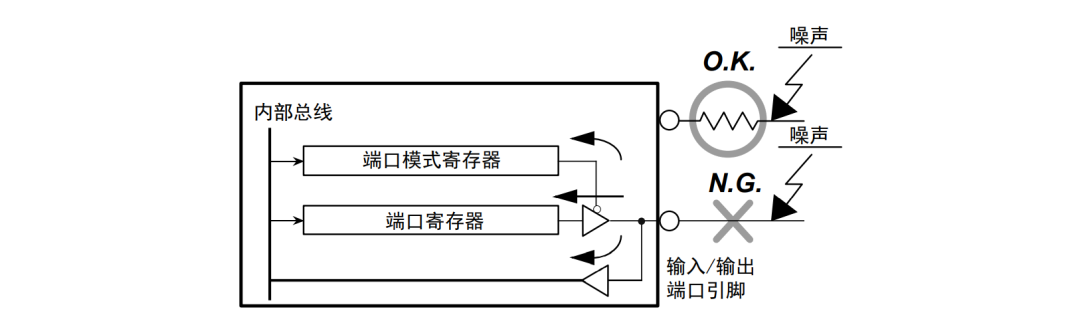

1.5 输入/输出端口的处理

输入/输出端口要按照以下要求,从硬件和软件两个方面进行处理。

硬件方面

• 要在连接输入/输出端口的信号线的尽可能靠近单片机的位置上串联100Ω以上的电阻。

软件方面

• 输入端口应通过程序反复多次进行读取,确定电平一致。

• 由于输出端口可能会因噪声的影响反相输出数据,因此每隔一定的周期就要进行端口寄存器的再写入。

• 每隔一定的周期进行控制端口功能的寄存器的再写入。

图1.7 输入/输出端口的处理