软件无线电的历史,意义与应用

说起软件无线电(software-defined radio,SDR),对于有些朋友来说可能显得奇怪,“无线电不是硬件吗,怎么又扯到软件了?”殊不知,软件无线电可以说是许多射频电路与系统从业者心中的终极目标。最近Xilinx发布了用于SDR的RFSoC,那么今天我们就来好好聊一聊SDR。

随着无线电的诞生,不同的无线通讯标准随之而来。不同的无线通讯标准通常工作在不同的频段,使用不同的协议,因此在早起无线电里需要专门的电路处理。随着无线电频段和标准越来越多,为了应付不同标准的射频系统也越来越复杂。那么,有没有可能用一种电路处理所有的无线通讯标准呢?SDR的概念应运而生,它早在1991年就由当时就职于E-Systems的Joseph Mitola在论文《Software Radio: Survey, Critical Analysis and Future Directions》中提出并广为人知,而Mitola本人也因为这篇论文成为了SDR领域教父级的人物。

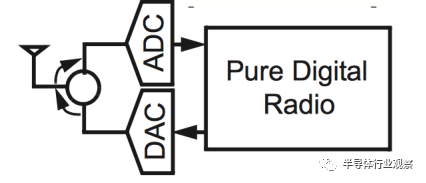

Mitola的SDR直接采样方案

Mitola的SDR架构很简单,在天线和射频前端器件后,接收机直接使用高速ADC把射频信号采样转换为数字信号,并把该数字信号送到数字基带处理器做处理。发射机也类似,数字基带处理器把信号在数字域上变频并送给高速DAC,DAC把数字信号转换为射频信号并驱动天线。

SDR系统的研究演进

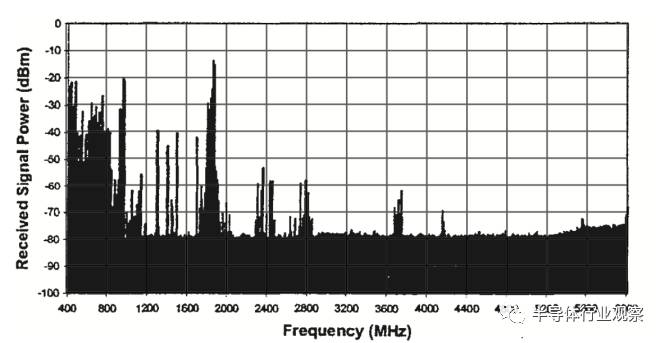

SDR系统看上去很简单,但是真正要实现起来非常困难,尤其是在90年代的时候。SDR中的接收机实现尤其困难。根据奈奎斯特采样定律,为了能够采集到载波频率在fc处的射频信号,ADC必须能工作在至少2*fc的采样频率。除此之外,对于接收机来说还有一重难点,就是射频信号强度大小不定,其强度变化的范围可以超过六到七个数量级,因此ADC的精度必须够高(10bit以上),否则无法采集到信号强度较弱的信号。最后,还存在blocker信号干扰的问题,因为接收到的射频信号强度差距可达好几个数量级,因此要求ADC的线性度非常好否则强的射频信号会把强度弱的射频信号淹没掉。

不同射频频段的频谱图

在90年代Mitola刚提出这个概念的时候,集成电路,尤其是CMOS集成电路实现SDR几乎是天方夜谭。那时候最流行的2G GSM标准工作在900MHz附近(因此需要1.8GHz的采样频率才能满足奈奎斯特定理),而ADC的采样频率非常慢。例如,拉扎维做的ADC,可以说代表了业界最前沿,1992年的时候他在ISSCC发表了12-bit 5MHz采样频率的ADC,而1999年他又在CICC发表了8-bit 150MHz采样频率的ADC。无论是5MHz还是150MHz,离1.8GHz来说都太远了。

Mitola的想法最初主要的资助方是美国国防部,因为军方对于SDR的需求更强烈而且可以不计成本使用最好的半导体工艺。到了21世纪初,即2005年前后,一方面随着摩尔定律CMOS电路能工作到越来越快,另一方面随着CMOS RF的兴起,SDR在商用领域也得到了各大公司的重视,不少大学和公司都开始投入SDR的研究。当时的ADC可以工作到10bit,500 MHz左右,但是主流3G通信已经开始用到了2GHz频段,因此使用直接ADC方案还是不行。那么,使用单独ADC直接采样不行,大家就想到了用一个比较折衷的方案,即设计一套接收机射频电路,可以通过配置覆盖很宽的载波频率范围。在同一时间,SDR接收机只工作在一个频段,但是可以通过软件配置在不同的时间工作在不同的载波频段。

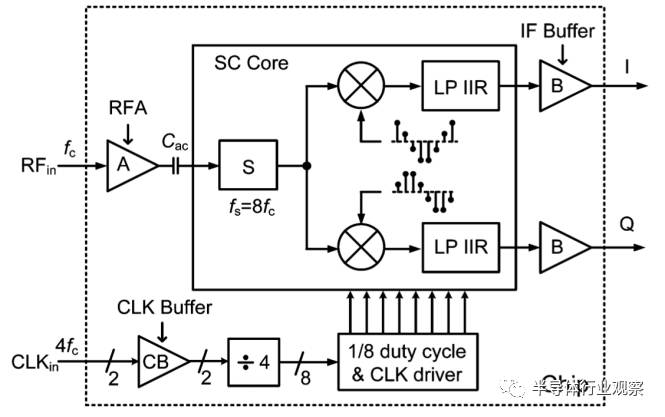

这个想法比起硬上ADC方案要简单不少,因此吸引了众多业界和学界人士投身其中。这套方案主要的挑战在于宽带可配置射频电路,而且需要在架构和电路层面上对噪声,线性度做优化。虽然困难重重,但是比起ADC直接采样方案来说还是有做一做的希望的。许多半导体业内的大佬都投入了SDR的热潮。在美国,有UCLA的Abidi提出了基于采样滤波器的方案。在欧洲,SDR研究也如火如荼,比利时鲁汶天主教大学和IMEC在ISSCC上给出了自己的方案,而荷兰屯特大学的汝嘉耘以及Eric Klumperink和Bram Nauta也提出了自己的采样接收机,使用崭新的charge-domain signal processing概念在SDR中做出了非常杰出和漂亮的工作。在工业界,ADI的SDR系统也是鼎鼎有名,使用可配置射频电路实现了能覆盖超大载波频率范围的可配置射频系统。

汝嘉耘提出的采样接收机架构

这样的SDR,不妨称之为单频段SDR,主要设计思路是一个射频系统不可能同时工作在多个不同频段,因此只需要能满足通过配置可以工作在不同频段即可。然而,随着2010年后4G通讯的兴起,载波聚合技术越来越重要。载波聚合需要射频系统同时在多个载波频段发射或接收信号,这意味着人们开始有越来越强的动力设计能同时工作在多个载波频段的射频收发机。这种SDR不妨称之为全频段SDR,因为需要它能同时工作在多个频段。全频段SDR中,使用ADC直接采样射频信号几乎不可避免,但好在此时ADC的采样频率已经上来了,工作在GHz的高精度ADC比比皆是,但是4G的载波频率最高主要还是在2GHz附近,相对于之前的3G没有太大变化。终于,2016年时Broadcom在ISSCC上发布了采样率4GHz,精度10bit的ADC,已经能满足全频段SDR的基本需求。只是Broadcom没有推出相应的SDR解决方案。

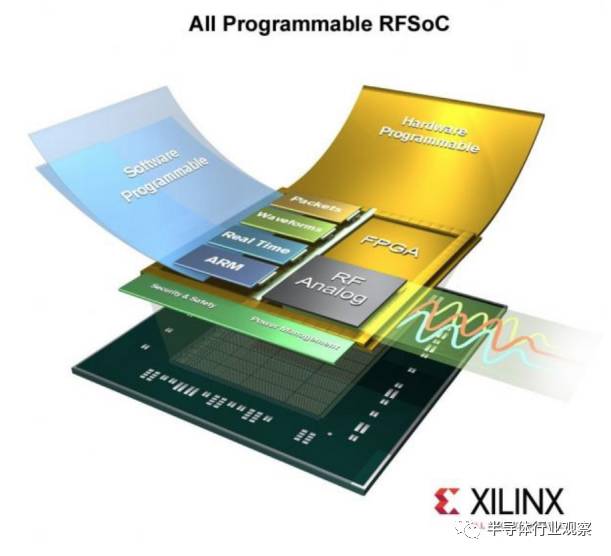

Xilinx的产品

Xilinx在SDR方面有着不少积累,但是主要是在使用FPGA实现的可重构数字基带方面。Xilinx FPGA实现的SDR基带以及相关软件在军方和业余无线电圈子里已经颇有名气。今年二月底,Xilinx又有些出人意料地推出了集成了超高速ADC/DAC的用于SDR的FPGA方案,称之为Xilinx All Programmable RFSoC。

在Xilinx的RFSoC中,ADC精度达到了12bit,而采样频率到达了4GHz,可以实现2GHz频段内的全频段SDR。DAC则可实现14bit精度,转换频率高达6.4GHz。配合Xilinx的FPGA用作数字基带处理器,一个完整的SDR电路系统就呼之欲出了。

第一个商用SDR系统被Xilinx抢先,而不是由Qualcomm,Broadcom等无线通讯业巨头拔得头筹(尤其是在Broadcom已经突破了SDR中最困难的ADC的情况下),确实让人有一些意外。然而,仔细想想还是在情理之中。首先,在过去的SDR研究中,大家都过于关心射频电路,但对于数字基带大家的关心并不多,总是觉得“设计出强大的数字基带处理器肯定没问题”。实际上,要实现能灵活配置的数字基带处理器并不容易,而FPGA以其可快速配置的特性目前不失为一种实现SDR数字基带处理器的选择。在FPGA方面,Xilinx的技术显然是遥遥领先的。另外,也是很关键的一点,就是目前全频段SDR仍未找到能马上落地的商用情景。虽然载波聚合需要工作在多个频段上,但是要全频段SDR的成本以及功耗比传统射频收发机更优,恐怕暂时还做不到。另一方面,在国防应用中,确实存在对全频段SDR的强烈需求,而且FPGA在军事应用中也是很常规的,因此由FPGA龙头Xilinx推出全频段SDR系统也是符合逻辑。

对中国半导体产业的启示

目前,中国半导体产业在射频电路与国外仍有一定差距,例如SDR中需要用到的超高速高精度ADC在中国仍然没有足够的技术实力实现,而更要命的是超高速ADC集成电路对于中国是禁运的。然而,除了在射频电路方面迎头赶上的同时,中国半导体业其实在SDR的其他方面也有机会填补空白。之前说的Xilinx 全频段SDR在电路方面已经接近理想,但是在片外射频前端器件方面,Xilinx仍然没有能力提供一整套方案。例如,SDR中如何实现天线,如何做片外功率放大器,仍然是空白。中国半导体行业在这些方面也有希望做一些有意义的事情,不仅为人类技术发展做贡献,也能提高我国在世界技术竞争中的话语权。

【关于转载】:转载仅限全文转载并完整保留文章标题及内容,不得删改、添加内容绕开原创保护,且文章开头必须注明:转自“半导体行业观察icbank”微信公众号。谢谢合作!

【关于投稿】:欢迎半导体精英投稿,一经录用将署名刊登,红包重谢!来稿邮件请在标题标明“投稿”,并在稿件中注明姓名、电话、单位和职务。欢迎添加我的个人微信号MooreRen001或发邮件到 jyzhang@moore.ren

【关于投稿】:欢迎半导体精英投稿,一经录用将署名刊登,红包重谢!来稿邮件请在标题标明“投稿”,并在稿件中注明姓名、电话、单位和职务。欢迎添加我的个人微信号MooreRen001或发邮件到 jyzhang@moore.ren