使用混合信号示波器时,您可能会遇到与检测相关的问题。这些问题体现在两类:探头负载和探头接地。探头负载问题通常会影响被测设备,而探头接地问题则会影响测量仪器数据的准确性。

探头的设计将第一个问题降到最低,而第二个问题可以通过积累检测经验来解决。

输入阻抗

逻辑探头是一种无源探头,提供高输入阻抗和高带宽。它们通常会给示波器提供一些信号衰减,通常为20 dB。

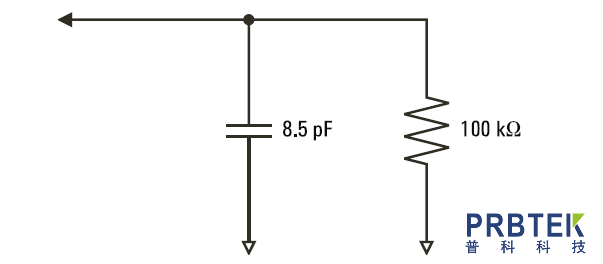

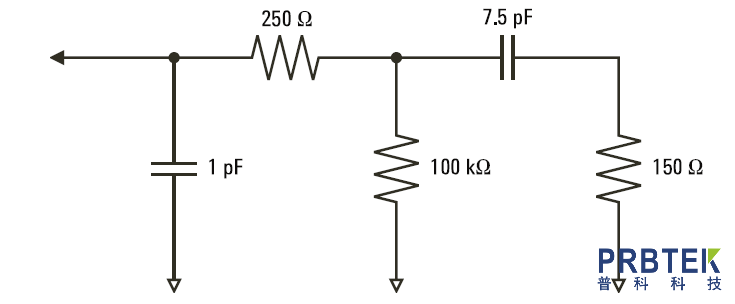

无源探头输入阻抗通常根据并联电容和阻抗来指定。阻抗是测试仪器的终端电阻值和输入阻抗之和(见下图)。它是电容补偿电容器和电缆加上仪表电容与杂散终端电容并联接地的串联组合。当这导致DC和低频输入阻抗规格的精确模型时,探头输入的高频模型更有用(见下图)。这个高频模型考虑了纯端接地电容和串联端阻抗,以及电缆的特性阻抗(Zo)。

和DC低频探头等效电路。

高频探头等效电路

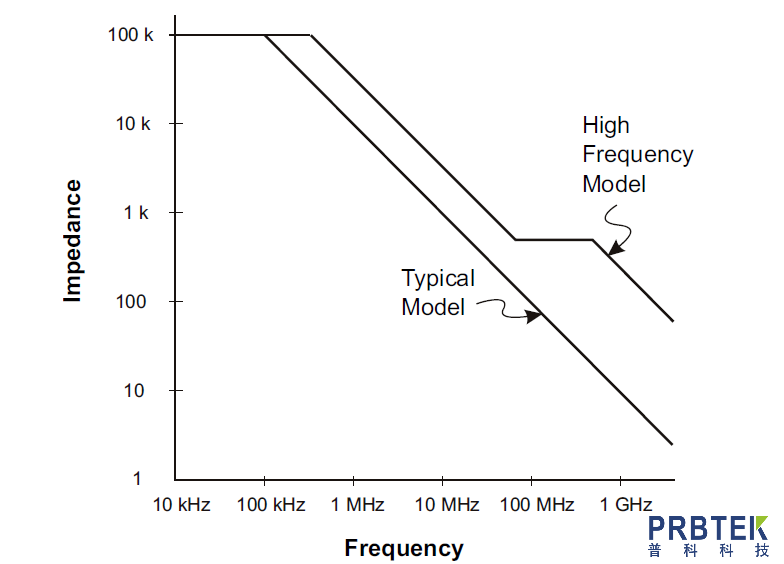

图中显示了两种型号的阻抗图。通过比较这两个图,可以看出串联端电阻和电缆的特性阻抗都明显扩大了输入阻抗。末端的杂散电容通常很小(1pF),最终断点设置在阻抗图上。

两种探针电路模型的阻抗和频率

逻辑探针由上面所示的高频电路模型表示。它们旨在提供尽可能多的串联端阻抗。通过探头端部组件的适当机械设计,杂散端接地电容将被最小化。这在高频时提供最大输入阻抗。

探针接地

探头接地是电流从探头返回电源的低阻抗路径。增加该路径的长度将在高频下在探头输入端产生大的共模电压。根据下式,产生的电压表现为路径是一个电感:

增加接地感应(L)、增加电流(di)或减少过渡时间(dt)都会导致电压增加(V)。当该电压超过示波器定义的阈值电压时,将会出现错误的数据测量。

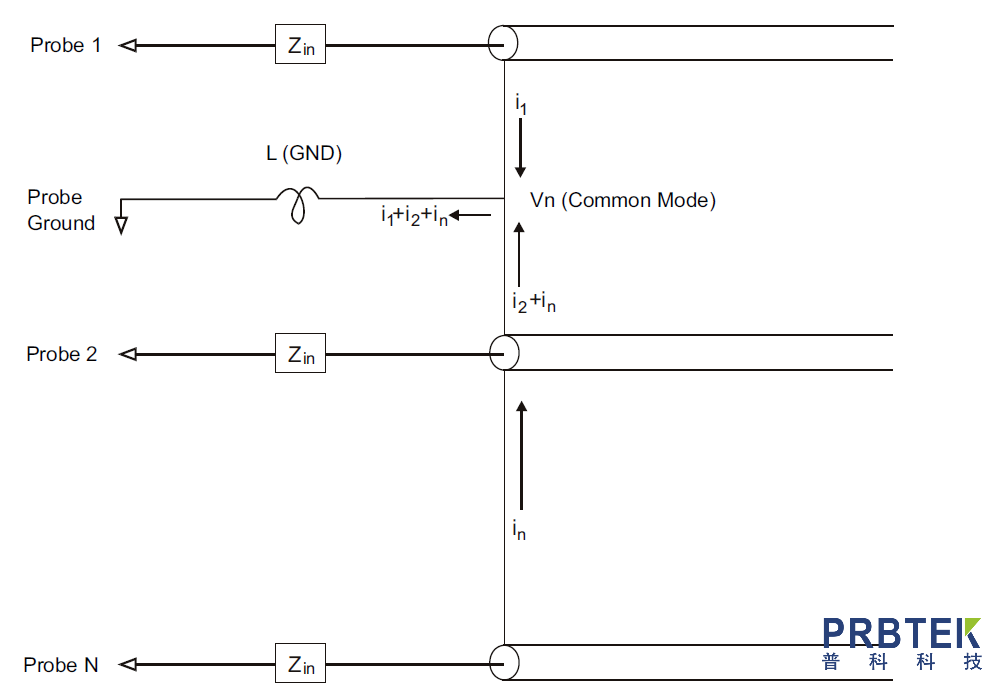

将一个探针与多个探针接地将迫使流向每个探针的所有电流在探针返回时流经该探针(其接地回路是共享的)。结果,在上述等式中,电流增加(di ),并且根据转换时间(dt ),共模电压可能增加到将产生错误数据的电平。

共模电压模型

除了共模电压之外,长接地回路也会降低探头系统的脉冲保真度。随着上升时间的增加,由于探头输入端的干LC电路,响铃振荡也会增加。因为数字通道显示重构的波形,所以它们不显示振铃和干扰。通过检查波形显示,你不会发现接地问题。事实上,通过杂乱的毛刺或矛盾的数据测量可能会发现问题。使用模拟通道查看振铃和干扰。

最佳检测习惯

由于变量L、di和dt,您可能不确定测量设置中有多少余量。以下是如何引导你养成良好的检测习惯:

如果组中的任何通道用于采集数据,每个数字通道组(D15–D8和D7–D0)的接地线应连接到被测设备的地。

在嘈杂环境中采集数据时,除了通道组接地之外,还应使用每三个数字通道探头的接地。

高速测量(上升时间< 3ns)应使用每个数字通道探头自己的接地。

设计高速数字系统时,应考虑设计一个直接面向仪器探头系统的专用测试端口。这将使测量设置更容易和可重复使用,以获得测试数据。