1、异步计数器

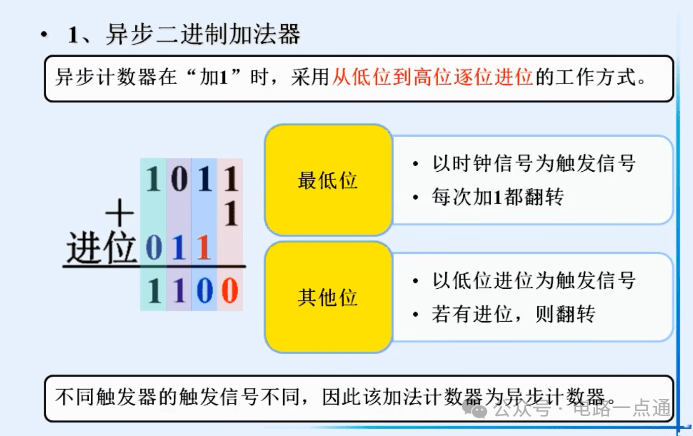

1、异步二进制加法器

1、原理

同步:在CLK到来时判断以往的状态是否需要翻转

异步:判断低位是否有进位来判断是否需要翻转

2、电路-下降沿触发

使用3个 下降沿 触发的T触发器构成异步计数器

CLK 0 的下降沿导致FF 0 翻转,若初始状态为000时,需要翻转两次,Q 0 才会产生下降沿,从而CLK i 的翻转频率逐级除以2

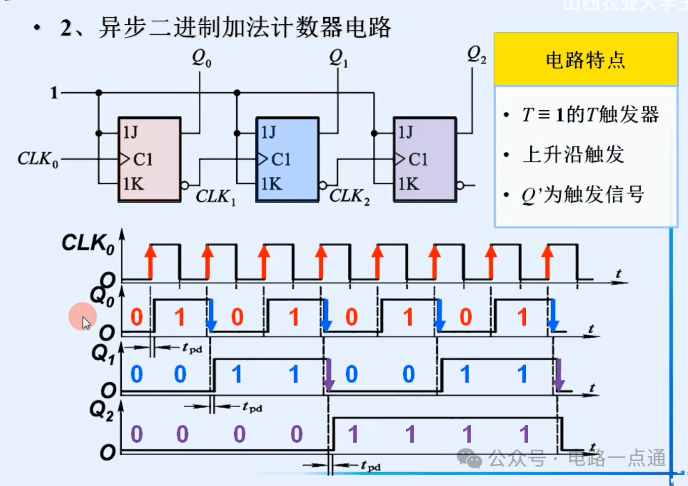

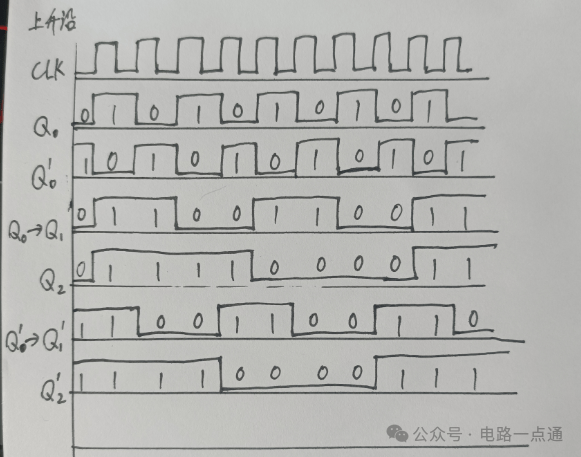

3、电路-上升沿触发

使用 上升沿 触发的T触发器构成加法计数器

因为初始状态为000,并且每个触发器是二进位,所以需要将Q’端接到CLK,使用Q’端的上升沿进行触发

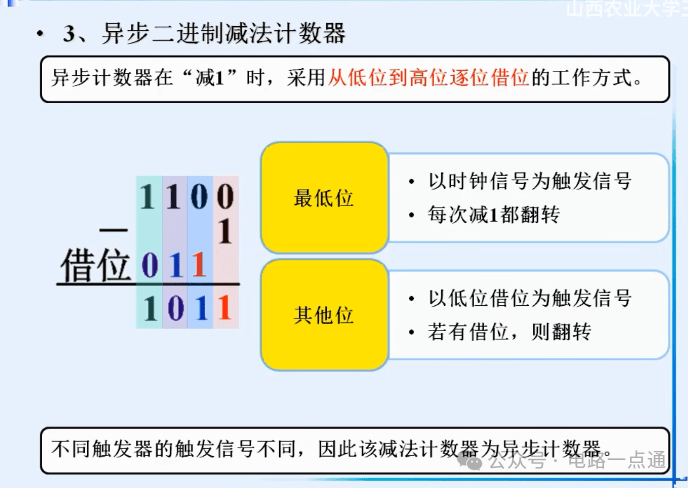

2、异步二进制减法计数器

1、原理

2、电路-下降沿触发

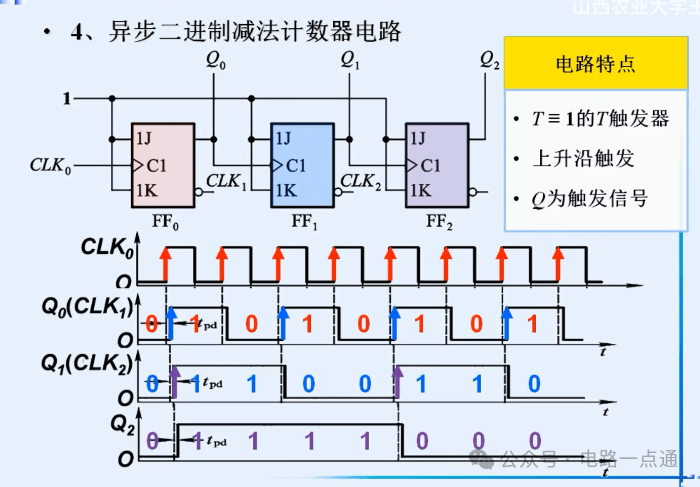

3、电路-上升沿触发

2.5、加减法电路连接规律总结

而上升沿Q端和下降沿Q’端就是减法计数器

连接Q还是Q’和上升沿和下降沿是可以两两组合的因素

但 连接Q时,Q是降序 Q’是升序;而 连接Q’时 ,Q’是降序 Q是升序

连接Q时,Q是升序 Q’是降序; 连接Q’时 ,Q’是升序 Q是降序

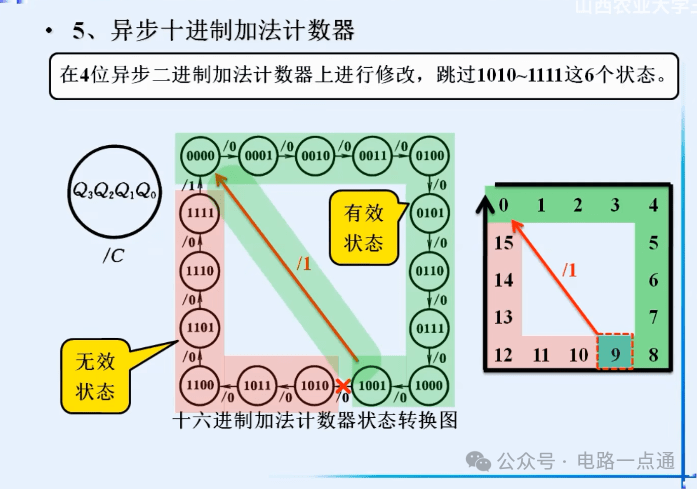

3、异步十进制加法计数器

1、状态

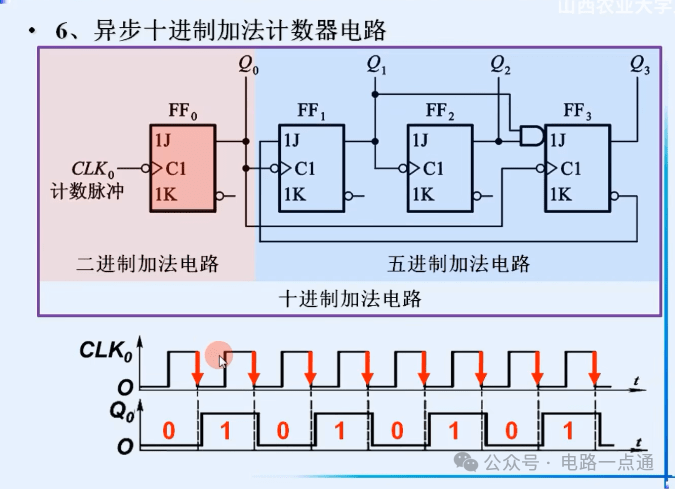

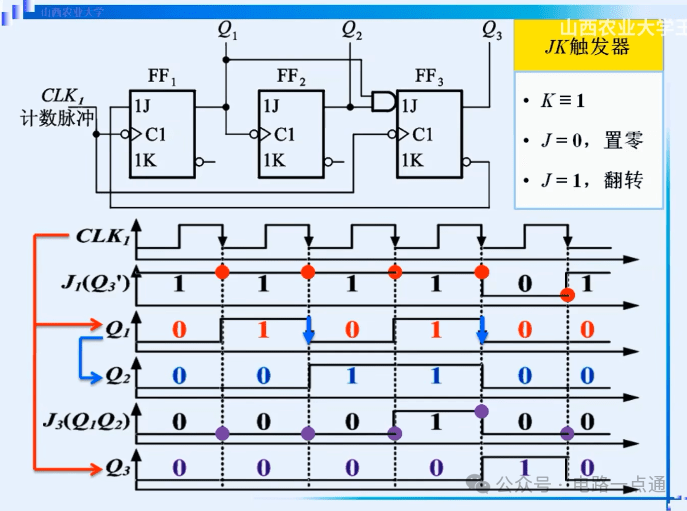

2、电路

分成2部分进行分析:

二进制加法电路:该JK触发器相当于T触发器,因为此时J=K=1。

每来一个CLK就进行翻转,相当于一个两位加法器

3、74LS290

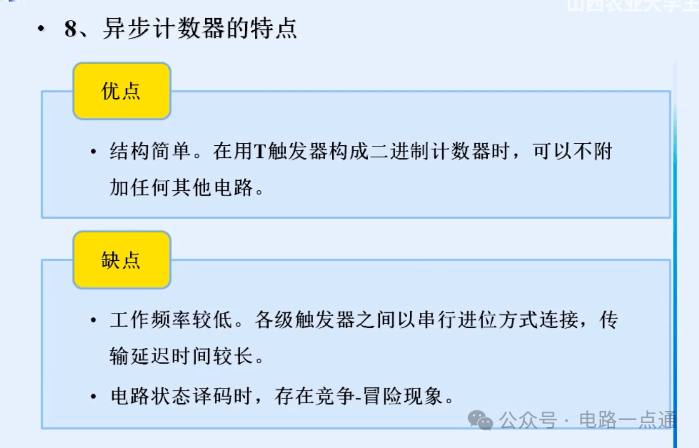

4、异步计数器特点

竞争冒险原因:因为异步,多个触发器先后进行状态改变,有延迟,例如001变为010状态,在FF0从1变为0时,FF1还处于0,此刻就会出现000状态。

由于延迟的关系,不会出现011的瞬时状态,该状态表示FF1先从0变成1,而FF0却还未改变。对于异步计数器而言,下一级FF i 的改变一定伴随着低一级FF i-1 的改变,并且时间上在低一级之后。

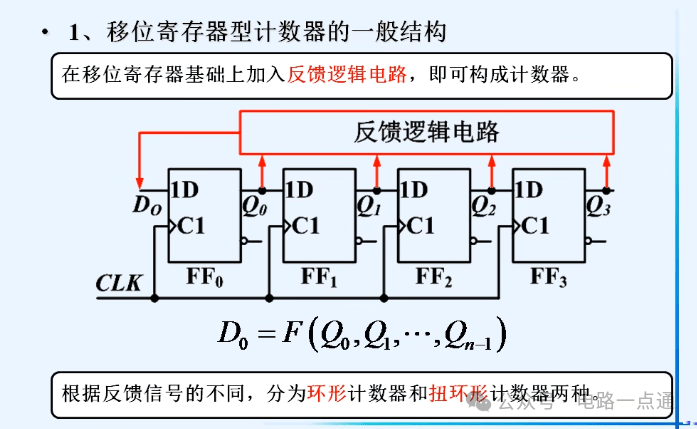

2、移位寄存器型计数器

1、一般结构

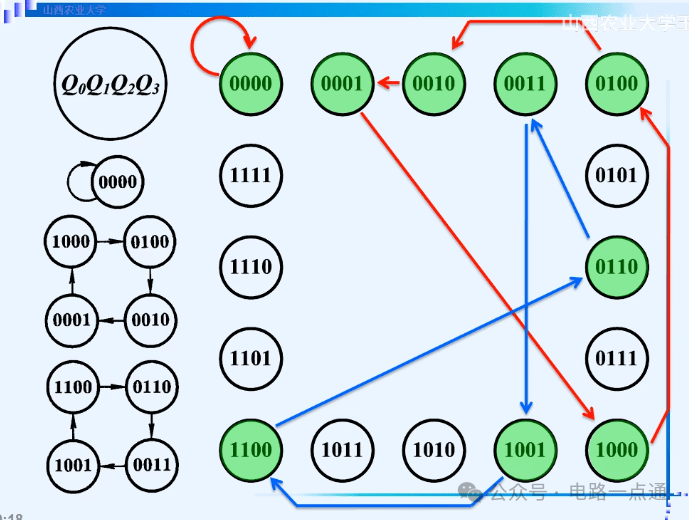

2、环形计数器

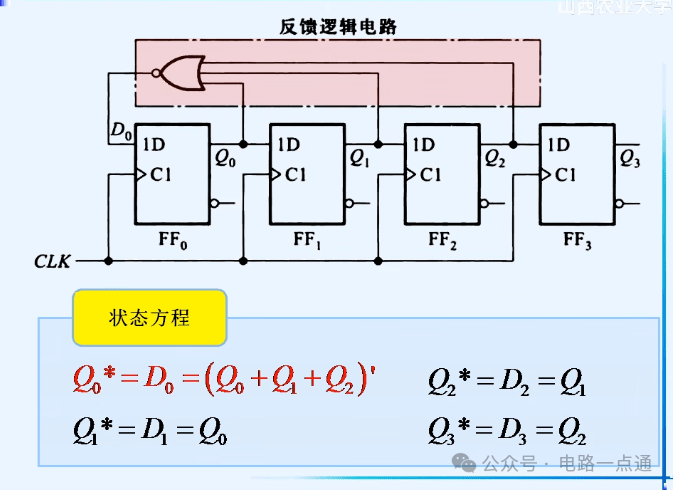

1、电路

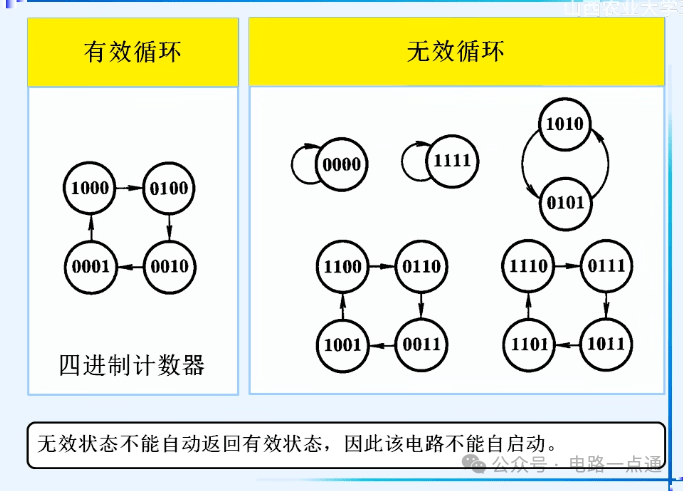

2、状态图

初始状态为

-

0000:移位过程中状态始终为0000 -

0001:4进制,有4个电路状态 -

0011:4进制,有4个电路状态 -

1111:移位过程中状态始终为1111 -

1010:2进制,有2个电路状态 -

1110:4进制,有4个电路状态

初始状态为:

初始状态为:

通常都要求电路能够自启动,所以需要修改电路

3、非启动->自启动

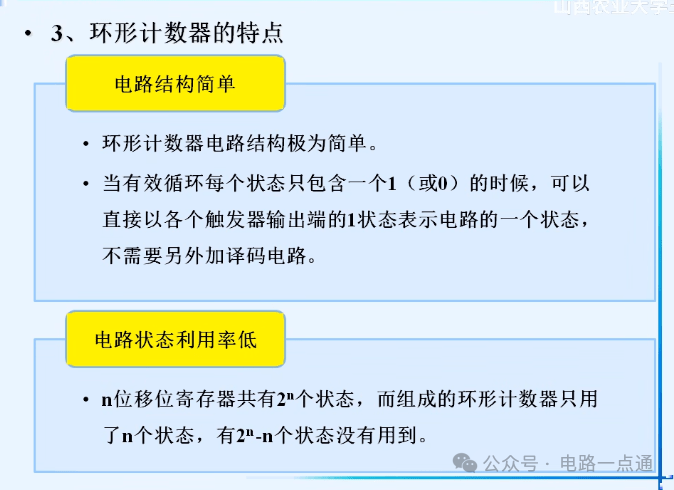

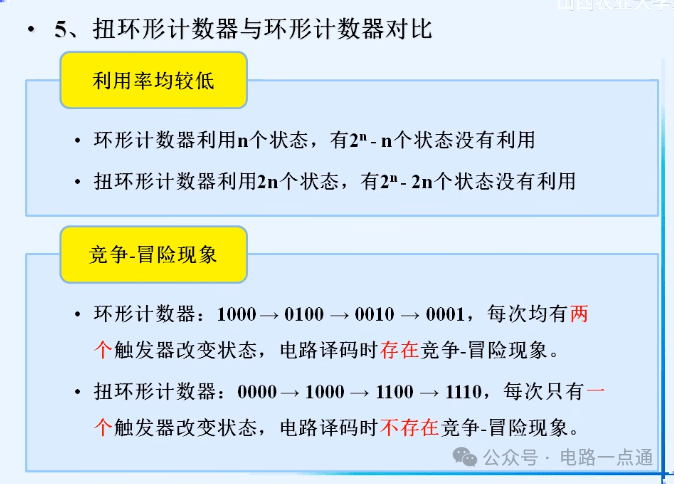

4、特点

例如上面的4进制计数器,4位移位寄存器有16个状态,最终却只用了4个状态

例如上面的4进制计数器,4位移位寄存器有16个状态,最终却只用了4个状态

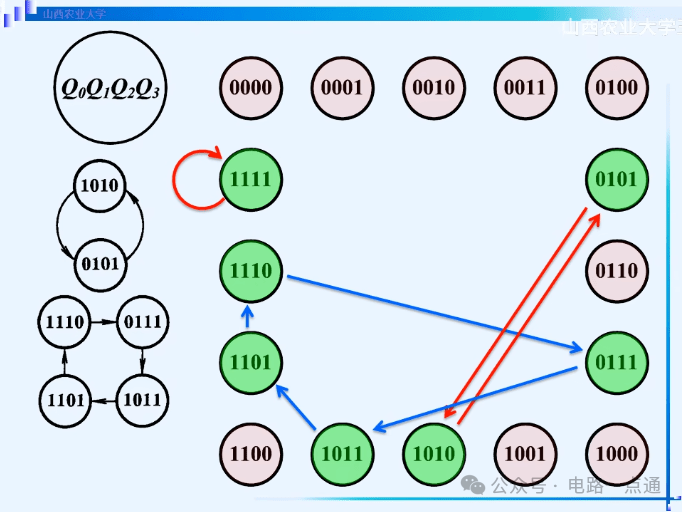

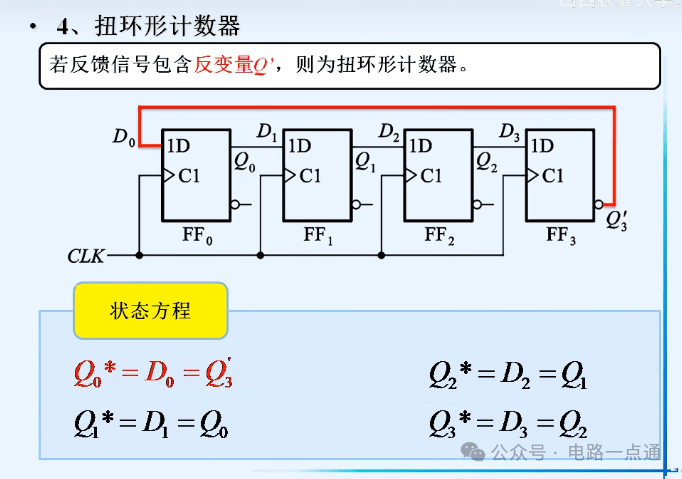

3、扭环形计数器

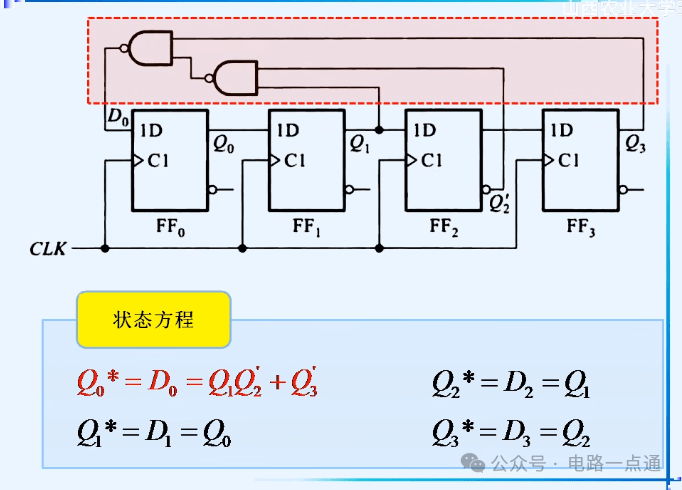

1、电路

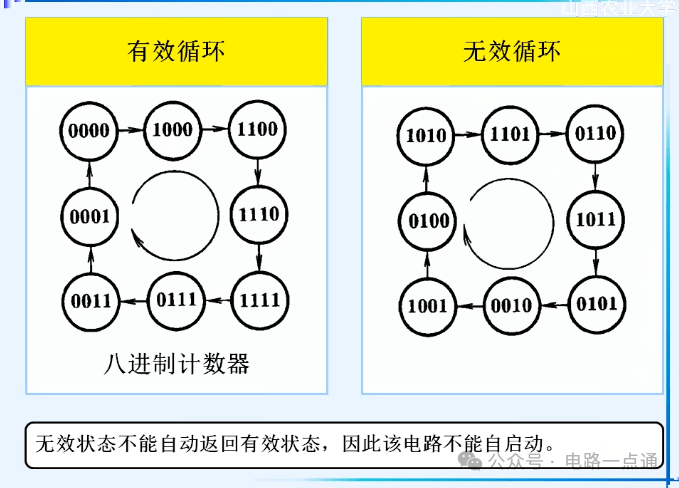

3、状态图

同样是8个状态都能自循环,为什么右边就是无效循环呢??

非自启-自启动

自启动状态图

4、对比

文章来源于:电路一点通 原文链接

本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关文章

可创建小型组合与时序逻辑电路的PLU可编程逻辑单元(2023-03-14)

可创建小型组合与时序逻辑电路的PLU可编程逻辑单元;在进行MCU开发时,有时需要用到一些简单的数字逻辑电路,LPC804与LPC55XX系列集成了PLU(Programmable Logic......

17个图解数字电路基础知识!!(2024-11-15 23:57:25)

、组合逻辑电路和时序逻辑电路数字电路可以分为组逻辑合电路和时序逻辑电路两种。

(1)组合逻辑电路组合逻辑电路是指输出值仅由输入信号的状态决定的电路......

FPGA设计必须注意的设计原则(2024-12-18)

信号都是由某个时钟沿驱动触发器产生出来的。

同步时序电路可以很好的避免毛刺。布局布线后仿真,和用逻辑分析仪采样实际工作信号都没有毛刺。

是否时序电路一定比异步电路使用更多的资源呢?

从单......

FPGA设计必须注意的设计原则(2024-12-18)

的。

异步时序电路的最大缺点是容易产生毛刺。在布局布线后仿真和用逻辑分析仪观测实际信号时,这种毛刺尤其明显。

同步时序

电路的核心逻辑用各种各样的触发器实现

电路......

STM32时钟电路(2024-11-15 11:28:50)

STM32时钟电路;

一、为什么需要时钟电路。

(1)单片机是一个集成芯片,其中包括

时序逻辑电路

,可以说,没有时序,就没有数字电路......

原理分享 | 单片机常用通信协议汇总(上)(2023-01-31)

帧格式

起始位:发送一位逻辑电平0开始传输数据

空闲位:当为高电平时,无数据传输

数据位:先发低位再发高位,传输8位数据

校验位:奇偶校验,1的位数为偶数(偶校验),1的位数为奇数(奇校验)

停止......

FPGA约束、时序分析的概念介绍(2024-01-04)

知道TINPUT,TINPUT为输入端的组合逻辑、网线和PAD的延迟之和,PAD的延时也根据器件型号也有典型值可选,但是到达输入端的组合逻辑电路和网线的延时就比较难以确定了,只能通过静态时序......

实验14:移位寄存器(2023-10-11)

实验14:移位寄存器;实验目的

(1)熟悉和掌握开发流程和软件使用方法;

(2)通过实验理解和掌握原理;

(3)学习用行为级描述时序逻辑电路。

实验任务

本实验的任务是设计一个7位右......

vivado时序异常分析(2024-12-19)

称作虚假路径。虚假路径在时序分析过程中应该被忽略不计。下面这些情况都属于虚假路径:

在有双同步器逻辑的地方有时钟域交叉

可能只在上电时写入一次的寄存器

复位或测试逻辑

异步......

实验16:扭环形计数器(2023-10-12)

实验16:扭环形计数器;实验目的本文引用地址:(1)熟悉和掌握开发流程和软件使用方法;

(2)通过实验理解和掌握原理;

(3)学习用行为级描述时序逻辑电路。

实验任务

设计一个右移。

实验原理

将移......

技术咨询

技术咨询 代买器件

代买器件 商务客服

商务客服 研发客服

研发客服