一、的功能

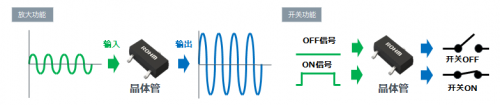

具有放大和开关电信号的功能。 比如在收音机中,会扩大(放大)空中传输过来的非常微弱的信号,并通过扬声器播放出来。这就是的放大作用。 另外,晶体管还能仅在事先确定的信号到达时才工作,这时发挥的是开关作用。 我们常听到的“IC”也好“LSI”也好,都是晶体管的集合体,是晶体管构成了其功能的基础。

本文引用地址:

【晶体管的基本功能示意图】

作为开关使用的晶体管

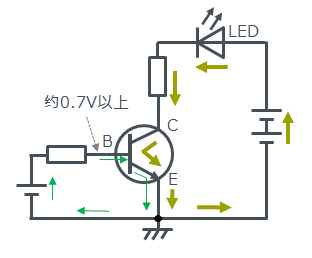

下面通过发射极接地时的开关工作来介绍起到开关作用的晶体管。

当晶体管的基极引脚被施加电压(约0.7V以上)并流过微小电流时,晶体管会导通,电流会在集电极和发射极之间流动。

反之,当施加到基极引脚的电压较低(约0.7V以下)时,集电极和发射极处于关断状态,电流不流动。

晶体管的开关工作就像使用基极作为开关来打开和关闭从集电极流向发射极的电流。

【开关导通示意图】

作为放大器使用的晶体管

下面通过比较自来水供水机制来介绍晶体管的功用。晶体管有三个引脚,分别是发射极、基极和集电极。基极相当于水龙头开关,发射极相当于水龙头出水口,集电极相当于水箱。用很小的力(向基极输入信号)控制水龙头开关,就会有大量的水从水箱(集电极)流向水龙头出水口(发射极)。通过这样的比喻来思考的话,可能更容易理解。

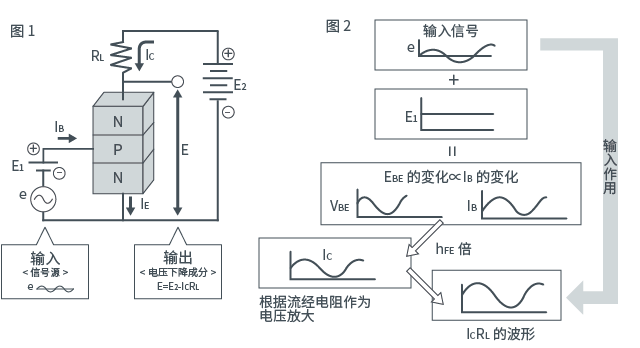

现在,我们使用图1和图2更详细地讲解一下晶体管的放大原理。流经集电极的电流是与输入电压e和偏置电压E1构成的基极-发射极间电压 (VBE)成正比的电流(IB)的hfe*1倍电流(IC)。随着该集电极电流IC流过电阻器RL,在电阻器RL两端出现IC×RL的电压。最终,输入电压e被转换(放大)为电压ICRL并在输出中体现出来。 ※1:hfe 晶体管的直流电流放大系数

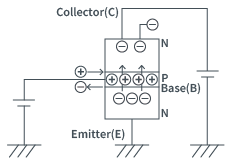

晶体管工作原理

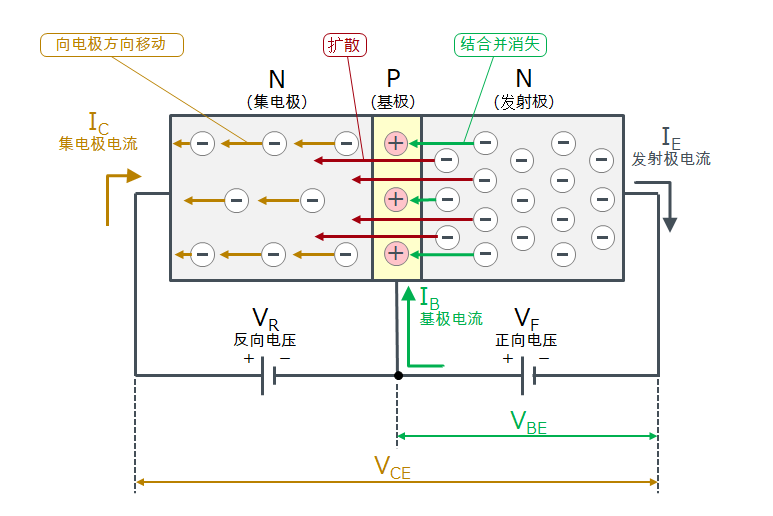

晶体管由PN结组成,通过在基极流过电流,而在集电极-发射极间流过电流。

在这里,以NPN晶体管为例来说明其工作原理。 当在基极和发射极之间施加正向电压(VBE)时,发射极的电子(负电荷)流入基极,部分电子会与基极的空穴(正电荷)结合。这就是基极的微小电流(IB)。 基极(P型半导体)在结构上很薄,从发射极流入基极的大部分电子会扩散到集电极。

电子(负电荷)被集电极-发射极间电压(VCE)吸引并向集电极的电极方向移动。这就是集电极电流IC。 <电流方向与电子移动方向相反>

【晶体管工作示意图(NPN型)】

NPN和PNP晶体管

晶体管大致可以分为“NPN”和“PNP”两种类型。从右图中也可以看出,主要是根据集电极引脚侧在电路中是吸入还是输出电流来区分使用晶体管。

如果想根据输入信号进行开关,那么使用NPN型晶体管,发射极接地。如果想在电源侧进行控制,则通常使用PNP型晶体管。

NPN型晶体管的载流子是电子(负电荷),而PNP型晶体管的载流子是空穴(正电荷)。在PNP型中,通过施加电压使发射极为正电压,基极为负电压,使发射极空穴(正电荷)流入基极,其中一部分与基极电子(负电荷)结合,产生微小的基极电流,其余部分扩散到集电极并成为集电极电流。

【NPN型和PNP型晶体管】

晶体管的历史

1、晶体管于1948年诞生于贝尔实验室

1948年发明了晶体管,这对当时的电子工业界带来了巨大的冲击。 正是那时拉开了当今电子时代的帷幕。此后,包括计算机在内的电力电子技术得到了飞速发展。从对我们的生活带来如此巨大的贡献来看,贝尔实验室的三位物理学家约翰·巴丁(John Bardeen)、沃尔特·布拉顿(Walter Brattain)、威廉·肖克利(William Shockley)获得诺贝尔奖可谓是当之无愧。 之后的发明,还有什么能与晶体管相匹敌呢?无论如何,晶体管对当今时代产生了巨大的影响。

2、从锗到硅

晶体管最初是由一种叫做“锗”的物质(半导体)制成的。 然而,锗具有在80℃左右时会损坏的缺点,所以现在大多采用硅材质。顺便提一下,硅是一种可以承受约180℃高热的物质。

二、概述

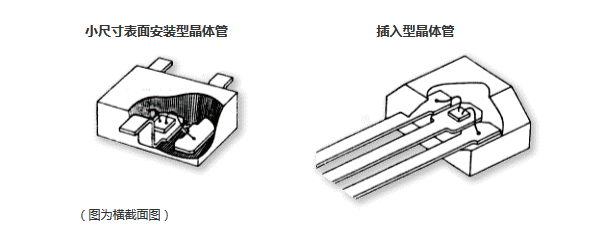

晶体管的代表形状

晶体管分类图:按照该分类,掌握其种类

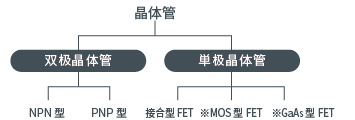

1、按结构分类

根据工作原理不同分类,分为双极晶体管和单极晶体管。

双极晶体管

双是指Bi(2个)、极是指Polar(极性)。双极晶体管,即流经构成晶体管的半导体的电流由空穴(正极性)和电子(负极性)产生。一般而言的晶体管是指这种由硅构成的晶体管。

FET

Field Effect Transistor的简称,是指场效应晶体管。有接合型FET和MOS型FET以及GaAs型。

接合型FET多用于音频设备等的模拟电路中,MOS型FET主要用于微控制器等数字IC。

GaAs型用于卫星广播信号接收等的微波增幅。

※MOS

Metal Oxide SemicONductor的简称,因其构造分别是金属 (Metal)、硅酸化膜 (Oxide)、半導体 (SemicONductor),故称MOS。MOS还分为P型、N型、C型,因为消费电流小,用于微控制器等集成度高的IC。

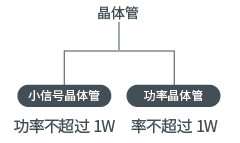

2、按功率分

主要以最大额定值的集电极功率PC进行区分的方法。大体分为小信号晶体管和功率晶体管,一般功率晶体管的功率超过1W。

小信号晶体管

最大集电极电流 (IC(max)) 在500mA以下,最大集电极功率 (PC(max)) 不超过1W的晶体管。相对功率晶体管而得名,一般以树脂封装居多,这是其特点之一。

功率晶体管

一般功率晶体管的功率超过1W。相比小信号晶体管拥有更大的最大集电极电流、最大集电极功率,对于散热而言,它本身形状就很大 ,有的功率晶体管上还覆盖着金属散热片。

晶体管“一词由Transfer(传送信号)和Resistor(电阻器)组成。构成晶体管的硅是形成地球的岩石中大量含有的物质。因此,晶体管也俗称”石“,设计者常用”…之石“的叫法

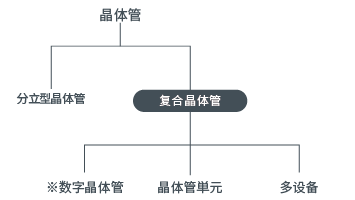

3、按集成度分类

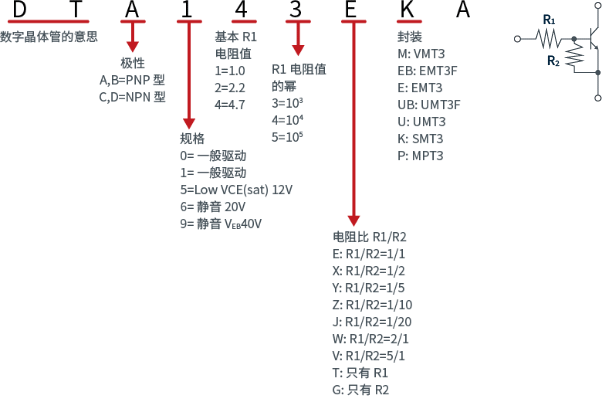

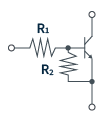

为满足客户需求,ROHM在分立式晶体管以外,还制造集成多个晶体管的复合晶体管。包括内置电阻的数字晶体管、集多个晶体管于一体的晶体管阵列,还有构成简单电路的晶体管单元。

※数字晶体管

内置电阻的晶体管。它是在电路设计中将频繁使用的部分标准化的产物。

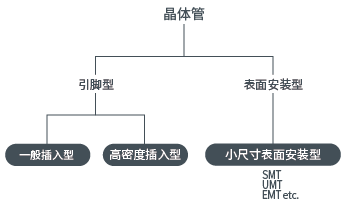

4、按形状分类

根据功率及安装形态,决定了晶体管的外形大小和形状。大体分为引脚型和表面安装型。

三、晶体管

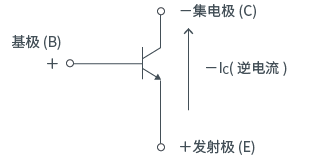

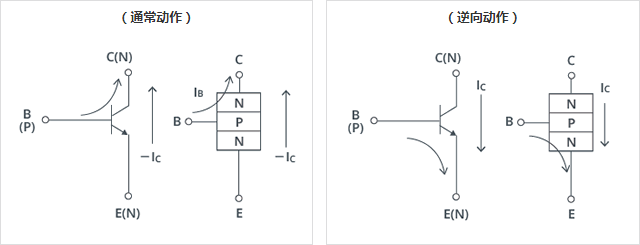

关于晶体管ON时的逆向电流

1、不用担心劣化和损坏,在使用上是没有问题的

1、不用担心劣化和损坏,在使用上是没有问题的

2、NPN-Tr的B和C对称、和E极同样是N型。

也就是说,逆接C、E也同样有晶体管的功效。即电流由E→C流动。

3、逆向晶体管有如下特点。

↑通用TR的情况,除此之外,还有5V以下 (突破此耐压范围,会发生hFE低下等特性的劣化,请注意。)

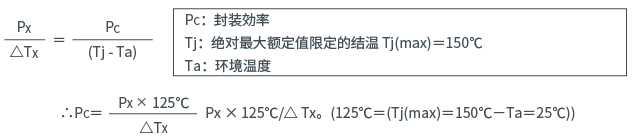

关于封装功率容许功

定义:是指由于输入晶体管的电压、电流产生的功耗在元件发热时,结温Tj为绝对最大额定值限定的温度(Tj=150°C)时的功率。

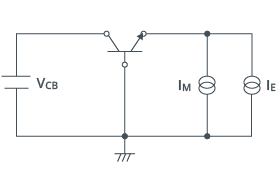

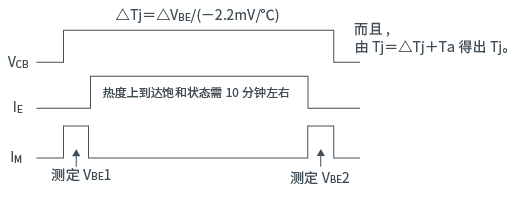

这里,PC、Ta、△Tx、Px可以由各自测定时的设定值或测定结果直接得出,但是只有Tj不能直接得出。因此,如下列出使用VBE的测试方法。

VBE测定法 硅晶体管的情况下 基极-发射极间电压:VBE根据温度变化。

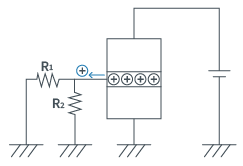

图1. 热电阻测量电路

由此,通过测定VBE,可以推测结温。

通过图1的测定电路,对晶体管输入封装功率:PC(max)。

(假设1W晶体管的情况下,输入条件为VCB=10V bbr title="" style="box-sizing: border-box; border-bottom: none; cursor: help;">IE=100mA)

如图2:

从这个结果得出△VBE=VBE2-VBE1。

这里,硅晶体管根据温度具有一定的温度系数。约为ー2.2mV/ºC。 (达林顿晶体管为ー4.4mV/ºC)

因此,根据由输入功率得出△VBE,可以由以下算式得出上升的结温。

图2. 进度表

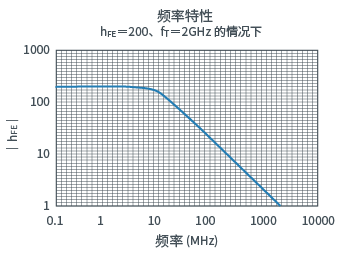

fT:增益带宽积、截止频率

fT:增益带宽积指晶体管能够动作的极限频率。

所谓极限,即基极电流对集电极电流的比为1(即hFE=1)的情况。

提高基极输入频率,hFE变低。

这时,hFE为1时的频率叫做fT(增益带宽积)。

fT指在该频率下能够工作的极限值。

但是,实际使用时能够动作的只有fT值的1/5 to 1/10左右。

测定条件如下

f: 根据测定装置而定。为测定的标准频率。

VCE:任意设定。我公司为一般值。

IC:任意设定。我公司为一般值。

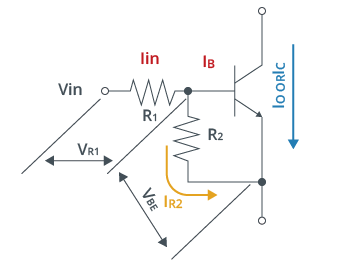

四、数字晶体管的原理

选定方法

①使TR达到饱和的IC/IB的比率是IC/IB=20/1

②输入电阻:R1是±30% E-B间的电阻:R2/R1=±20%

③VBE是0.55~0.75V

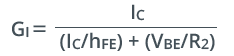

数字晶体管具有下面的关系式。

■数字晶体管直流电流增益率的关系式

GI:数字晶体管的直流电流增益率

GI=IO/Iin

hFE=IC/IB

IO=IC , Iin=IB +IR2, IB=IC/hFE , IR2=VBE/R2

电压关系式 VIN=VR1+VBE

■集电极电流关系式

∴ IC= hFE×1) ・・・①

※这里所说的hFE是VCE=5V、IC=1mA时的值,不是饱和状态。

作为开关使用时,需要饱和状态的电流比率IC/IB=20/1

∴ IC= 20×2)・・・②

将式子①的hFE替换成20/1。

而且,如果在考虑偏差的基础上计算 将R1的最大值+30% R2的最小值-20% VBE的最大值0.75V这一组最差数值代入式子②计算。 根据下面的式子选择数字晶体管的电阻R1、R2,使数字晶体管的IC比使用设备上的最大输出电流Iomax大。

∴ Iomax≦203)

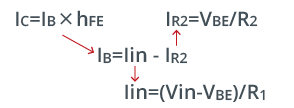

数字晶体管的型号说明

IO和IC的区别

IC: 能够通过晶体管的电流的最大理论值

IO: 能够作为数字晶体管使用的电流的最大值

解说

DTA/C系列为例,构成数字晶体管的个别晶体管能流过100mA电流。

用IC=100mA定义。个别晶体管连接电阻R1、R2,则成为数字晶体管。

此数字晶体管流过IC=100mA时,基极电流IB需要相对应的电流値,其结果需要高的输入电压VIN。

根据绝对最大额定值限制,由输入电阻R1的功率许容值(封装功率)决定输入电压VIN(max)。电流IC=100mA流过时,可能超过这个额定值,在不超过VIN(max)条件下,数字晶体管中流过的电流值定义为IO。

如您所知,绝对最大额定值被定义为”不能同时提供2项以上“,仅用IC标记没有问题,但结合客户实际使用状态,合并标记为IO。

因此电路设计探讨中此IO即为绝对最大额定值。

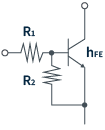

GI和hFE的区别

hFE: 作为晶体管的直流电流增幅率

GI: 作为数字晶体管的直流电流增幅率

解说

GI和hFE都表示发射极接地直流电流放大率。 数字晶体管是指普通晶体管上连接2个电阻器的晶体管。 直流电流放大率为 输出电流/输入电流 ,因此不因输入电阻R1,放大率下降。仅有输入电阻R1的类型 放大率表示为hFE,与个别晶体管hFE相等。 如果在E-B间附加电阻R2,输入电流则分为流过个别晶体管的电流和流过E-B间电阻R2的电流。 因此放大率比单体时下降。此值称为GI,用以区分。

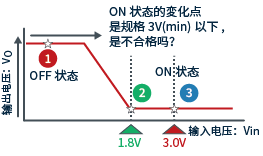

关于VI(on)和VI(off)的区别

VI(on)、VI(off)容易被混淆

VI(on): 数字晶体管为保持ON状态的最低电压、定义VI(on)为min

错误观点

1:由0开始依次加入输入电压。

2:达到1.8V时,数字晶体管启动。

3:因在规格书规定的3V(min) 以下,故判断为不合格。

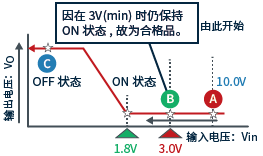

正确观点

A:首先为了启动数字晶体管,加入足够的输入电压Vin(如10V)

B:渐渐降低电压,到规格书规定的3V时停止。 因仍保持ON状态,故该产品为合格。

C:如果继续降低基极电压,不能完全保持ON状态,而向OFF状态变化。 因这一变化点在3V以下,故产品为合格。

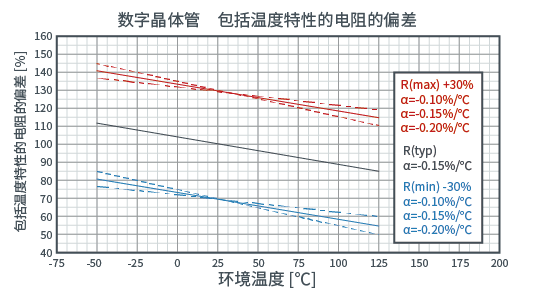

关于数字晶体管的温度特性

根据环境温度、VBE、hFE、R1、R2变化。

hFE的温度变化率约为0.5%/ºC

VBE的温度系数约为-2mV/ºC(-1.8 to -2.4mV/ºC的范围有偏差)

R1的温度变化率,如下图表。

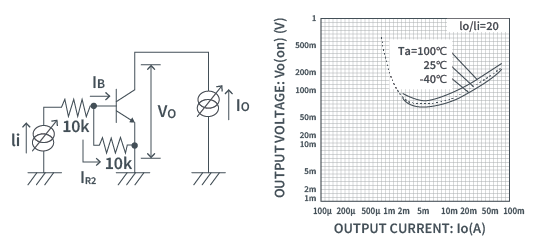

关于输出电压 - 输出电流特性的低电流领域(数字晶体管的情况)

数字晶体管的输出电压-输出电流特性,按以下测定方法测定。

IO(低电流区域)条件下,个别晶体管基极没有电流流过。

因此低电流区域输出电压 (VO)[VCE(sat)]上升。

测定方法 DTC114EKA 的场合 用IO/Ii=20/1测定。

Ii=IB+IR2、(IR2=VBE/10k=0.65V/10k=65μA)

IB=Ii-IR2=Ii-65μA 即Ii在65µA以下时,IB没有电流流过,VO [VCE(sat)]上升。 因此,在低电流区域不能测定VO。

关于数字晶体管的开关动作

①晶体管的动作

如图1,输入电压,启动NPN晶体管。

在这个电路中,基极(B)-发射极(E)之间输入顺向电压,注入基极电流。 就是说,在基极(B)领域注入+空穴。 如果在基极(B)领域注入+电子,发射极(E)的载流子-会被吸引至基极(B),但是正极(B)领域非常薄,因此通过加入集电极电压,载流子可以穿越基极(B)流向集电极(C)。 借此,电流可以由集电极(C)→发射极(E)流动。

②开关动作

晶体管的动作有增幅作用和开关作用。 在增幅作用中,通过注入基极电流IB,能够通过增幅hFE倍的集电极IC。 在活性领域中,通过输入信号持续控制集电极电流,可以得到输出电流。 在开关作用中,在ON时电气性饱和状态(降低集电极-发射极间的饱和电压)下使用。

关于数字晶体管的用语

VI(on)Min.:输入电压 (INPUT ON VOLTAGE)

向OUT引脚、GND引脚间施加正向电压 (VO),并得到规定的输出电流时需要的最小输入电压,即数字晶体管导通区域的最小输入电压值。

因此,如果要从ON状态变为OFF状态,需要进一步降低该最小输入电压值,所以正常产品的电压值低于这个数值。

VI(off)Max.:输入电压 (INPUT OFF VOLTAGE)

在向OUT引脚、GND引脚间施加电源电压 (VCC)、输出电流 (IO) 的状态下,IN引脚、GND引脚间得到的最大输入电压,即可以保持数字晶体管OFF状态区域的最大输入电压值。 因此,如果要从OFF状态变为ON状态,需要进一步升高该最大输入电压值,所以正常产品的电压值高于这个数值。

VO(on):输出电压 (OUTPUT VOLTAGE)

在任意输入条件下不超过绝对最大额定值的输出引脚电压。GND接地放大电路流过充足的输入电流时,输出电压降低,IN、OUT接合也变为正偏压状态。在规定的VO、IO下将II设定为整数(通常10~20)分之一进行测定。

II(Max.):输入电流 (INPUT CURRENT)

向IN引脚、GND引脚间施加正向电压 (VI) 时,IN引脚连续流过电流的最大输入容许值。

GI:GND接地直流电流增益 (DC CURRENT GAIN)

在规定的VO、IO条件下的IO/II的比值。

R1:输入电阻 (INPUT RESISTANCE)

在IN引脚、晶体管基极之间内置的电阻。R1的公差设定为±30%。另外,还会随着温度的变化而变化。

R2/R1:电阻比率(RESISTANCE RATIO)

晶体管的基极∙发射极之间的电阻与内置输入电阻的比率。