作者:Frank Qin

本文引用地址:Abstract

随着汽车电子的快速发展,汽车上很多电机的驱动方式已经从传统继电器逐渐演变成为MOSFET驱动的直流电机。同时,为了实现更高速和更精确的控制,现在对于MOSFET预驱的要求也逐渐变高。-Q1作为一款高度集成式 H 桥栅极驱动器不仅可以满足现在越发精细的需求,也可以实现更多元的保护,确保系统运行过程中的各种风险和错误都可以被识别到并实施保护。本文即具体讨论-Q1的机制以及一些经验分享。

Contents

1. 背景介绍............................................................1

2. 诊断和保护类型..................................................2

2.1 VGS监控机制................................................... 2

2.2 VGS监控触发点:tDRIVE 以及deglitch time.......3

2.3 VGS报错和恢复机制......................................... 4

2.4 VGS监控和INx信号反转的关系......................... 4

3..... Corner case举例............................................ 5

4..... 总结................................................................ 6

参考文献..................................................................6

Figures

Figure 1. 内部设计示意框图......................................... 2

Figure 2. VGS错误检测的触发点和有效区间................................. 3

Figure 3. VGS报错和不报错的两种情况........................................ 4

Figure 4. MOSFET闭合太缓导致的VGS误报举例....................... 6

1. 背景介绍

DRV8705-Q1 是一款高度集成式 H 桥栅极驱动器,能够驱动高侧和低侧 N 沟道功率 MOSFET。它可使用集成式倍增电荷泵(针对高侧)和线性稳压器(针对低侧)生成合适的栅极驱动电压。DRV8705-Q1 提供了一系列保护功能,可确保系统稳定运行。此类功能包括适用于电源和电荷泵的欠压和过压监控、适用于外部 MOSFET 的 VDS 过流和 VGS 栅极故障监控、离线开路负载和短路诊断,以及内部热警告和热关断保护功能。DRV8705-Q1有两种版本,H版本为硬线版本,可以简化控制并节省MCU引脚资源。S版本为SPI控制,可以详细配置和诊断。

2. 诊断和保护类型

DRV8705-Q1可以支持多种诊断和保护类型,包括运行前的系统监控(offline diagnostic)和运行中的故障监控:对于电源和电荷泵的欠压及过压监控、针对外部MOSFET的VDS和VGS栅极故障监控、离线开路负载和短路检测,以及内部热警告和热关断保护。其中为了保护外部MOSFET,和保护尤为重要:通过对外部MOSFET的VGS电压的监控并控制MOSFET的开关,可以有效防止MOSFET的栅极短路错误或栅极电压卡在高位或低位的情况。

Figure 1. DRV8705内部设计示意框图

2.1 VGS监控机制

VGS(栅源电压)是栅极相对于源极的电压,VTH(阈值电压)是MOSFET导通或截止的阈值。栅源电压(VGS)与阈值电压(VTH)之间的关系直接决定了MOSFET的导通与截止状态。要实现 MOSFET的开关功能,需要确保 VGS 大于 VTH。在MOSFET导通时,栅源电压(VGS)大于阈值电压(VTH),沟道形成,电流可以通过器件。而在MOSFET截止时,栅源电压(VGS)小于阈值电压(VTH),沟道被堵塞,电流无法通过。

因此DRV8705通过监控VGS和设定的阈值VGS_LVL做比较(如图1),来判定MOSFET是否正确的导通或者截止。以此来防止输出错误、栅极短路以及上下管直通的问题。VGS_LVL可以通过寄存器9h bit1来修改,有1V和1.4V两个选项。VGS fault会在VGSHx和VGSLx的上升沿和下降沿做检测,当在tDRIVE时间内没有检测到VGS电压穿过VGS_LVL时,就会报出VGS fault的错误,芯片停止输出并提出警报(拉低nFAULT或WARN)。所以datasheet的Table 7-9将VGS触发条件标注为VGS > VGS_LVL是不够严谨的,应以datasheet章节7.3.8.8 Gate Driver Fault (VGS_GDF)中描述的“cross”为准,可以包含上升沿和下降沿的两种情况。

2.2 VGS监控触发点:tDRIVE 以及deglitch time

MOSFET正在打开或者闭合的这个时间称之为tDRIVE,也就是VGSHx和VGSLx这两个电压正在上升或者下降的时间(如图2)。对于VGS错误检测来说,tDRIVE时间就是blanking time,这个时间内VGS相对于阈值的关系是不会被关注的。而deglitch time是真正去判断VGS和阈值之间相互关系的时间区间,对于DRV8705-Q1来说,无论是S还是H版本,deglitch time都固定在2us。也就是意味着如果VGS在这2us的时间内依然没有穿过阈值,芯片会在认为MOSFET没有正确地打开或者关闭,芯片会在2us结束后报错。

Figure 2. VGS错误检测的触发点和有效区间

图2中绿色部分比较直观地展示了检测VGS fault的场景,即VGSHx和VGSLx在上升沿和下降沿的tDRIVE(blanking time)结束后开始检测,deglitch time是紧接着tDRIVE结束后立即开始的。在绿色区域的时间内检测到的VGS错误都会在2us的deglitch time结束后报错。图3举例说明了VGS报错和不报错的两种情况。

Figure 3. VGS报错和不报错的两种情况

请注意,对于DRV8705-Q1来说,tDRIVE的时间并不是由MOSFET决定的。H版本的tDRIVE固定为4us,S版本的tDRIVE是可以通过寄存器调整的(2~96us)。因此,在利用DRV8705-Q1s设计时,请根据选用的MOSFET型号以及配置的IDRIVE电流确定合适的芯片tDRIVE时间。判断标准为,需保证MOSFET打开或闭合的时间不长于DRV8705-Q1的tDRIVE时间,否则极有可能被芯片判断为VGS fault。

2.3 VGS报错和恢复机制

当VGS fault被诊断出后,DRV8705S-Q1可以支持四种不同的报错和恢复机制,可以根据实际系统需要进行选择:

Latched Fault Mode:发现错误后,驱动停止使能,nFAULT pin、FAULT寄存器和VGS寄存器都会报错。而且当故障移除后必须通过手动清除CLR_FLT寄存器才可以重置并恢复驱动。

Cycle by Cycle Mode:发现错误后,驱动停止使能,nFAULT pin、FAULT寄存器和VGS寄存器都会报错。当下一个PWM信号进来后,驱动即可自行恢复。但是VGS寄存器仍会留存信息,需要手动清除CLR_FLT寄存器。

Warning Report Only Mode:发现错误后芯片只会通过寄存器和WARN提示,并不会中止输出。

Disabled Mode:发现错误后不会有任何的反馈和提醒。

DRV8705H-Q1版本是固定在了Cycle by Cycle Mode,tDRIVE和deglitch time也都是固定不可调的。

2.4 VGS监控和INx信号反转的关系

DRV8705-Q1支持PWM控制,因此MOSFET上下管的开闭也是可以通过PWM不同的占空比来实现不同的开闭频率。因此代表PWM信号反转的INx信号可以看作是MOSFET开闭动作的触发。如图2所示,每次INx信号反转都出发了MOSFET上管或下管的闭合。

但是,当占空比很小时,INx的反转信号很可能会落在tDRIVE或deglitch time这个区间中。INx落在不同的地方也会给VGS诊断带来不同的影响,VGS诊断报错也会做出不同的反馈。根据IN信号发生反转的不同时间点,以DRV8705H-Q1(tDRIVE=4us)为例,三种情况分类如下:

当IN信号反转发生在blanking/tDRIVE time(4us)内,此时是VGS的blanking time,错误不会被识别。而新周期的诊断会随着IN信号反转同步开始。

当IN信号反转发生在deglitch time(2us)内,此时如果有相应错误已经达成触发条件,nFAULT依然会在deglitch time后报错。而新的诊断是随着IN信号反转同步开始。

当IN信号反转发生在blanking和deglitch time(4+2us)之后,随着IN反转,上一个诊断直接停止,进入下一个周期的诊断。

3. Corner case举例

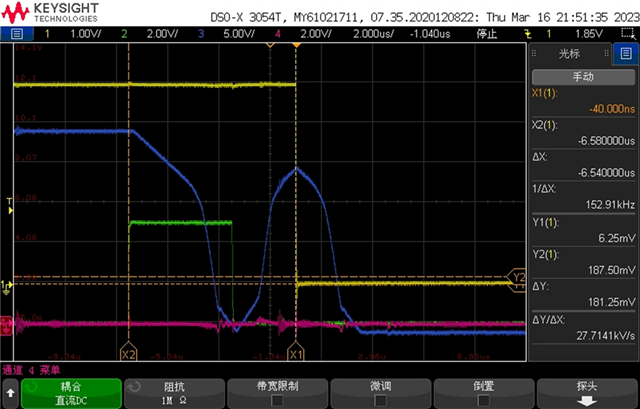

如下图4的示波器截图,测试芯片是H版本的DRV8705H-Q1。其中绿色是IN信号,蓝色是VGSHx,粉色是VGSLx,黄色是nFAULT信号,X轴每格是2us。

从波形可以看出,黄线nFAULT拉低表示报错,芯片判断为VGS fault,nFAULT拉低的时间正好大约是IN信号拉高的6us之后,也就是tDRIVE+deglitch的(4+2)us。从绿色的IN信号可以算出,此时的PWM(50Hz)占空比很高,是92%,MOS管上管下降很缓,没能在IN高电平的时间内完成下降,粉线表示的下管没有成功开启,可以看到此时蓝线表示的上管已经开始第二次开启。从波形图可以清楚看到,由于MOSFET下降太缓,导致没能完成闭合。这个case巧合的地方在于,IN信号反转的时间点正好和tDRIVE时间结束也就是deglitch time诊断开始的时间点是重合的。对于VGS诊断来说,此时就正式开始监控,而恰好此时IN信号发生反转,则VGS诊断直接记录了此时的VGS电压并在2us的规定动作之后报错拉低了nFAULT。

这个case虽然巧合,恰好因为PWM占空比的IN反转信号踩在了blanking time结束的时间点,触发了诊断报错。但是真正引发错误的根本原因是MOSFET下降太缓,没有在tDRIVE的时间内完成下降而触发了错误。因此在配置tDRIVE时间以及MOSFET选型时,这是需要注意规避的要点。

Figure 4. MOSFET闭合太缓导致的VGS误报举例

4. 总结

DRV8705-Q1作为一款集成了多种诊断和保护功能的H桥栅极桥驱芯片,可以灵活应用在各类需要马达驱动的汽车类应用中。正确理解DRV8705-Q1的诊断和保护模式也可以更好地利用该芯片实现安全高效地应用。

参考文献

DRV8705-Q1 数据手册 (SLLSFB6A)

Smart Gate Drive (SLVAE70)

Understanding Smart Gate Drive (SLVA714D)