现场可编程门阵列 (FPGA)、支持 Linux 的RISC-V 微控制器单元 (MCU) 子系统、先进的存储器架构和高性能通信接口,是设计人员的重要工具。对于安全互联系统、安全关键型系统,以及人工智能 (AI) 和机器学习 (ML) 等各种硬实时确定性系统的设计人员,更是如此。

本文引用地址:然而,将这些不同要素整合成一个安全、互联且具确定性的系统可能极具挑战性且非常耗时,为各种系统要素布设高速互连器件也是一样。设计人员需要提供存储器管理单元、存储器保护单元、安全启动能力以及用于高速连接的千兆级收发器。设计将需要活动和静态功率管理以及涌流控制。一些设计要求能够在 0°C 至 +100°C 结温 (TJ) 的扩展商用温度范围内工作,而工业环境中的系统需要在 -40°C 至 +100°C 的 TJ 内工作。

为了应对这些和其他挑战,设计人员可以借助 FPGA 片上系统 (SoC) 器件,这种器件具备低功耗、热效率和国防级安全等特点,可实现智能、互联、确定性的系统。

本文回顾了此类 FPGA SoC 的架构,以及它如何支持高效设计互联确定性系统。随后,本文简要介绍了EEMBC CoreMark-Pro 处理能力与功耗基准的关系,并考察了一款代表性 FPGA SoC 的基准性能。本文探讨了如何将安全性植入这些 FPGA SoC,并详细介绍了 Microchip Technology 的典范 FPGA SoC,以及能加速设计过程的开发平台。最后,文中简要列出了 MikroElektronika 的扩展板,这些扩展板可用于实现一系列通信接口和全球卫星导航系统(GNSS) 定位能力。

用 FPGA 结构构建的 SoC

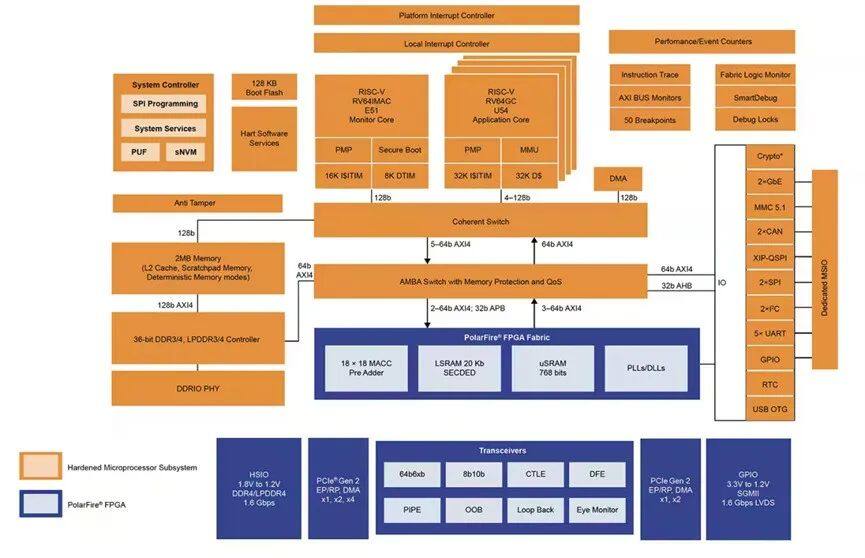

该 SoC 的“芯片”是 FPGA 结构,包含各种系统要素:从 FPGA 到用强化 FPGA 逻辑构建的 RISC-V MCU 子系统。MCU 子系统包括一个四核 RISC-V MCU 集群、一个 RISC-V 监视核心、一个系统控制器和一个确定性 2 级 (L2) 存储器子系统。这些SoC 中的 FPGA 包含多达 460 K 的逻辑元件、高达 12.7 Gbps 的收发器以及其他输入/输出 (I/O) 模块,包括通用 I/O (GPIO) 和外设快速互连标准 (PCIe) 2 模块。整体架构设计可靠。其包括用于所有存储器的单错误校正和双错误检测(SECDED)、差分功率分析 (DPA)、物理存储器保护以及128 Kb 闪存启动存储器(图 1)。

图 1:该 FPGA SoC 的所有要素(包括 RISC-V 子系统)都是在 FPGA 结构上实现的。(图片来源:Microchip Technology)

Microchip 提供由第三方工具和设计资源组成的 Mi-V(发音为“my five”)生态系统,以支持 RISC-V 系统的实现。该生态系统的建立是为了加快 RISC-V 指令集架构 (ISA) 在强化 RISC-V 内核和 RISC-V 软内核中的应用。Mi-V 生态系统的要素包括:

● 知识产权 (IP) 许可证

● 硬件

● 操作系统和中间件

● 调试器、编译器和设计服务

FPGA SoC 中的强化 RISC-V MCU 包括多种调试功能,如无源运行时可配置的高级可扩展接口 (AXI) 和指令跟踪。通过 AXI,设计人员可以监控写入各种存储器或从中读取的数据,并知道数据被写入或读取的时间。

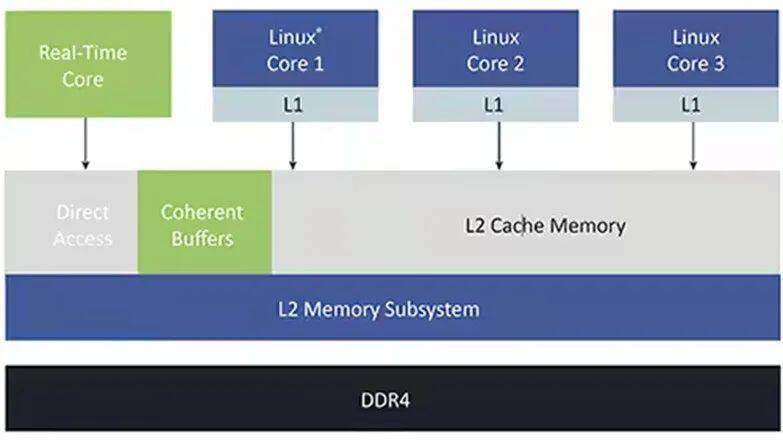

RISC-V MCU 子系统采用 5 级单发射有序流水线。此流水线不易受到 Spectre 或 Meltdown 漏洞(可能会导致乱序架构遭受攻击)的影响。所有 5 个 MCU 与存储器子系统相一致,支持各种确定性非对称多处理 (AMP) 模式实时系统和 Linux。RISC-V 子系统的功能包括(图 2):

● 运行 Linux 和硬实时操作

● 将 L1 和 L2 配置为确定性存储器

● DDR4 存储器子系统

● 禁用/启用分支预测器

● 有序流水线操作

图 2:RISC-V 子系统包括多个处理器和存储器元件。(图片来源:Microchip Technology)

以更低能耗提供更强大处理能力

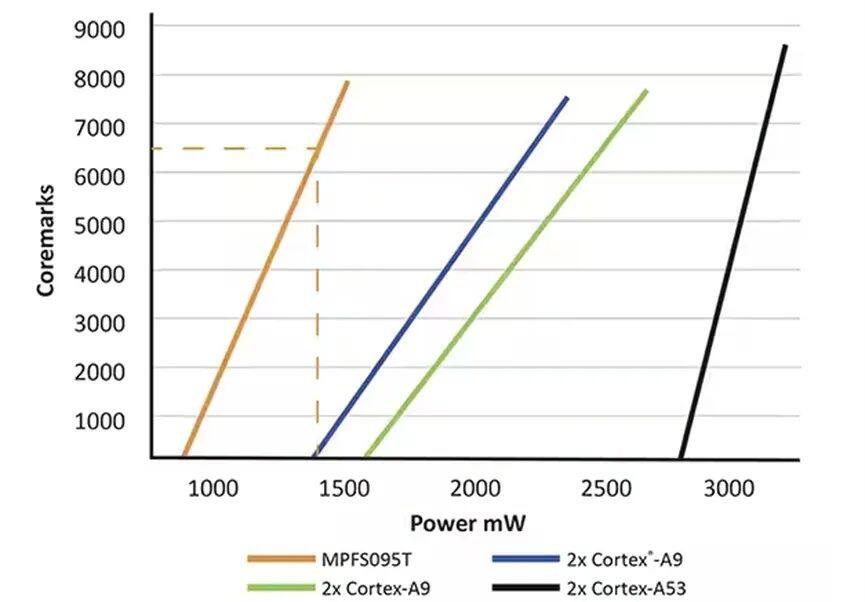

这些 FPGA SoC 除了系统运行优势(包括支持硬实时处理)之外,还具有非常高的能效。EEMBC CoreMark-PRO 基准测试是比较嵌入式系统中 MCU 的效率和性能的一种行业标准,专门设计用来衡量硬件性能,并取代 Dhrystone 基准。

CoreMark-PRO工作负载包括 4 种浮点工作负载和 5 种流行的整数工作负载,其性能特点、指令级并行和存储器利用率各不相同。浮点工作负载包括源自 LINPACK 的线性代数例程、快速傅里叶变换、用于模式评估的神经网络算法以及改进版的Livermore 循环基准测试。JPEG 压缩、XML 解析器、ZIP 压缩和 256 位安全哈希函数算法 (SHA-256) 构成整数工作负载的基础。

这些 SoC FPGA 的 MPFSO95T 模型,如 MPFS095TL-FCSG536E,可在 1.3 W 下实现高达 6500 Coremarks(图 3)。

图 3:MPFS095T FPGA SoC(橙线)在 1.3 W 下实现 6500 Coremarks。(图片来源:Microchip Technology)

安全考虑

这些 FPGA SoC 的安全关键型和硬实时应用除了需要高能效和强大的处理能力外,还需要强大的安全性。这些 FPGA SoC 的基本安全功能包括防差分功率分析 (DPA) 的位流编程、真随机数发生器 (TRNG) 和物理不可克隆功能 (PUF)。安全功能还包括:标准和用户自定义的安全启动;物理存储器保护,其提供与机器的特权状态相关的存储器访问限制,包括机器、超级用户或用户模式;以及免受 Meltdown 和 Spectre 攻击的能力。

安全始于安全的供应链管理,包括在晶圆测试和封装期间使用硬件安全模块 (HSM)。每个 FPGA SoC 中都嵌入了 768 字节的数字签名 x.509 FPGA 证书,以增强供应链的安全保证。

这些 FPGA SoC 中包含许多片上防篡改检测器,以确保其安全可靠地运行。如果检测到篡改,就会发出一个篡改标志信号,使系统能够根据需要作出响应。提供的一些防篡改检测器包括:

● 电压监控器

● 温度传感器

● 时钟毛刺和时钟频率检测器

● JTAG 主动检测器

● Mesh 主动检测器

256位高级加密标准 (AES-256) 对称分组密码相关性功耗攻击 (CPA) 防范措施、确保数据完整性的集成加密摘要功能、用于密钥存储的集成 PUF,以及用于 FPGA 结构和所有片上存储器的归零功能,进一步确保了安全性。

FPGA SoC 实例

Microchip Technology 将这些能力和技术整合到其 PolarFire FPGA SoC 中,这些 SoC 提供多种速度等级、温度等级和不同封装尺寸,以支持设计人员对 25 K 至 460 K 逻辑元件的广泛解决方案需求。有 4 个温度等级可供选择(均为 TJ 额定值):0°C 至 +100°C 的扩展商用范围、-40°C 至 +100°C 的工业范围、-40°C 至 +125°C 的汽车范围和 -55°C 至 +125°C 的军用范围。

设计人员可以选择标准速度等级的器件,或选择速度快 15% 的 -1 速度级器件。这些FPGA SoC 可以在 1.0 V 电压下工作以实现最低功耗,或者在 1.05 V 电压下工作以获得更高性能。它们提供一系列封装尺寸,包括 11 x 11 mm、16 x 16 mm 和 19 x 19 mm。

对于需要扩展商用温度范围、标准速度、254 K 逻辑元件和 19 x 19 mm 封装的应用,设计人员可以使用 MPFS250T-FCVG484EES。对于需要 23 K 逻辑元件的更简单解决方案,设计人员可以使用 MPFS025T-FCVG484E,该元件采用 19 x 19 mm 封装,也能在扩展商用温度范围内以标准速度工作。具有 254 K 逻辑元件的 MPFS250T-1FCSG536T2 专为高性能汽车系统而设计,其工作温度范围为 -40 至 125°C,速度等级为 -1,时钟速度快 15%,采用紧凑型16 x 16 mm 封装,焊球数为 536,间距为 0.5 mm(图 4)。

图 4:汽车温度 MPFS250T-1FCSG536T2 采用 16 x 16 mm 封装,焊球数为 536,间距为 0.5 mm。(图片来源:Microchip Technology)

FPGA SoC 开发平台

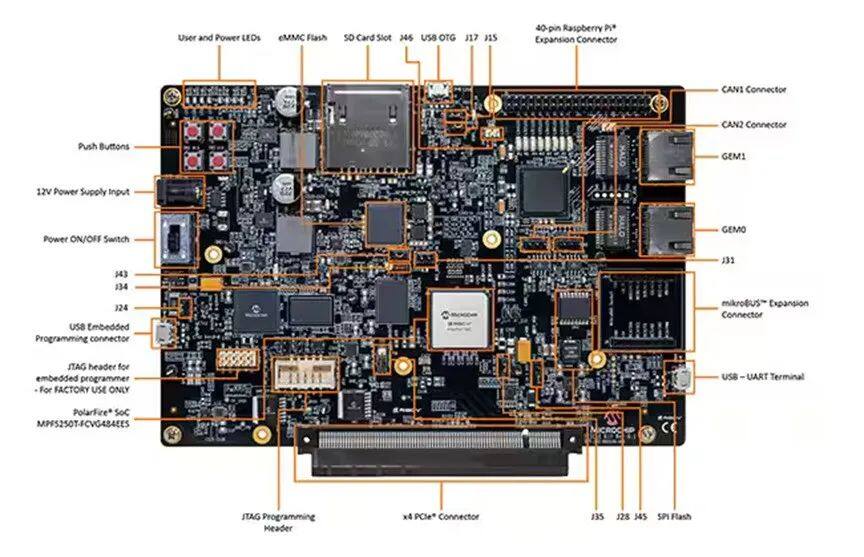

为了加快采用 PolarFire FPGA SoC 的系统设计,Microchip 提供 MPFS-ICICLE-KIT-ES PolarFire SoC Icicle 套件,其支持探索低功耗实时执行、可运行 Linux 的五核 RISC-V 微处理器子系统。该套件包括一个免费的 Libero Silver 许可证,能满足评估设计需要。它支持单一语言编程和调试功能。

这些 FPGA SoC 在 VectorBlox 加速器软件开发工具包 (SDK) 的支持下,可以实现低功耗、小尺寸的 AI/ML 应用。该工具包旨在简化设计过程,设计人员事先无需具备 FPGA 设计经验。VectorBlox 加速器 SDK 使开发人员可以使用 C/C++ 语言对高能效神经网络进行编程。Icicle 套件提供一个全面的开发环境,具备众多功能,包括:监视各种功率域的多轨功率传感器系统,PCIe 根端口,用于运行 Linux 和 Raspberry Pi 的板载存储器(包括 LPDDR4、QSPI 和 eMMC 闪存),用于一系列有线和无线连接选项的 mikroBUS 扩展端口,以及 GNSS 定位能力等功能扩展(图 5)。

图 5:该 FPGA SoC 综合开发环境包括用于连接 Raspberry Pi(右上方)和 mikroBUS(右下方)扩展板的连接器。(图片来源:Microchip Technology)

扩展版

mikroBUS扩展板的几个例子包括:

MIKROE-986,使用串行外设接口 (SPI) 增加 CAN 总线连接。

MIKROE-1582,用于 MCU 和 RS-232 总线之间的接口。

MIKROE-989,用于与 RS422/485 通信总线连接。

MIKROE-3144,支持 LTE Cat M1 和 NB1 技术,实现与 3GPP 物联网设备的可靠简单连接。

MIKROE-2670,支持 GNSS 功能,可同时接收 GPS 和Galileo 信号以及北斗或 GLONASS 信号,在城市峡谷中信号较弱或有干扰的情况下也能实现高定位精度。

总结

开发互联、安全关键型和硬实时确定性系统时,设计人员可以采用 FPGA SoC。FPGA SoC 提供诸多系统要素,包括 FPGA 结构、带有高性能存储器的 RISC-V MCU 子系统、高速通信接口和众多安全功能。为了帮助设计人员开始工作,相关厂商提供了包含所有必要元件的开发板和环境,包括可用于实现广泛通信和定位功能的扩展板。

小编的话

设计一个高完整度的硬实时确定性系统面临诸多挑战,相信有不少系统设计工程师朋友都有过在安全、互联和高效及低功耗这些方面要如何配置子系统才能实现最佳性能的困扰。本文介绍的利用FPGA架构进行SoC设计的方法,提供了一个高效灵活的实现路径。您认为应用FPGA架构进行系统芯片设计是一个理想的方法吗?您是否有采用过文中提到的器件和开发平台进行系统开发?

作者:Jeff Shepard 来源: