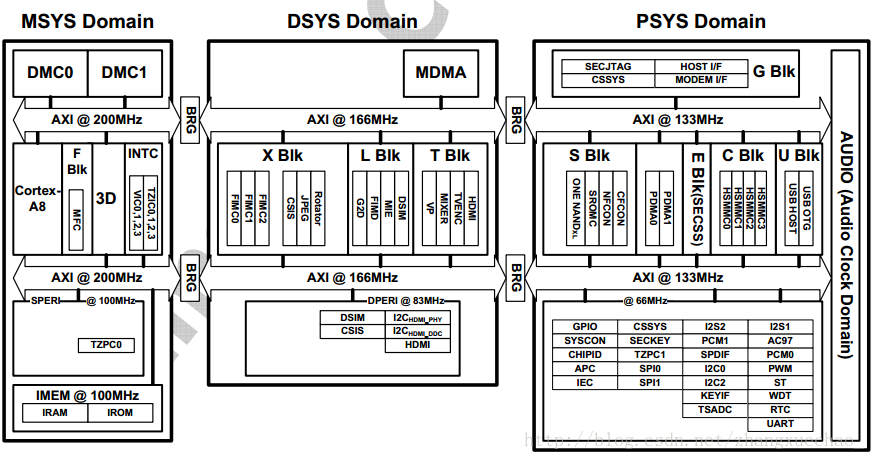

CLOCK DOMAINS 时钟域

S5PV210 consists of three clock domains, namely, main system (MSYS), display system (DSYS), and peripheral system (PSYS)

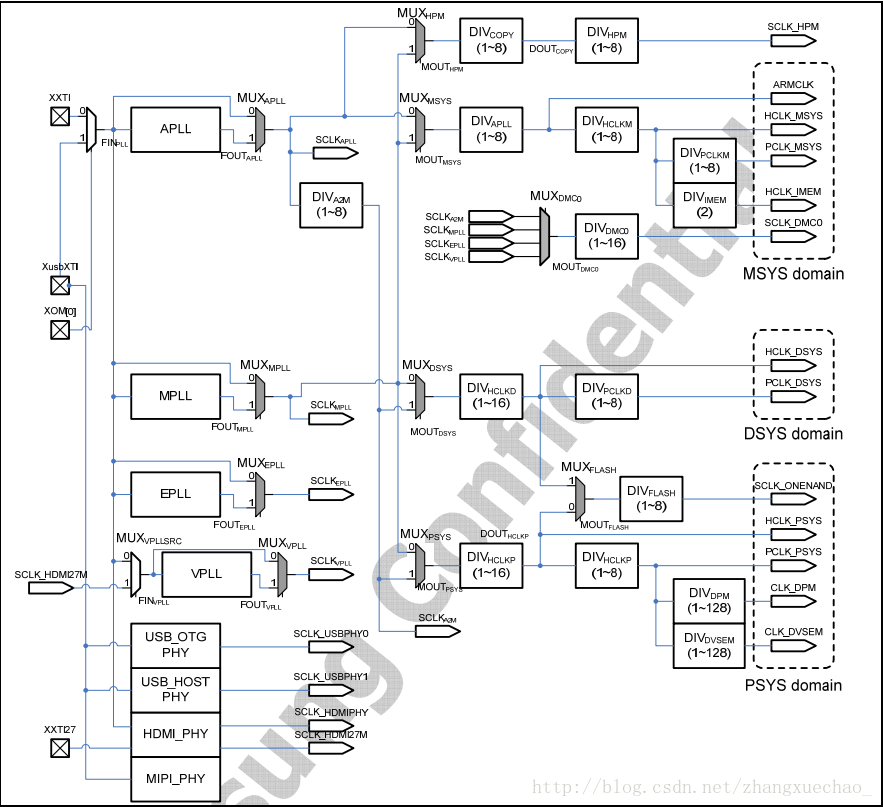

时钟源

外部焊接:

1.XRTCXTI:实时时钟

2.XXTI:CPU时钟

3.XUSBXTI:USB时钟

4.XHDMIXTI:HDMI时钟

CMU典型应用:

1.MSYS clock domain uses APLL (that is, ARMCLK, HCLK_MSYS, and PCLK_MSYS)

2.DSYS and PSYS clock domain (that is, HCLK_DSYS, HCLK_PSYS, PCLK_DSYS, and PCLK_PSYS) and other peripheral clocks (that is, audio IPs, SPI, and so on) use MPLL and EPLL

3.Video clocks uses VPLL

时钟关系

MSYS clock domain

− freq(ARMCLK) = freq(MOUT_MSYS) / n, where n = 1 ~ 8

− freq(HCLK_MSYS) = freq(ARMCLK) / n, where n = 1 ~ 8 //高速

− freq(PCLK_MSYS) = freq(HCLK_MSYS) / n, where n = 1 ~ 8 //低速

− freq(HCLK_IMEM) = freq(HCLK_MSYS) / 2 //内存

• DSYS clock domain

− freq(HCLK_DSYS) = freq(MOUT_DSYS) / n, where n = 1 ~ 16

− freq(PCLK_DSYS) = freq(HCLK_DSYS) / n, where n = 1 ~ 8

• PSYS clock domain

− freq(HCLK_PSYS) = freq(MOUT_PSYS) / n, where n = 1 ~ 16

− freq(PCLK_PSYS) = freq(HCLK_PSYS) / n, where n = 1 ~ 8

− freq(SCLK_ONENAND) = freq(HCLK_PSYS) / n, where n = 1 ~ 8 //nand

PLL 锁相环

1.APLL can drive MSYS domain and DSYS domain

2.MPLL can drive MSYS domain and DSYS domain

3.EPLL is mainly used to generate audio clock

4.VPLL is mainly used to generate video system operating clock

CLK_SRC0, R/W, Address = 0xE010_0200

PLL选择,通过设置相应的位

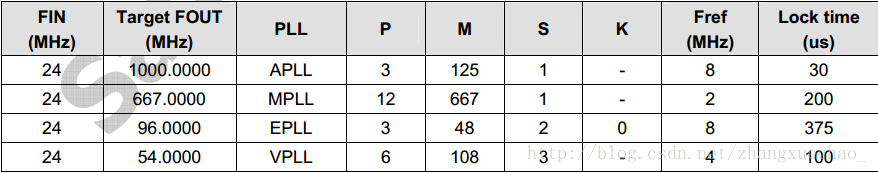

倍频

以APLL举例

APLL_CON0, R/W, Address = 0xE010_0100

FOUT = MDIV * FIN / (PDIV * 2^(SDIV-1))

PDIV: 1 ≤ PDIV ≤ 63

MDIV: 16 ≤ MDIV ≤ 1023

SDIV: 0 ≤ SDIV ≤ 5

常用参考值

倍频到1G

输入频率,默认24M

FOUT = 125 * 24 / (3 * 2^(1-1)) = 1000