【导读】在FMS 2023闪存峰会上,SK海力士展示了其新型PLC(5-Bit MLC)技术的研究成果。这一技术原理上类似铠侠2019年开发的Twin BiCS FLASH技术,简单来说就是用两个2.5 bit单元,这样双线程同时写入的话一定会比5 bit存储快得多。

在FMS 2023闪存峰会上,SK海力士展示了其新型PLC(5-Bit MLC)技术的研究成果。

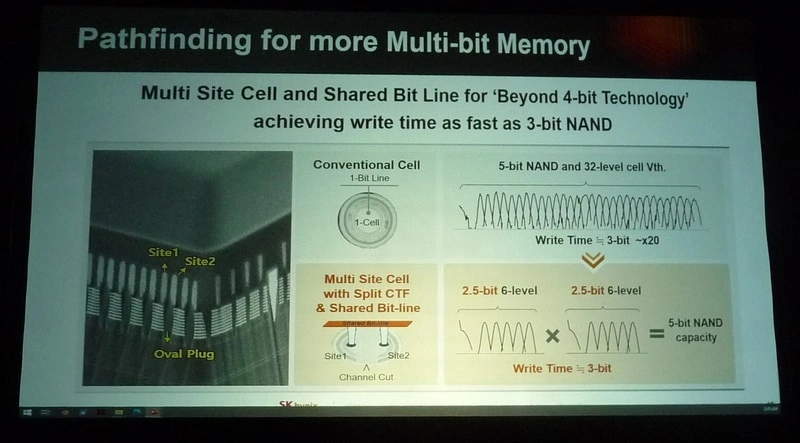

这一技术原理上类似铠侠2019年开发的Twin BiCS FLASH技术,简单来说就是用两个2.5 bit单元,这样双线程同时写入的话一定会比5 bit存储快得多。

在5 bit单元中,一个存储单元中可以包含32个不同的阈值电压,而常规方式下用PLC写入并验证32个不同的阈值电压所需时间是TLC的近20倍,这显然是用户无法接受的。

因此,SK海力士设计了一种新型PLC,将一个5bit单元分为两个2.5 bit点位,每个点也存储2.5 bit。然后综合各个点的数据获得5 bit数据,这样就可以使PLC写入时间与TLC(3bit单元)大致相同。

实际上,Solidigm一年前已经展示过首款采用PLC-NAND的SSD,它沿用了当前QLC-NAND一样的192层闪存,但由于每个单元由5 bit(而非4bit)点组成,其密度增加至23.3Gbit/mm²,创下了最高记录;而凭借321层的第9代新型TLC-NAND,预计SK海力士有望达到20Gbit/mm² 以上的密度。当然,更多的层数也意味着更多的工作步骤和更高的成本,预计早期产品依然还会很贵。

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。

推荐阅读: