7.1 STM32定时器概述

STM32内部共有8个定时器,其中Timer1和Timer8属于高级定时器,Timer2~Timer5属于通用定时器,8个定时器的资源独立,互不影响。

STM32的通用定时器是一个通过可编程预分频器(PSC)驱动的16位自动装载计数器(CNT)构成。STM32的通用定时器可以被用于:测量输入信号的脉冲长度(输入捕获)或者产生输出波形(输出比较和PWM)等。使用定时器预分频器和RCC时钟控制器预分频器,脉冲长度和波形周期可以在几个微秒到几个毫秒间调整。STM32的每个通用定时器都是完全独立的,没有互相共享的任何资源。

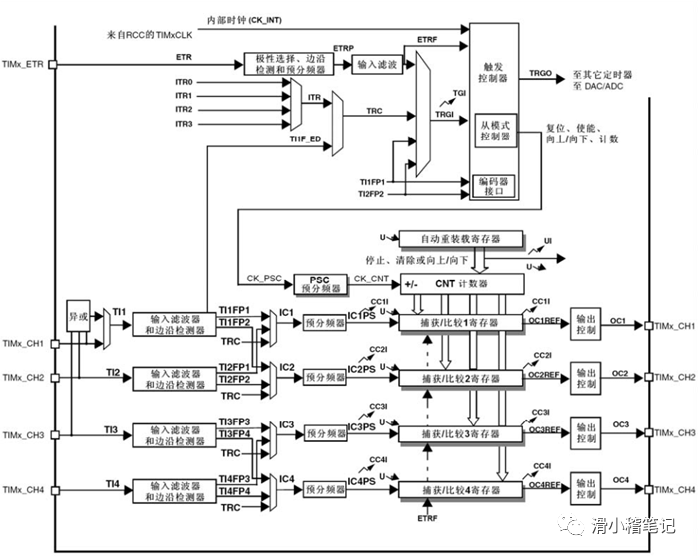

通用定时器的内部结构如下图所示。

7.2 相关寄存器

要使用通用定时器的基本功能,一共需要配置4个寄存器,剩余的寄存器都是在输入捕获和输出比较中使用到的。

7.2.1 控制寄存器1:TIMx_CR1

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| - | CKD[1:0] | ARE | CMS[1:0] | DIR | OPM | URS | UDIS | CEN |

Bit 9~Bit 8:时钟分频系数,定义定时器输入时钟频率与数字滤波器采样频率之间的分频系数

00:采样频率与定时器输入频率相等

01:采样频率是定时器输入频率的2倍

10:采样频率是定时器输入频率的4倍

11:保留

Bit 7:自动重装载使能

0:TIMx_ARR寄存器中没有缓冲

1:TIMx_ARR寄存器的数据装入缓存器

Bit 6~Bit 5:选择中央对齐模式

00:边沿对齐模式,计数器根据方向位DIR计数

01:中央对齐模式1,计数器交替向上向下计数,当TIMx_CCMRx中的CCxS=00时,计数器向下计数时被设置

10:中央对齐模式2,计数器交替向上向下计数,当TIMx_CCMRx中的CCxS=00时,计数器向上计数时被设置

11:中央对齐模式3,计数器交替向上向下计数,当TIMx_CCMRx中的CCxS=00时,计数器向下和向上计数时 被均设置

Bit 4:计数方向

0:向上计数,计数器从0计数到TIMx_ARR寄存器的数据时重新从0开始并产生一个计数器溢出事件

1:向下计数,计数器从TIMx_ARR寄存器的数据计数到0时重新从TIMx_ARR寄存器的数据开始并产生一个计数器溢出事件

Bit 3:单脉冲模式

0:发生更新事件时计数器不停止

1:在发生下一次更新事件时,计数器停止

Bit 2:更新请求源

0:如果使能了更新中断或DMA请求,计数器溢出/设置UG位/从模式控制器产生更新都产生更新中断或DMA请求

1:如果使能了更新中断或DMA请求,只有计数器溢出才产生更新中断或DMA请求

Bit 1:禁止更新

0:允许UEV。更新事件由计数器溢出/设置UG位/从模式控制器产生更新事件产生

1:不产生更新事件

Bit 0:使能计数器

0:禁止计数器

1:使能计数器

7.2.2 DMA/中断使能寄存器:TIMx_DIER

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| - | TDE | - | CC4DE | CC3DE | CC2DE | CC1DE | UDE | - | TIE | - | CC4IE | CC3IE | CC2IE | CC1IE | UIE |

Bit 14:允许触发DMA请求

0:禁止触发DMA请求

1:允许触发DMA请求

Bit 12:允许捕获/比较4的DMA请求

0:禁止捕获/比较4的DMA请求

1:允许捕获/比较4的DMA请求

Bit 11:允许捕获/比较3的DMA请求

0:禁止捕获/比较3的DMA请求

1:允许捕获/比较3的DMA请求

Bit 10:允许捕获/比较2的DMA请求

0:禁止捕获/比较2的DMA请求

1:允许捕获/比较2的DMA请求

Bit 9:允许捕获/比较1的DMA请求

0:禁止捕获/比较1的DMA请求

1:允许捕获/比较1的DMA请求

Bit 8:允许更新的DMA请求

0:禁止更新的DMA请求

1:允许更新的DMA请求

Bit 6:触发中断使能

0:禁止触发中断

1:允许触发中断

Bit 4:允许捕获/比较4的中断

0:禁止捕获/比较4的中断

1:允许捕获/比较4的中断

Bit 3:允许捕获/比较3的中断

0:禁止捕获/比较3的中断

1:允许捕获/比较3的中断

Bit 2:允许捕获/比较2的中断

0:禁止捕获/比较2的中断

1:允许捕获/比较2的中断

Bit 1:允许捕获/比较1的中断

0:禁止捕获/比较1的中断

1:允许捕获/比较1的中断

Bit 0:允许更新中断

0:禁止更新中断

1:允许更新中断

7.2.3 预分频寄存器:TIMx_PSC

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| PSC[15:0] |

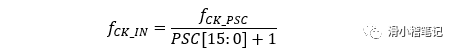

Bit 15~Bit 0:预分频器的值,计数器的时钟频率计算公式为

7.2.4 自动重装载寄存器:TIMx_ARR

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ARR[15:0] |

Bit 15~Bit 0:自动重装载的值,该值就是传送到实际的自动重装载寄存器的数值,当该寄存器的值为空时,计数器不工作。