4.1 模式与异常

当正常程序流程被暂时停止发生异常,例如响应一个来自外设的中断。在处理异常前,必须保护当前的处理器状态,以便在完成处理程序后能恢复到原来的程序 。

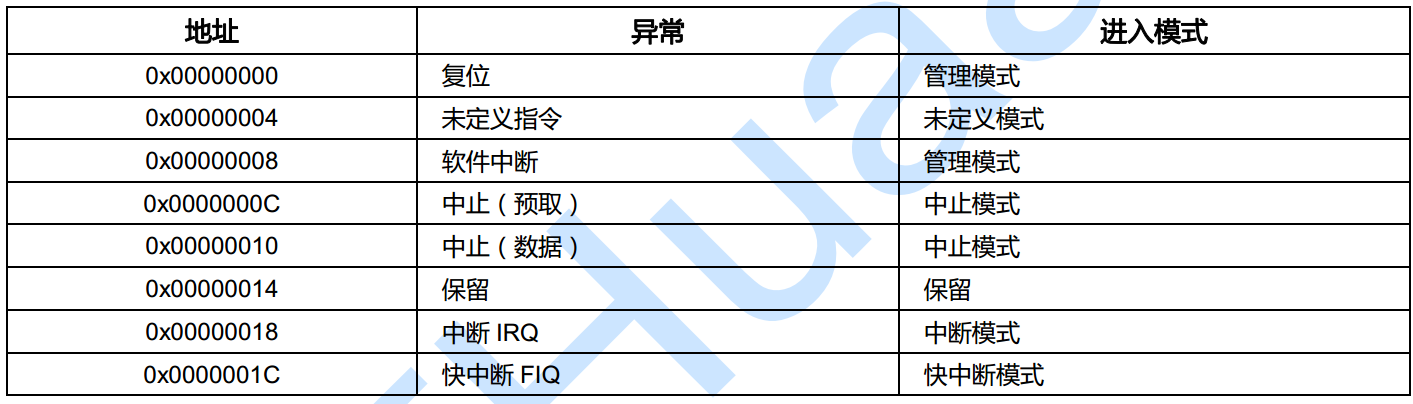

异常的类型: Reset undefined instruction swi prefetch/bort data/abort Reserved IRQ FIQ

处理器的模式: 每一个异常对应一种模式, 但不是一一对应关系

如下,中断向量表

4.2 ARM 异常处理过程

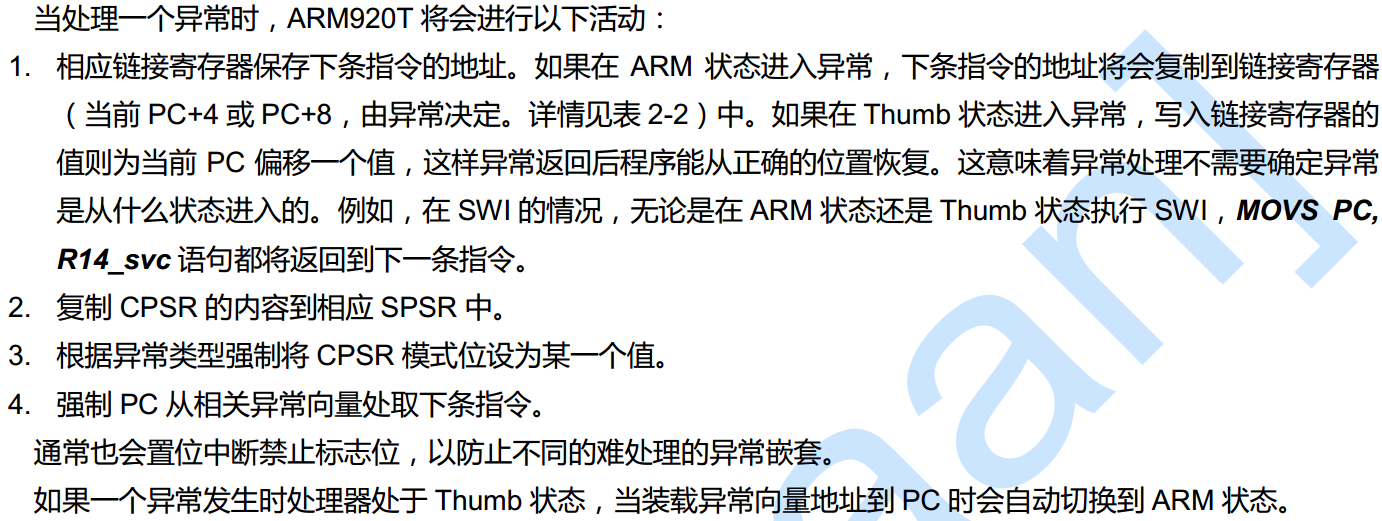

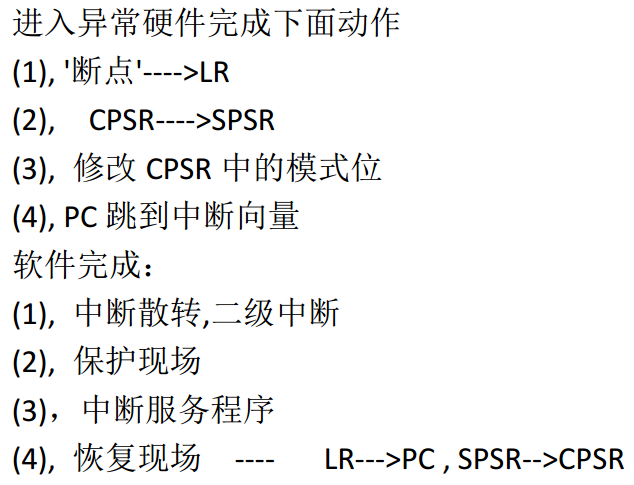

下面的步骤都是硬件自动完成的,软件不需要完成。

解释:

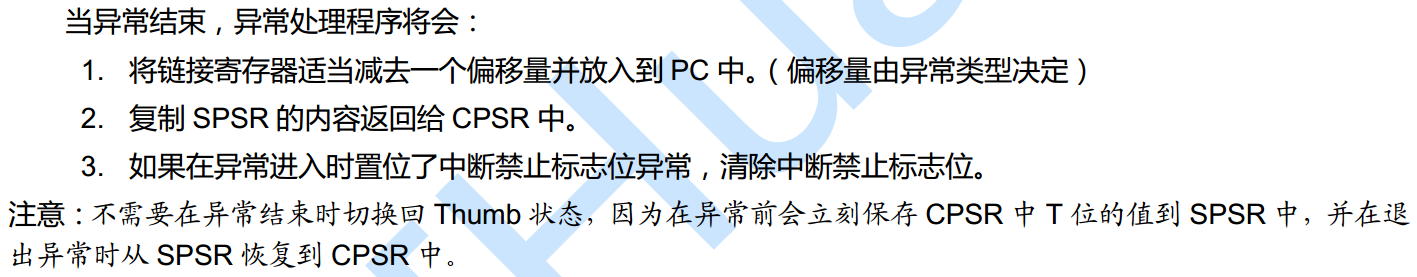

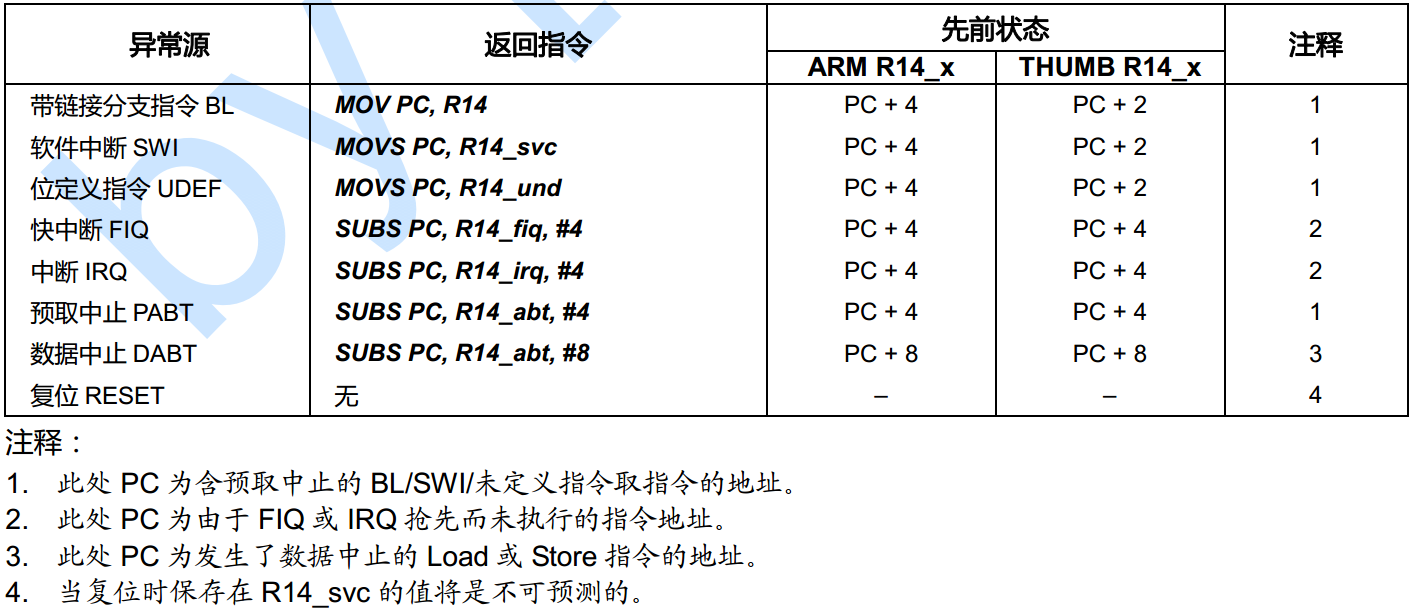

4.3 异常进入/返回总结

注意:

PC 在不同情况含义不一样,比如:PC(excute)=PC(fetch) - 8, 程序进入异常时LR 值(LR= PC-4)异常会清除处理器的流水线。

每种异常发生的时机不一样,对于中断而言,指令还未被执行就产生了,对于 BL/SWI/UNEF 而言, 指令是执行过了的。

当发生预取中止, 将预取的指令标记为无效,在指令达到流水线执行阶段执行才进入异常,如果指令在流水线中因为分支而没有被执行,异常不会发生。

当发生数据中止异常时,异常会在访存阶段发生。

PABT 和 DABT 常结合 MMU 和 OS 来使用,abort 的处理程序就必须找出异常中断的原因,使要求的数据可用,并重试被中止掉的指令。

4.4 ARM 的存储系统

4.4.1 存储器与存储控制器

存储器单元:存放数据的位置,地址是挂在系统总线。

存储控制器:初始化存储器器件,有对应的寄存器配置,寄存器是挂在系统总线上。

4.4.2 存储器存储数据格式

大端格式: 8051 ARM 处理器将最高位字节保存在最低地址,最低字节保存在最高地址

小端格式: ARM, X86 一个字当中最低地址的字节被看作是最低位字节,最高地址的字节被看作是最高位字节