这篇文章主要给大家介绍一下STM32F7x6的系统架构。

STM32F7系列三个提高处理器性能的特性:

第一个是STM32F7拥有两个独立的机制实现零等待执行性能,从Flash执行的时候零等待的一个执行性能,一个是ST的ART加速器,一个是M7内核独有的可用于内部和外部存储器的一级缓存,在STM32F7里拥有4KB的指令缓存和4KB的数据缓存。

第二个是STM32F7拥有AXI和多层AHB总线矩阵,除了内核作为总线矩阵的MASTER以外,还有两个通用DMA,一个以太网专用DMA,一个USB专用DMA,还有硬件图形加速器都是作为总线矩阵的MASTER。这些DMA可以在CPU不参加的情况下进行数据的传输来减少CPU的负荷,提高处理器的性能。

第三个是大容量分布式SRAM,在STM32F7系列里有多大320KB的系统RAM,包括连接到总线矩阵的SRAM1(240KB),SRAM2(16KB)和64KB数据的TCM RAM。除此之外,还有16KB的指令TCM RAM和4KB的备份SRAM,这4KB的备份SRAM的地址范围为0x40024000-0x40024FFFF。

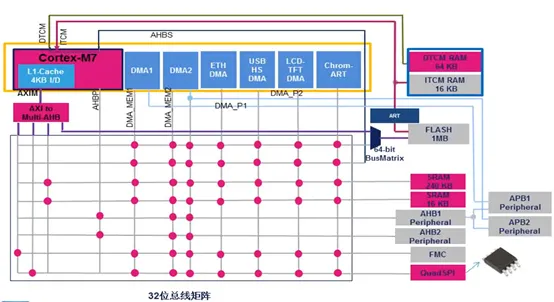

下面我们说一下STM32F7的整体系统框架

STM32F7是基于Cortex-M7的内核,它拥有更高的运行和数字信号处理能力,STM32F7还拥有更多的总线主设备,除了内核,我们之前也有说到STM32F7还有两个通用的DMA,以太网专用的DMA、USB专用的DMA、LCD-TFT DMA和一个通信加速器。

STM32F7还有更多的片上SRAM,包括SRAM1、SRAM2和数据TC SRAM,加起来一共有320bit。它还有64位宽的AXI总线,AXI总线带来了更大的取指和数据读取宽度,在AXI总线接口上Cortex-M7内部带有一级缓存,这大大提高了从外部存储器执行的性能。连接到TCM接口的64KB的DTCM RAM和16KB的ITCM RAM,这两个部分的RAM可以被内核直接访问,访问的速度更快。

STM32F7还支持更多的外设,比如说Quad SPI等。

整个STM32F7的系统架构是基于两个子系统

一个是AXI转多层AHB总线桥,它实现了从AXI到AHB协议的转换,包括一个AXI转64位AHB桥,它连接到内部的FLASH;三个AXI转32位AHB桥,连接到下面大的多层AHB总线矩阵。

另一个子系统就是下面大的多层AHB总线矩阵,这个多层AHB总线矩阵连接了所有的MASTER和SLAM,它包括一个32位的多层AHB总线矩阵、一个64位的小的多层AHB总线矩阵,小的多层AHB总线矩阵它将来自CPU的64位的总线和来自通用DMA的32位AHB总线连接到内部FLASH。

FLASH接口

FLASH接口包括三个主接口,分别为64位ITCM接口、64位AXI/AHB接口和32位AHB寄存器接口

DMA传输

DMA传输可以访问到映射到AXI接口的内部FLASH、SRAM1、SRAM2、FMC和Quad SPI。DTCM可以通过Cortex-M7的AHBS总线进行访问,但是需要注意的是AHBS不能访问ITCM总线。DMA不能访问映射到ITCM总线的存储空间,包括ITCM-RAM和映射到ITCM地址的FLASH空间。

DMA1只能实现外设和存储器之间的传输,存储器到存储器的传输只能通过DMA2来实现。