来源:内容来自 原理 ,谢谢。

什么是登纳德缩放比例定律?为什么芯片里总有那么一部分甚至一大部分是不能同时工作的?那为什么我们还要费尽心思往集成电路里加更多的晶体管呢?暗硅又是一种怎样概念?

早在1971年,英特尔推出了首个商用,速度仅有740kHz的计算机芯片Intel-4004。在此之后,芯片速度得到了迅速的发展,在不到30年后的2000年就已经突破了2GHz,达到了近3000倍的增长。然而2000年似乎成为了芯片发展速度的一个坎,直到如今市场上多数处理器也在3GHz左右徘徊。

△ Intel C4004微处理器。(图片来源:Wikipedia)

2001年IBM首先制造出了世界上第一个双核处理器,使得两个低速度、低功耗的处理器能在性能方面与当下的单个高速度的处理器相匹敌,并由此开辟了并行化体系结构的市场。

2004年,在AMD发布了其第一个双核处理器之后,英特尔更是宣布取消其对4GHz处理器的研究,与当时一众同行一起投入到了多核处理器的研发当中。由此,计算机芯片的发展从之前的更高速的单核研究转变到了同等甚至更低速的多核研究。究其原因,主要来自于更高速的处理器的功耗和散热已经达到了不可忽视的地步。

2013年,ITRS在第二次修正了摩尔定律的同年发表评论,将功耗列为了计算机发展的主要挑战。那么这个挑战从何而来呢?为什么在如此迅速发展之后突然遇到了门槛呢?这就不得不提到芯片行业发展的又一个定律——登纳德缩放比例(Dennard Scaling)。

在了解登纳德缩放比例定律之前,我们先来看看晶体管的功耗是如何计算的。晶体管的功耗大体分为两类:一类是静态功耗,一类是动态功耗。静态功耗的计算比较好理解,就是常规的电压乘以电流。而晶体管在做 1和 0的相互转换时会根据转换频率的高低产生不同大小的功耗,我们把这个功耗叫做动态功耗,与电压的平方以及频率成正比。

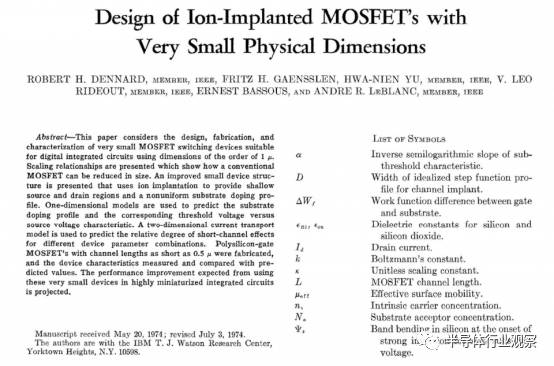

△罗伯特登纳德在1974年发表的论文。(图片来源:Robert Dennard)

1974年,也就是高登摩尔第一次修正摩尔定律的前一年,罗伯特登纳德在发表的论文 “Design of ion-implanted MOSFETS with very small physical dimensions”[1]中表示,晶体管面积的缩小使得其所消耗的电压以及电流会以差不多相同的比例缩小。也就是说,如果晶体管的大小减半,该晶体管的静态功耗将会降至四分之一(电压电流同时减半)。芯片业的发展目标基本上是在保证功耗不变的情况下尽可能提高性能。那么根据登纳德缩放比例,设计者可以大大地提高芯片的时钟频率,因为提高频率所带来的更多的动态功耗会和减小的静态功耗相抵消。于是,登纳德缩放比例定律同摩尔定律一起引领了芯片行业30多年的飞速发展。因为在往同面积电路中集成更多晶体管的时候,提高芯片时钟频率成为了一个“免费的午餐”。

事情发展到2005年前后。在摩尔定律的指导下当晶体管的大小越做越小时,量子隧穿效应(指像电子等微观粒子能够穿入或穿越位势垒的量子行为)开始慢慢介入,使得晶体管漏电现象开始出现。漏电现象的出现打破了原先登纳德所提出的定律,使得晶体管在往更小工艺制作时候的静态功耗不减反增,同时也带来了很大的热能转换,使得芯片的散热成为了急需解决的问题。如果散热做的不好,芯片的寿命将大大减少甚至变得不稳定。在这种情况下,提高芯片的时钟频率不再是免费的午餐。相反,在没有解决晶体管漏电的问题之前,单纯的增加芯片的时钟频率因为随之而来的散热问题而变得不再现实。毕竟没人希望今后需要通过不停的往自家电脑主机里灌水来散热。于是芯片研究商们开始纷纷停止高频芯片的研发,转而向低频多核的架构开始研究。这才有了从2001年开始的第一个双核芯片到现在普遍家用电脑的4核芯片,再到如今英特尔最新架构KnightLanding上的64核的发展。

然而从单核向多核的发展并没有从根本上解决问题。因为芯片研发商仅仅是停止了高频单核的研发,但并未停止往同面积的集成电路内加入更多的晶体管。不然就不会有从双核到四核再到八核的发展了。那么正如之前所提到的,在登纳德缩放比例不再适用,在晶体管越做越小并因晶体管漏电而导致芯片发热越来越严重的今天,芯片制造商们又是如何解决功耗以及散热的问题呢?答案是,没有解决!可能你引以为傲,刚买的八核处理器只不过是一个摆设。要解释这个问题,就需要了解暗硅这个概念。

暗硅这个概念是在2011年在计算机体系结构会议ISCA中首次提出的[2]。作者发现在后登纳德时代,为了在现有的散热技术上保证芯片不至于过热以及功耗不至于过大,如今多核芯片中已经有一部分不能和其余部分同时使用。举个简单的例子,对于一个65纳米下的4核处理器,假如额定功耗允许其四个核能够同时全速工作。当工艺缩小到32纳米的时候,等面积的处理器现在能容下16核了,但是能够同时工作的还是只有四个核。而这块不能和其他部分同时使用的12个核就称为暗硅。Igor Markov在论文 “Limits on fundamental limits to computation”中提到,按照如今的发展速度,现代处理器的暗硅部分很快就能大到99% [3]。也就是说,按照如今的发展,不久之后的芯片,即便是再牛,在同一时间能够利用的也只是1%。加上越来越多核数的集成,内部连接所导致的的功耗也正在逐渐超过核内运算所导致的功耗。基于这个结果,微软和IBM共同预测了多核芯片研发在不久将来的终结[4]。

那么问题来了,既然芯片大部分会成为暗硅,那么芯片商为什么还要不断地往同面积的芯片里加入更多的核呢?为什么不通过把芯片直接做小来减少成本呢?首先芯片面积的成本根本不重要。随着芯片越做越小,芯片的面积成本所占的比重越来越小,从而使得芯片成本不会因为芯片面积缩小而线性缩小。芯片的引脚和封装开始占设计成本越来越重要的部分。其次就是商业原因。尽管多出来的核数大多数都是暗硅,但八核处理器听起来就是比双核牛逼吧?就是容易在消费者心里留下更深的印象吧?而且通过一些程序和编译器的优化设计也确实有可能让更多的核在更低频的工作,从而达到系统性能的提升。至少八核处理器的潜力大过双核,特别是对一些特别任务的加速。虽然这些特殊的任务大部分用户在大部分时间里都不会遇到。

那么面对这些问题,科学家们又是怎么应对的呢?在业界,ARM率先提出了异构系统架构(big.LITTLE以及前段时间刚发布的DynamlQ),在芯片里同时放入大核(高频)与小核(低频)。核的利用根据所运行的程由操作系统决定,从而达到尽量减小功耗目的。在学术界,洛夫兰道尔(Rolf Landauer)在1961年的论文中提出这样一个概念[5]。因为擦掉一个比特的信息用于重写至少需要消耗kTln2(k是波尔兹曼常数,T是温度)的能量,如果我们能建立一个计算模型,将每个输入产生的输出信号的能量保存起来,为新的信号输入提供能量,那我们是否能创造出一个零热量产生的计算方式。这种计算模型被称之为可逆计算。

兰道尔的想法的前半部分(即擦掉一个比特的信息用于重写至少需要消耗kTln2的能量)在2012年在实验中得到了证实之后[6],可逆计算在学术界再次引起涟漪。虽然零热量产生的计算方式在海森堡不确定性原理的限制下被证明为不可能[7],科学家利用超导体材料将之前提到的擦掉1比特信息所需要的能量减少到了kTln2以下[8]。同时,科学家们也开始通过量子电路的设计来模拟可逆计算的计算模型,从而达到更小的计算功耗[9]。虽然这些研究还处于开始阶段,离实际应用还需要很长一段时间,但是众多科学家们对突破功耗极限的努力依然能让我们看到芯片发展的光明前途。

今天是《半导体行业观察》为您分享的第1295期内容,欢迎关注。

关注微信公众号 半导体行业观察,后台回复关键词获取更多内容

回复 科普 ,看《第三代半导体科普,国产任重道远》

回复 争霸 ,看《晶圆代工争霸战四部曲(了解各晶圆厂的前世今生,非常详细!建议收藏!) 》

回复 指南 ,看《半导体专业留学海外指南(1): 专业方向选择》

回复 财报 ,看《18家半导体企业财报汇总,几家欢喜几家愁》

回复 国产手机 ,看《谨以此文献给国产手机背后的劳动者》

回复 指纹 ,看《面板厂将指纹识别芯片革命到底 》

回复 OLED ,看《一文看懂我国OLED全产业链,除了京东方还有啥值得骄傲的?》

回复 缺货 ,看《半导体行业缺货危机重现 这10大领域面临洗牌?》

【关于转载】:转载仅限全文转载并完整保留文章标题及内容,不得删改、添加内容绕开原创保护,且文章开头必须注明:转自“半导体行业观察icbank”微信公众号。谢谢合作!

【关于征稿】:欢迎半导体精英投稿(包括翻译、整理),一经录用将署名刊登,红包重谢!签约成为专栏专家更有千元稿费!来稿邮件请在标题标明“投稿”,并在稿件中注明姓名、电话、单位和职务。欢迎添加我的个人微信号 MooreRen001或发邮件到 jyzhang@moore.ren

【关于征稿】:欢迎半导体精英投稿(包括翻译、整理),一经录用将署名刊登,红包重谢!签约成为专栏专家更有千元稿费!来稿邮件请在标题标明“投稿”,并在稿件中注明姓名、电话、单位和职务。欢迎添加我的个人微信号 MooreRen001或发邮件到 jyzhang@moore.ren