SiC 作为第三代宽禁带半导体具有击穿电场高、热导率高、电子饱和速率高、抗辐射能力强等优势,在各种各样的电源应用范围在迅速地扩大。其中一个主要原因是与以前的功率半导体相比,SiC 使得高速开关动作成为可能。但是,由于开关的时候电压和电流的急剧变化,器件的封装电感和周边电路的布线电感影响变得无法忽视,导致漏极源极之间会有很大的电压尖峰。这个尖峰不可以超过使用的 的最大规格,那就必须抑制尖峰。

本文引用地址:MOS_DS电压尖峰产生的原因

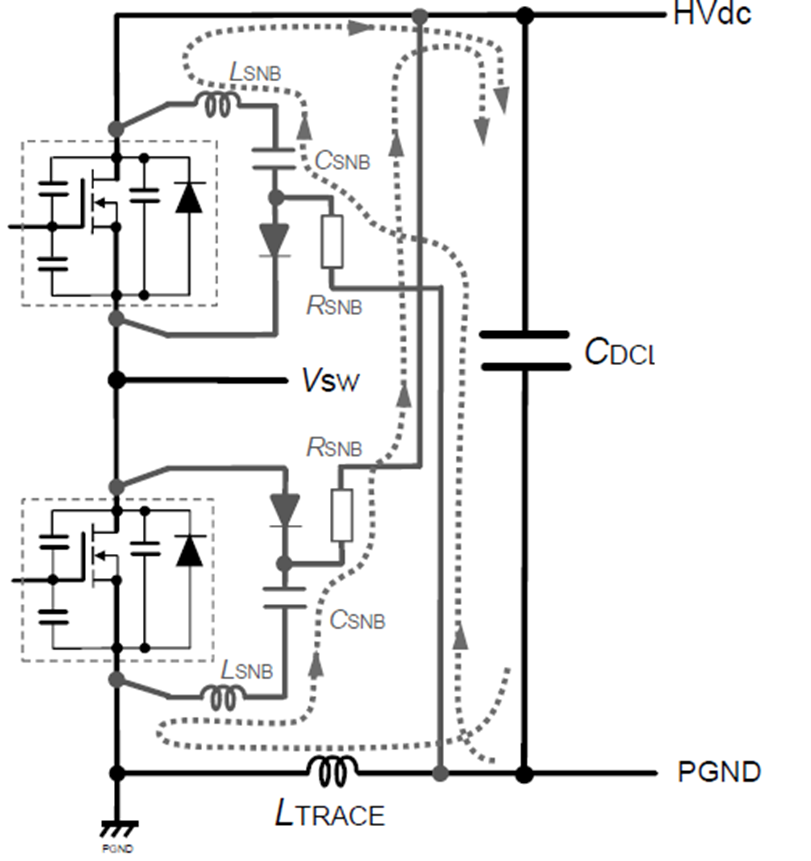

在半桥电路中,针对MOS漏极和源极产生的尖峰抑制方法之一就是增加缓冲电路,其设计方法说明了漏极源极之间的电压尖峰是由于在Turn ON 时流过的电流的能量储存在线路和基板布线的寄生电感中,并与开关元件的寄生电容共振所产生的。

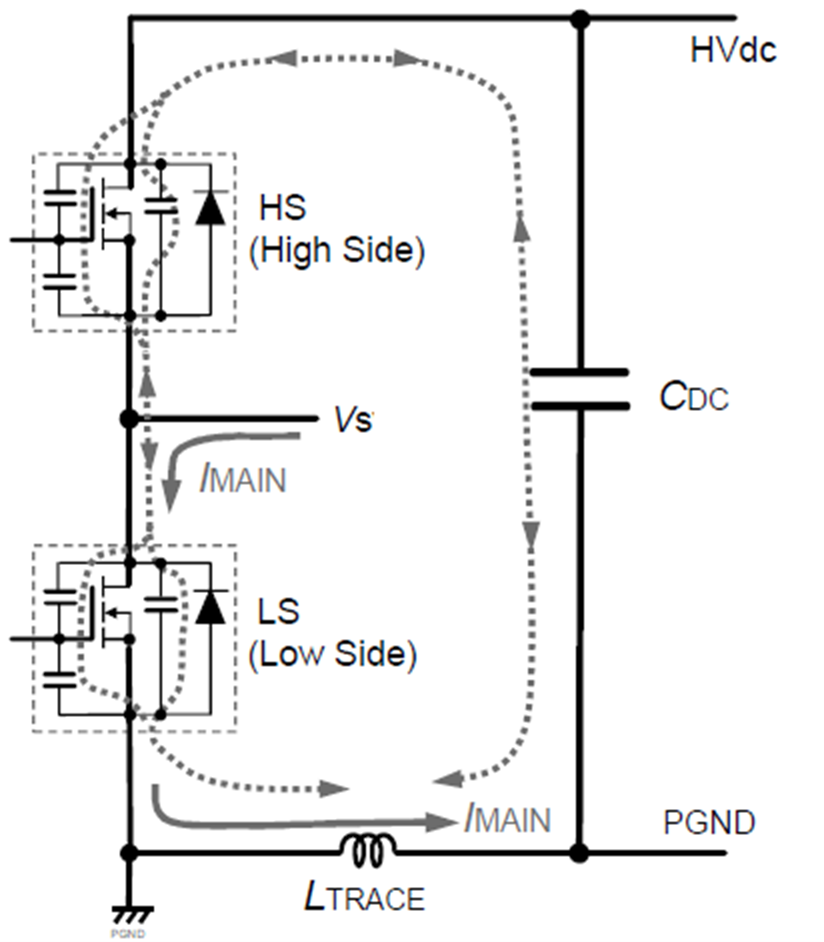

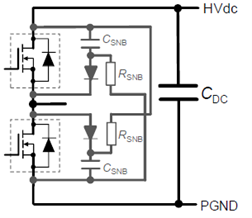

图 1 图示尖峰产生时的振铃电流路线

图1由HS (High side) 和LS (Low side) 的开关元件组成的半桥结构。

当LS 元件Turn ON时,开关电流IMAIN流动的情况。这个IMAIN通常从Vs流入再通过配线电感LTRACE。

当LS 元件Turn OFF 时,在LTRACE 流动的IMAIN 通常会通过接在输入电源HVdc-PGND 之间的Bulk 电容CDC,经由HS 元件和LS 元件的寄生电容如图中虚线所示流动。

此时,在LS 侧漏极源极之间LTRACE和MOSFET 的寄生电容COSS(CDS+CDG)之间发生谐振现象,在漏极源极之间产生尖峰。

VDS_SURGE:尖峰的最大值

VHVDC:HVdc 端的电压

ROFF:MOSFET Turn OFF 时的电阻

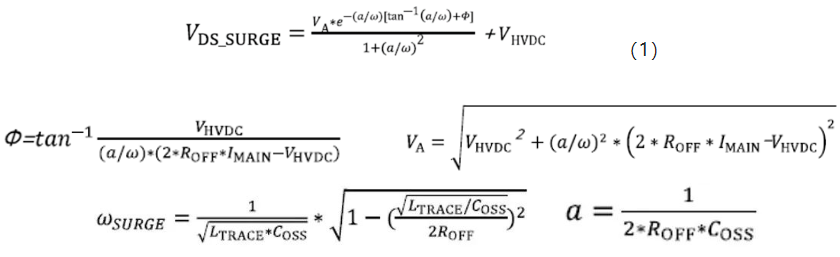

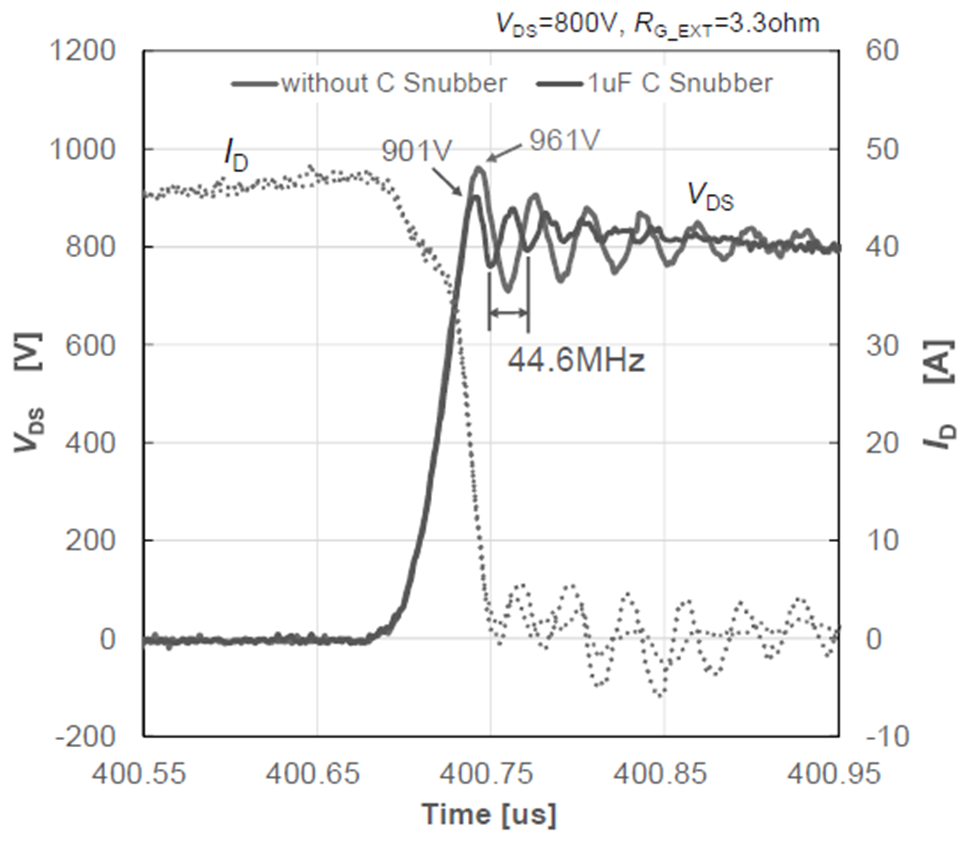

如图2 HVdc 电压为800V 时,VDS_SURGE为961V,振铃频率约为33MHz。使用方程式(1)根据该波形计算出LTRACE 约110nH。

图2 Turn OFF 电压尖峰波形

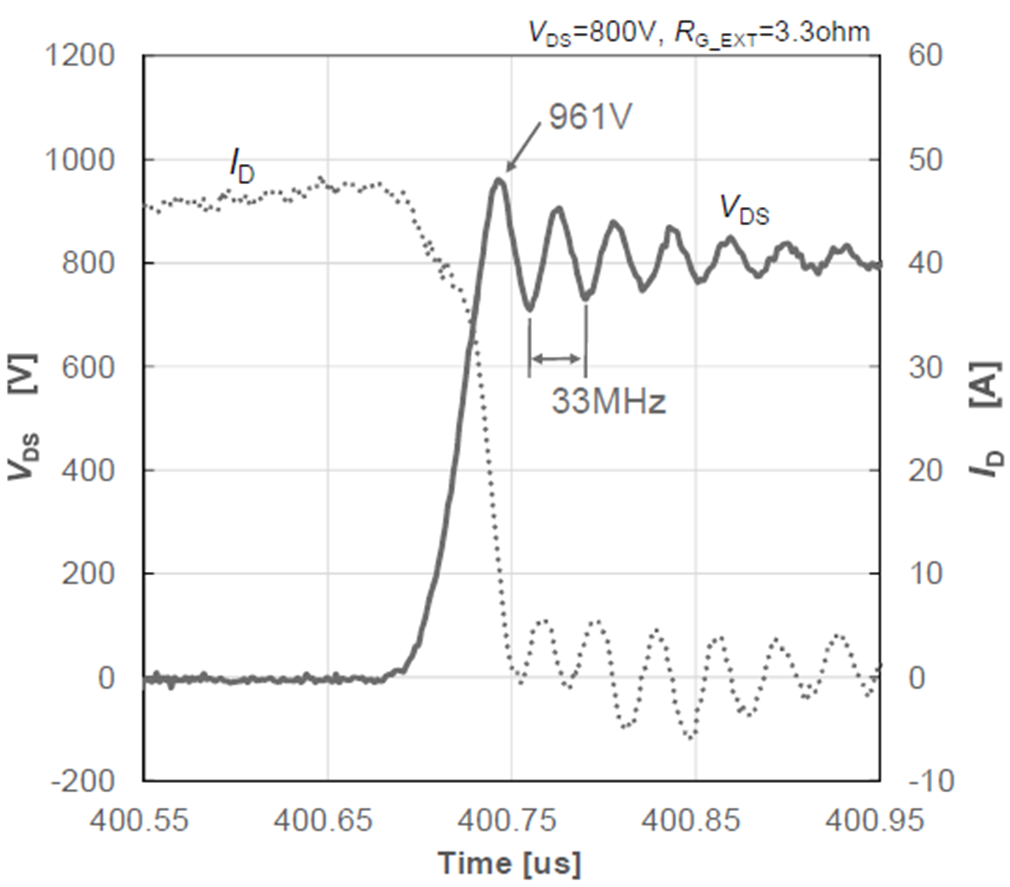

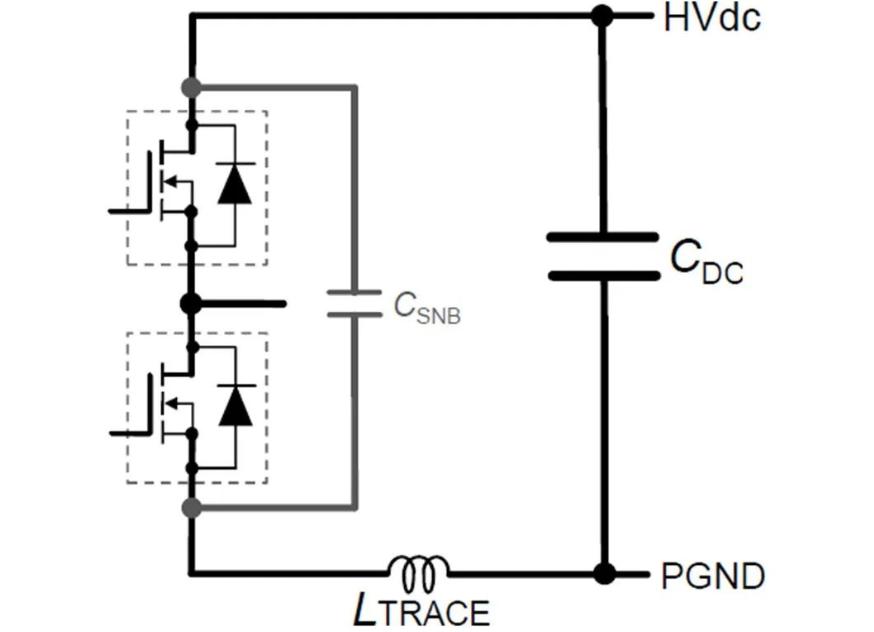

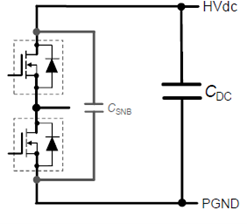

下面在电路中添加图3所示的缓冲电路CSNB,这个时候电压尖峰降低了50V 以上(约901V),振铃频率也变大为44.6MHz,由图4可知,包含CSNB 在内的电路网中的LTRACE 变小了。同样,使用式(1)可算出LTRACE 约为71nH。

图3 CSNB缓冲电路

图4 CSNB缓冲电路减小Turn OFF 尖峰电压

一般需要线路布局设计为配线电感最小化,但通常优先考虑的是元件的散热设计,因此布线设计不一定理想。因此通过尽可能在开关装置附近布置缓冲电路,以形成旁路电路,将电压尖峰产生的源头——布线电感最小化,还可以吸收积蓄在布线电感中的能量。这样就可以将开关元件的电压钳位住,缩小Turn OFF 电压尖峰。

缓冲电路的种类

缓冲电路分为由电阻、线圈和电容器等被动部件组合的电路,和包含半导体元器件的主动电路。

a. CSNB缓冲电路

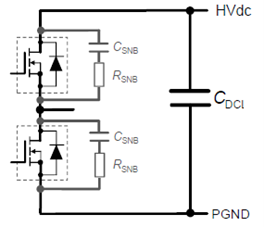

b. RC 缓冲电路

c. RCD 缓冲电路

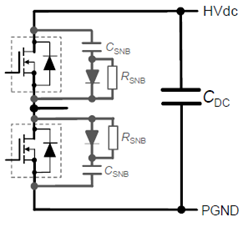

d. 非放电型RCD 缓冲电路

为了更好地发挥其的效果,必须将这些缓冲电路尽可能布局在在开关元件的附近。

a. CSNB缓冲电路零件数目少,但必须连接到桥式结构的上部和下部之间,因此缺点是线路会变得较长,因此通常不是用分立元器件,而是多用2合1 的分立元器件模块。

b. RC 缓冲电路可在各开关元件附近能布局缓冲电路,不过,必须确保每次元件Turn ON 时CSNB 中积存的全部能量均由RSNB 消耗掉。因此,当开关频率变高时,RSNB 所消耗的电力可能会变为数W,而CSNB 很难很大,所以抑制尖峰的效果也会变得有限。此外,RSNB 的尖峰吸收能力有限,因此抑制效果也会受限。

c. RCD 缓冲电路的RSNB 消耗的电力与(b)相同,但因为只经由二极管吸收尖峰,比起(b)的吸收效果高、更实用。但是,需要注意使用的二极管的恢复特性,因为吸收尖峰时的电流变化大,需要极力减少缓冲电路的配线电感。另外,如果将RSNB 与CSNB 并联,在动作上也是相同的。

d. 非放电型RCD 缓冲电路的RSNB 只消耗CSNB 所吸收的电压尖峰能量,CSNB 所积蓄的能量不会每次开关都充分释放出来。因此,即使开关频率加快,RSNB 的消耗功率也不会变得很大,可以将CSNB 增大,大幅提高电路的抑制效果。但样线路布局变得复杂,如果不是4 层以上的基板,布线会极为困难。

如上所述,这里介绍的缓冲电路各有长短,需要根据电源电路结构和转换功率容量选择最佳的缓冲电路。

缓冲电路的设计方法

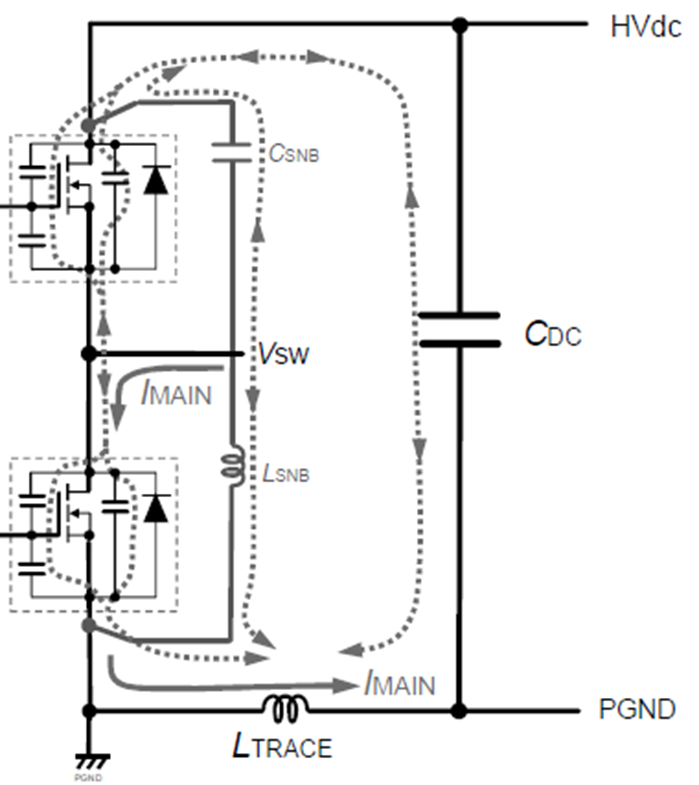

1.图5所示的缓冲电路是通过CSNB 吸收LTRACE 积蓄的能量。因此,在缓冲电路中形成的LSNB 必须比LTRACE 小。由于CSNB 中积蓄的能量基本不放电,静电容量越大电压尖峰抑制效果变好,但使用的电容器的等价串联电感 (ESL) 也必须考虑到LSNB 中。一般来说,电容器的尺寸越大ESL 越大,在选择静电容量时要注意。

图5 CSNB缓冲电路

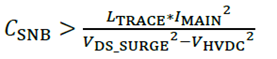

为了将LTRACE 中积蓄的能量全部用CSNB 吸收, 需以算式(2)所示静电电容为依据选定电容。

(2)

(2)

2.RC 缓冲电路的设计

图6所示为RC缓冲电路动作时的电流路径与CSNB缓冲电路一样:

图6 RC 缓冲电路

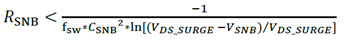

CSNB的数值由算式(2)决定,而RSNB 的参考值根据算式(3)求得。

(3)

(3)

fSW:开关频率

VSNB:放电缓冲电压(VDS_SURGE 的0.9 倍)

决定RSNB 之后,以算式(4)计算出RSNB 的消耗功率,选定功率满足要求的电阻。

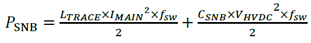

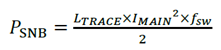

(4)

(4)

对于RC 缓冲电路,算式(4)追加了第二项,因为fSW 或VHVDC越高RSNB 所消耗的电力越大,PSNB 太大导致电阻选定困难时,必须降低CSNB 的静电容量值重新计算。

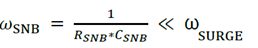

另外,为了RC 缓冲电路充分吸收电压尖峰,RSNB 和CSNB 的谐振频率ωSNB 必须比电压尖峰的谐振频率ωSURGE 低很多,需要结合算式(5)所示的RC 缓冲电路的谐振频率ωSNB 来确认。

(5)

(5)

3.放电型RCD 缓冲电路的设计

放电型RCD 缓冲电路的设计基本上与RC 缓冲电路相同。只是由于是通过二极管吸收的尖峰,所以不需要通过算式(5)确认谐振频率。并且,二极管必须选定为恢复电流小的型号。

4.非放电型RCD 缓冲电路的设计

非放电型RCD 缓冲电路与放电型RCD 缓冲电路不同,RSNB消耗的电力仅限于电压尖峰的能量,用于抑制容许损失的RSNB的选择范围很广。因此可以增大CSNB 的静电容量,提高钳位的效果。CSNB 由算式(2)决定,RSNB 由算式(3)决定,而RSNB 的消耗功率由算式(6)决定,没有算式(4)中包含CSNB 及fsw 的第二项。因此,由CSNB 或fsw 产生的消耗功率增加基本没有,能选择大的静电容量的CSNB,不仅仅缓冲电路的钳位效果更好,还能对应fsw 的高频化。

(6)

(6)

图8所示为非放电型RCD 缓冲电路动作时的放电路径。因为上臂的尖峰朝向PGND、下臂的尖峰朝向HVdc,放电流经由RSNB 流动,不那么受线路电感影响。另一方面,连接到MOSFET 的漏极源极之间的布线电感LSNB 因为电流变化大,电感值需要尽量小。

图8 非放电型RCD 缓冲电路动作时的放电路径

封装不同而造成的电压尖峰差异

最后说明的是,Turn OFF 尖峰根据封装的不同而有差异。图9是 SiC MOSFET 的代表性封装, (a)是被广泛采用的TO-247-3L,(b)是近几年渐渐扩大采用的用于驱动电路的源极端子(即所谓的开尔文接法)的TO-247-4L。

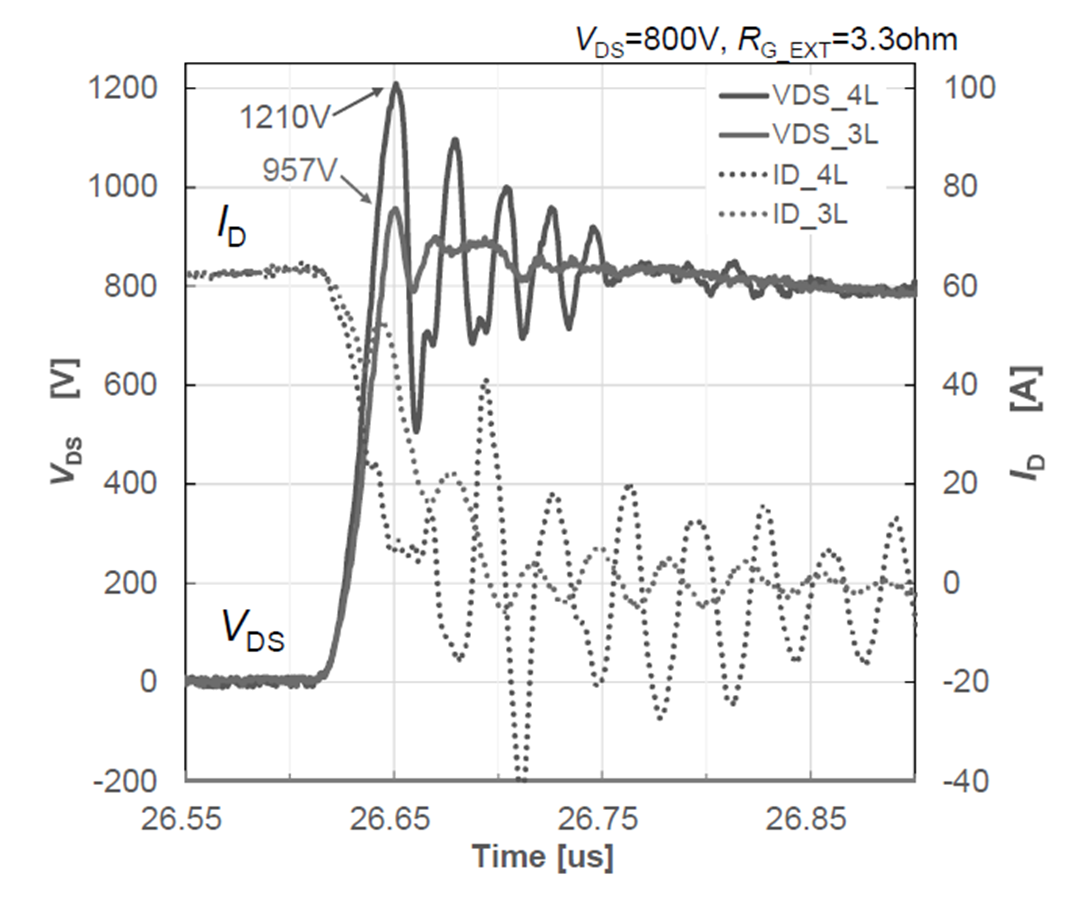

4L 型与3L 型相比,改变了驱动电路路径,使开关速度加快。由于这个原因,Turn ON 电压尖峰和Turn OFF 电压尖峰变得更大。图10为3L 类型和4L 类型的Turn OFF 电压尖峰的对比波形。VDS=800V、RG_EXT=3.3Ω、ID=65A 时的Turn OFF波形,漏极源极间电压尖峰3L 类型为957V,而4L 类型则为1210V。

图10

如上所述,桥式电路中的MOSFET 的栅极信号在MOSFET之间相互关联、动作,并在栅极源极之间产生预料之外的电压尖峰,其抑制方法需要考虑基板的线路布线,根据情况不同采取不同的对应。