1 说明

实验平台: JZ2440

CPU: S3C2440

SDRAM型号: EM63A165TS-6G

2 SDRAM的一些基本概念

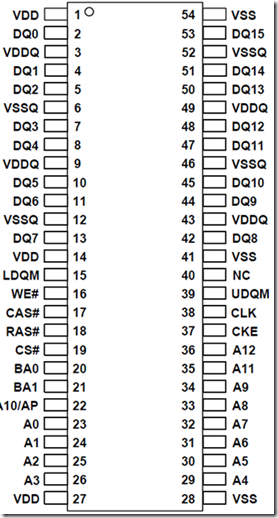

2.1 引脚分配

2.2 引脚描述

A0-A12 :地址线

DQ0-DQ15 :数据线

LDQM、UDQM :数据屏蔽控制

BA0-BA1 :L-BANK地址线

CLK :时钟

CKE :时钟使能

CS# :片选

WE# :写使能

CAS# :列地址选通脉冲

RAS# :行地址选通脉冲

VSS、VSSQ :地

VDD、VDDQ :电源

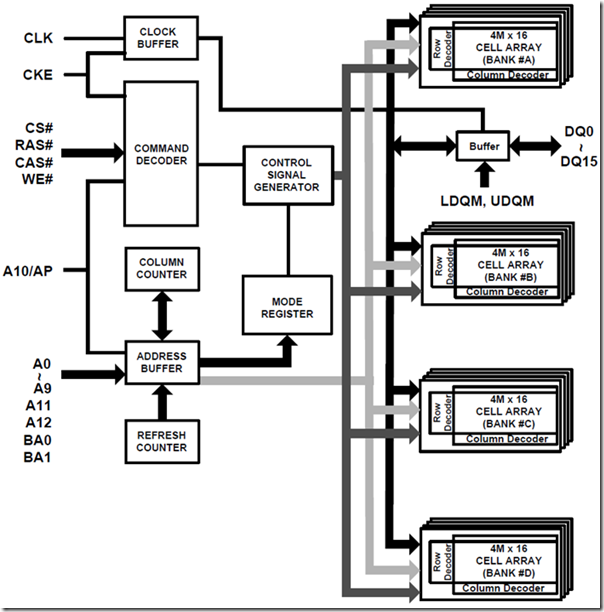

2.3 内部框图

2.4 基本概念

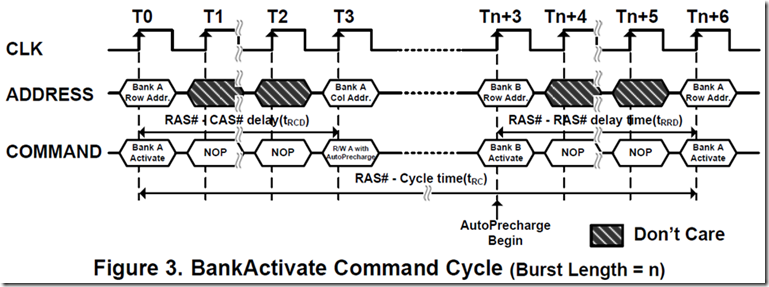

初始化完成之后,想要对一个L-BANK的阵列进行寻址,需要经过片选、选择L-BANK、激活对应的行,选择对应的列并发送读写命令,完成对应操作。

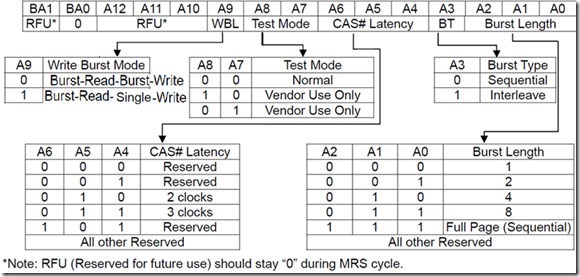

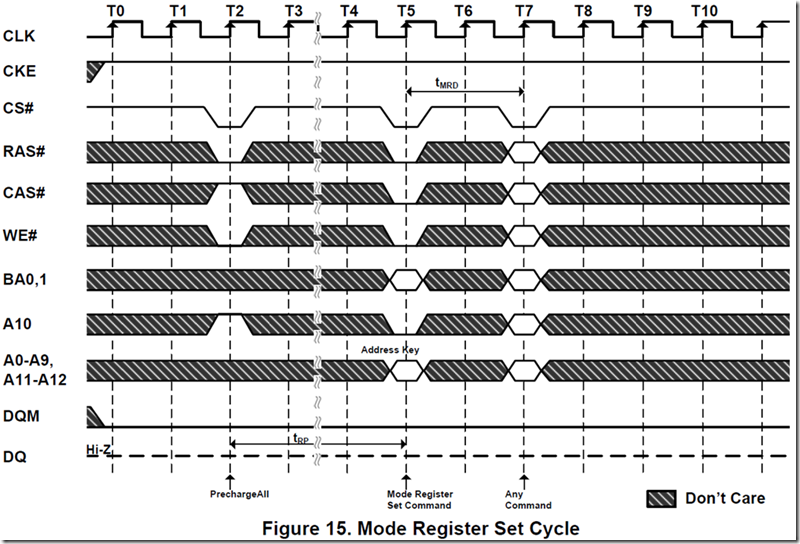

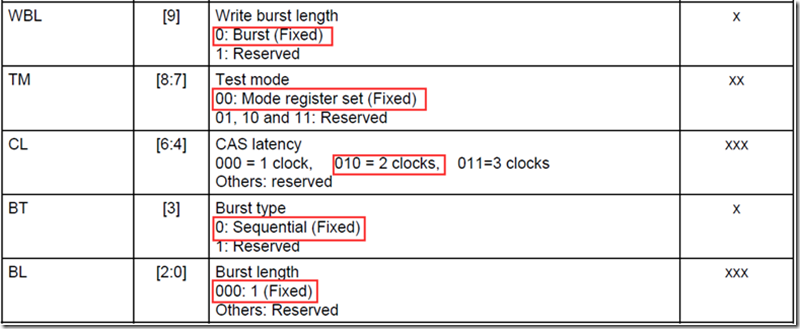

模式寄存器位映射关系

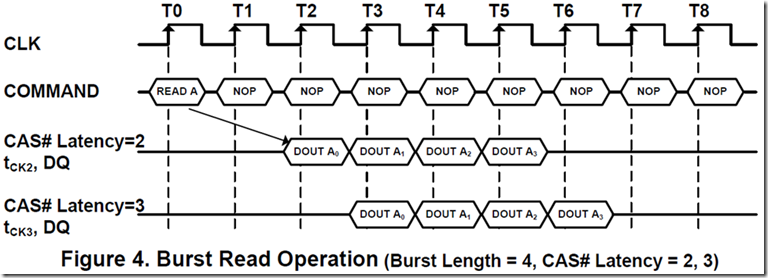

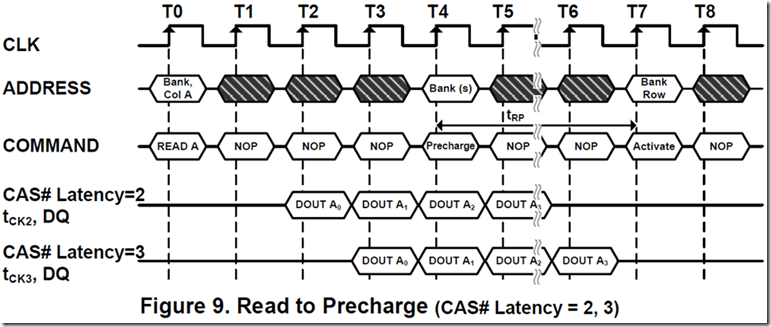

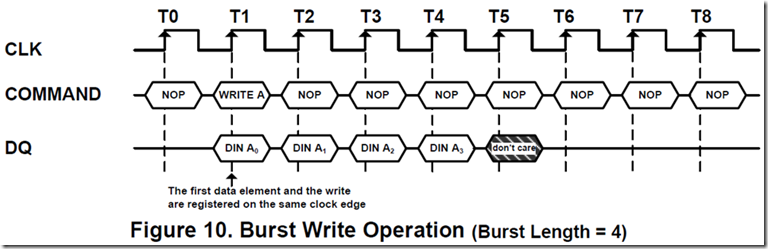

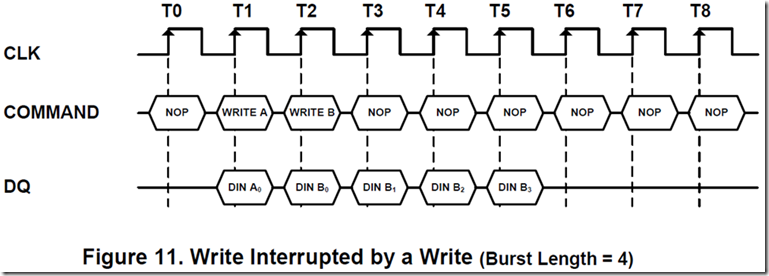

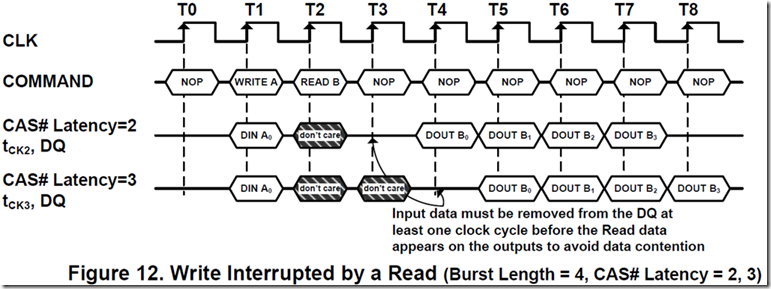

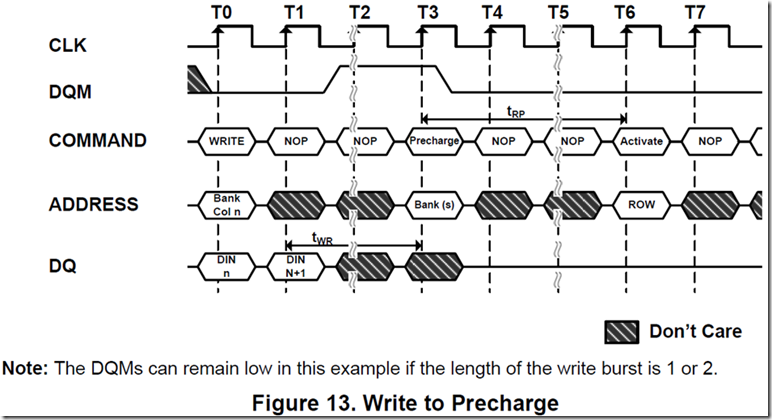

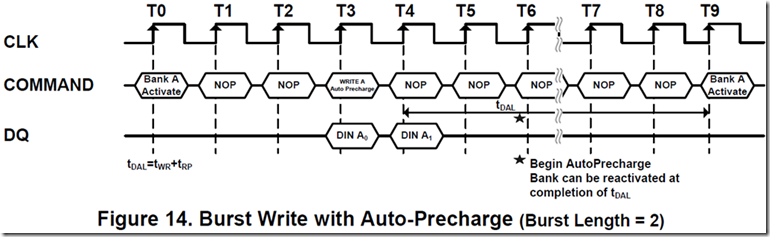

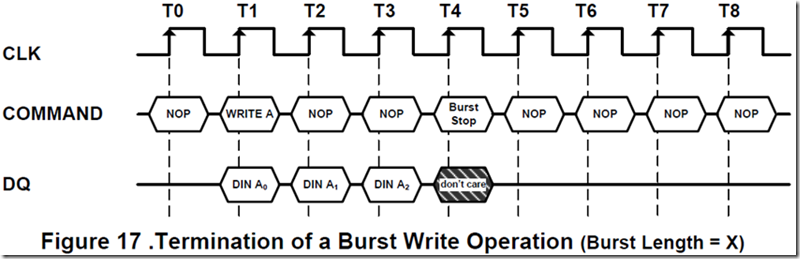

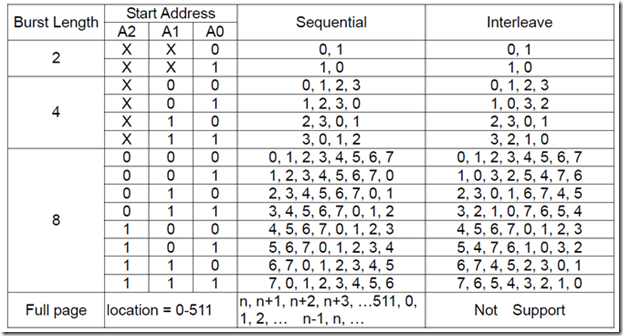

3.3 突发访问规则

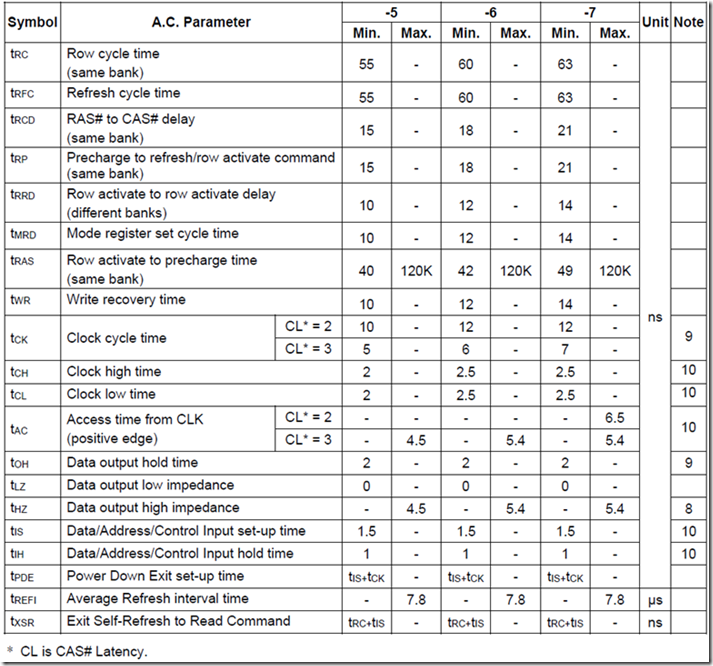

3.4 AC特性

4 S3C2440内存控制器配置说明

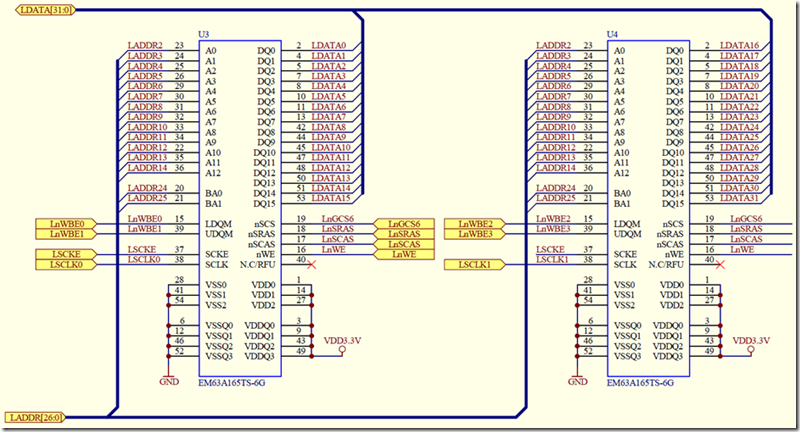

4.1 原理图说明

这是一种两个16位位宽的SDRAM芯片拼接成一个32位位宽的模组接法。

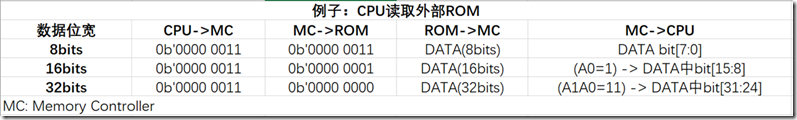

a、A0连接CPU的哪根地址线,是由模组的数据位宽决定的。由于CPU是按字节寻址的,而SDRAM模组是按字寻址的,所以应该进行地址转换。

b、A0、BA0、BA1连接的地址线可以参考用户手册。

4.2 工作原理简述

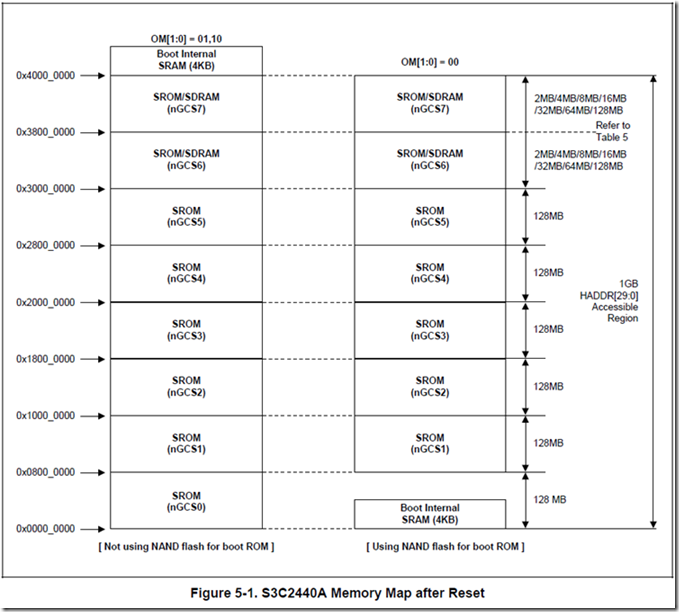

S3C2440的内存空间划分为不同的块,当CPU向内存控制器发出地址,内存控制器根据地址范围,发出对应片选信号到片选引脚,实现对不同设备的控制。

4.3 寄存器设置(clocks = 10ns)

4.3.1 BWSCON

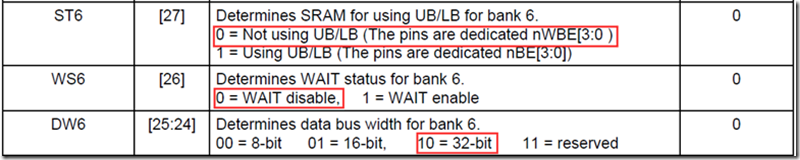

说明

[27]

0:把对应的引脚映射为写字节使能,该位的作用是,对写入数据,屏蔽不需要写入的字节,实现单个字节写操作。

1:把对应的引脚映射为字节使能,该位的作用是,对读入数据,屏蔽不需要读取的字节,实现单个字节读操作。

[26]

如果CPU速度远远大于SDRAM速度,当CPU向SDRAM发送读取命令时,SDRAM未能及时准备好数据,可以使能该位,设置等待,保证能读到数据。

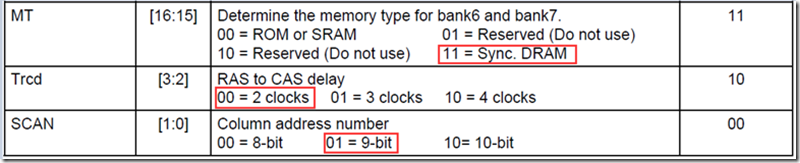

4.3.2 BANKCON6

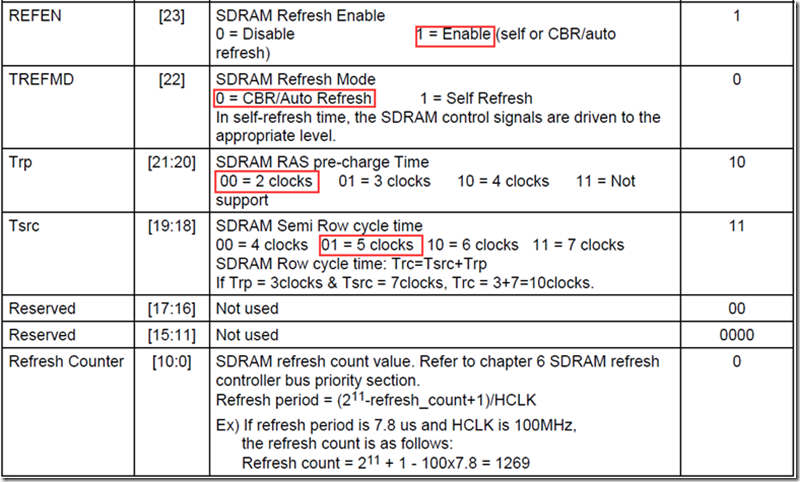

4.3.3 REFRESH

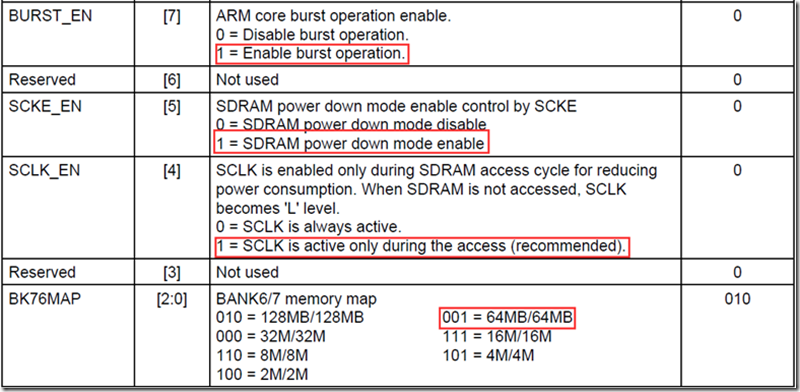

4.3.4 BANKSIZE

4.3.5 MRSRB6

附录1 参考文档

《S3C2440用户手册》

《EM63A165TS Datasheet》

《高手进阶——高级内存技术指南》

《嵌入式Linux开发完全手册》