今年9月底,华为发布了包括Mate 60智能手机在内的一系列产品,几乎覆盖了家庭、个人、出行等所有的数字终端设备应用,构建了一个生态系统。这些产品除了都具备高度智能化的特点外,还用统一的软件构造了所有产品的统一平台,带来了极致的用户体验。

这样平台化的布局其实源于非常现实的、对数字经济的需求。如今,数字经济的关键趋势囊括了数字平台、提供服务转变为体验以及生态系统。数据显示,2016-2025年,全球数据量将达到163 zettabytes,高速发展的智能设备(平板、无人机、智能手机等)将在2030年达到6.9万亿美元的市场规模。

在这个市场规模下,全世界将产生大量数据,要存储并利用好这些数据,又带来了大量对工具、芯片以及软件硬件的需求,而支撑这些应用需求的,正是半导体产业。

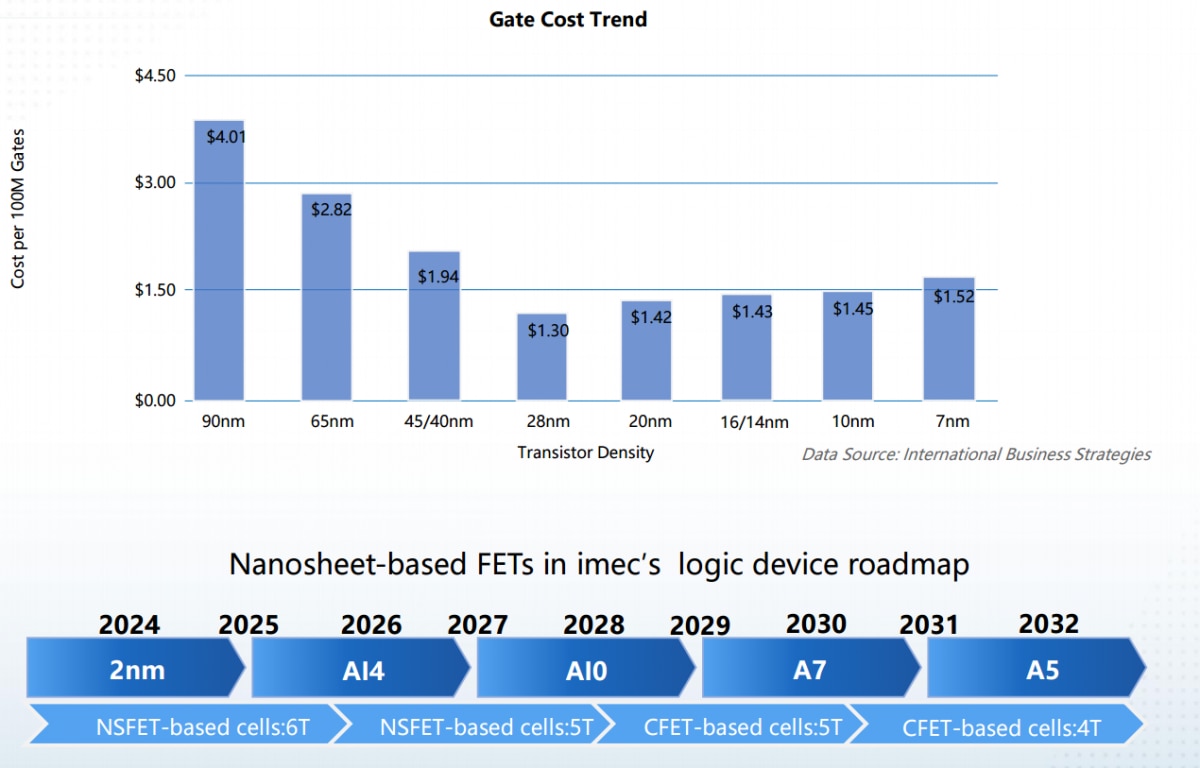

如下图所示,从摩尔定律演进和开发成本的角度来看,2011年整个半导体产业的制造工艺集中在28nm,成本达到历史低点。随着工艺技术的进步,半导体制造成本却开始持续地往回涨,如今要设计和生产一颗7nm以下的芯片,成本非常高。

根据比利时微电子研究中心(IMEC)的预测,从2024年到2032年,芯片制造工艺会从2nm逐步发展到1.4nm、1.0nm、0.7nm甚至0.5nm,不停地往前进步。

“但是很不幸的是,这些先进工艺目前对中国来说是被封锁的。这也是我们EDA产业要突破的地方,因为所有的这些先进工艺都离不开工具软件的支撑。EDA行业一定要领先于工艺的发展,才能支撑工艺的落地。” 在日前举行的第11届EEVIA年度中国硬科技媒体论坛暨产业链研创趋势展望研讨会上,上海合见工业软件集团(UniVista)产品工程副总裁 孙晓阳 从高端芯片面对的发展挑战和机遇出发,重点谈了EDA验证环节对芯片开发的重要性,并介绍了合见工软的最新验证解决方案。

上海合见工业软件集团产品工程副总裁 孙晓阳

上海合见工业软件集团产品工程副总裁 孙晓阳

EDA和整体半导体行业之间的影响

越是高端的应用,越会大量地使用高端芯片。例如智能手机里的SoC芯片,云计算HPC用到的高性能CPU、GPU等,都属于用到先进工艺的高端大芯片。从市场生态发展的角度看,国内的半导体公司越来越多,要抢占市场先机面临的压力也越来越大。再加上流片成本、人员成本越来越高,对各种验证技术的需求就会越来越大。

除了芯片设计和验证本身,系统级封装也一样面临非常大的挑战。由于海量数据需要高性能处理,容量的增加让芯片尺寸越做越大,I/O的高速、大量和多样化,工艺节点提升,多核异构,层次化的软件设计与多源多版本的全栈式集成以及持续增加的IP集成需求,都带来了先进封装复杂度的提升。

“其实整个半导体产业可以看做一个倒三角形,最上面是所有的终端应用,中间是电子系统的软硬件,硬件就包括了芯片,最下层就是EDA工具和IP。” 孙晓阳说到,“半导体要设计并制造出来,需要EDA工具和IP。就像造一栋大楼要先画图,把大楼的结构图、应力分析做出来一样。”

上层广阔且庞大的市场规模,让位于最下层的EDA看起来很不起眼。这也是一个事实,上层玩家非常多,中层的系统厂商和服务商也很多,EDA则相对小众。但正是这样的“小众”,也让EDA行业受整体大环境的影响更小。

以2022年的全球芯片短缺潮为例,当时所有的半导体公司生意都非常好,但到了2023年初,突然间的市场下行,让很多半导体公司开始清库存。在这次下行周期中,位于倒三角上方的系统厂商受市场供需关系影响非常大,虽然影响也传递到了EDA行业,但相对会小很多。

孙晓阳表示,这是因为半导体或系统厂商即使今年生意不好,仍需继续投入研发,“如果不继续做研发投入,也许两年后市场复苏,就被竞争对手超过了。所以对于芯片和系统厂商来说,今天的研发投入不是说在解决今年的问题,而是解决两年后的问题,其中对新技术的研发投入就需要EDA的支撑。”

验证对芯片设计公司的重要性

据介绍,合见工软秉承以EDA为核心的工业软件战略,布局从芯片级的设计验证、系统级的封装设计一直到应用级,可以支撑超算、大数据、AI等方面的应用。而其中最重要的着力点就是验证领域,这是因为验证贯穿整个芯片设计流程,是花费时间、资源最多的步骤。

如下图所示,设计成本随着工艺节点的进步指数上升,芯片功能和集成度越来越高,所涉及的因素特别多,通过设计验证发现设计缺陷和错误愈发重要。

“以前的手机除了打电话,就是块砖。而现在则是一个漂亮的移动设备,还能拍照、看视频、玩大型游戏,功能不知道强过以前多少倍,这就是工艺演进带来的集成度提高和功能的拓展。” 但孙晓阳也同时提到,“这样的提升对芯片功耗、性能又带来很多挑战,验证成本在设计环节占的比例,正是在这种情况下逐渐变高的。”

验证随着IC设计发展逐渐细化,验证方法学及验证手段在不断发展,涉及到仿真验证(Simulation)、硬件仿真(Emulation)、原型验证(Prototyping)、虚拟原型(Virtual Prototyping)、形式验证(Formal)、静态时序分析(STA)等。

孙晓阳认为,对一家IC设计公司来说,验证是芯片开发最大的挑战,而工具和方法学是验证的基础。只有在验证上做得又快又好又完整,才能提升效率,因此要将各种验证方法结合,来提升验证的可预期性。“在保证激励及场景的真实性、准确度,跨平台的一致性、验证引擎的健壮性等验证的质量的同时,由于现在各种应用的不断变化,还要满足功能、性能、功耗、安全、软硬件协同等场景不一样的验证多样化需求。”

各种验证方法的优劣势

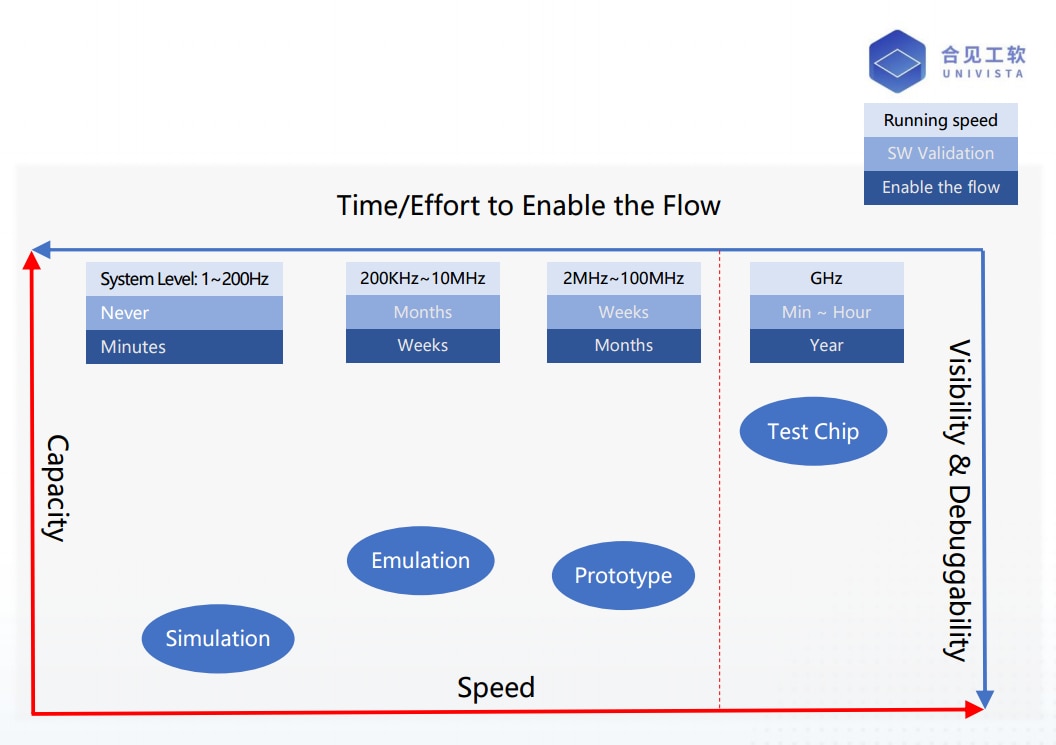

他认为,应该从几个维度来判断验证工具的好坏:

- 最上方的线代表花多大的力气才能把验证环境准备好开始跑;

- 最下方的线是工具运行的速度(Speed),例如一个小模块或整颗芯片,跑多久验证工作可以结束;

- 左边的线代表容量(Capacity),即一次验证能处理的是一个小模块、一个子系统还是一颗芯片;

- 右侧的线代表Visibility & Debuggability,意思就是跑验证会有错的地方,这个错有可能出现在验证本身的环境中,工程师要去调试它,“在验证领域还有一个非常通常的共识,调试会占验证70%的时间。所以在所有验证方法和手段中,可调试能力是非常重要的因素。”孙晓阳说到,“如果不可调试,即便能很快地把错误找到,找不到根本原因还是无法解决问题。”

从这四个维度可以发现,软件仿真(Simulation)的速度是最慢的,只能处理比较小规模的单元、模块和子系统初始化,但所有信号可见,所以可调试性非常好。

大概十年前左右,国内就开始大量使用硬件仿真加速器(Emulator),可以看做EDA工具用一个硬件系统,去仿真客户的设计。硬件仿真在速度和容量上都较软件仿真有所提升。

而传统上原型验证系统(Prototype),就是在芯片流片之前,把设计的一部分放到FPGA上验证,它的优势是速度可以跑得很快。

所以综合对比上面三种验证方式,传统的硬件仿真容量最大,原型验证虽然容量相对低一些,但可以跑得更快。随着软件的发展,原型验证和硬件仿真开始出现融合,界限已经不那么清晰了,业内一般把它们统称为硬件加速或者硬件原型系统。

在这样的大系统上,IC设计公司有机会把一颗芯片设计全部放到硬件上做验证,并且可以跟外界所有接口对接,去仿真和验证一个真实的场景,甚至跑真实的软件也变成可能。

当然,这种硬件原型系统还是比真实的芯片测试(Test Chip)要慢很多。举例来说,操作系统在笔记本电脑的真实芯片上可能是一分钟就跑起来了,但是到硬件仿真或者原型验证系统上要几十分钟或一个小时的水平。

“但它(原型验证系统)的突破在于相比其他几种验证方式,终于能把操作系统跑起来,能跑起来就意味着能跑应用。” 孙晓阳以手机行业最常见的跑分宣传为例,事实上手机芯片的公司在流片之前,真的会在原型验证或硬件仿真上跑分,这样才能在芯片回来之前就知道芯片的性能、功耗。“正是因为有了硬件仿真和原型验证的大量使用,才使得中国的半导体设计和制造企业可以高效率地去设计和生产这样的芯片。”

合见工软验证工具的优势

合见工软的产品覆盖了上面提到的验证范围和领域,算得上是一个全流程验证平台,包含了形式验证、数字仿真器和硬件仿真加速器和原型验证系统,以及虚拟原型验证。

所有这些验证引擎都是基于计算的,算出来对错后要进行调试,所以下图下方的Debug调试平台(Debugger),在所有验证工具判定“对或错”后,会转移到调试工具环境中寻找对错的原因。

由于验证是一个非常复杂的过程,所以需要做验证管理,合见工软做的整个验证管理系统从规划、出口标准去驱动整个验证流程,然后签核(signoff)和出口。

原型验证系统是合见工软引以为傲的产品,满足了刚才上文提到的验证质量、效率、可预期性等因素,当前面对超大规模CPU/HPC芯片软硬件协同验证挑战,还要支持更大的容量。

“一款验证工具的容量、性能,代表了实现快速设计移植和启动速度的能力。直接反应出花多少力气能把一个设计在验证平台上跑起来。再来就是调试手段能否实现芯片的快速版本迭代,能否支持十亿门的大规模设计等。”孙晓阳说到。

目前,合见工软新一代时序驱动(Timing-Driven)高性能原型验证系统Advanced Prototyping System(UV APS)已经实现4-100颗VU19P FPGA级联,这也是赛灵思(Xilinx)最成熟、最大的一颗FPGA。据悉合见工软在客户端的实际部署总数已经达到160颗,按照单套设备四颗FPGA 10亿门计算,大概支持40亿门的规模,最大容量支持25套设备级联。

UV APS全新功能升级版还集成了先进的时序驱动全流程编译软件APS Compiler,自研前端编译处理引擎可以快速实现多种类型设计的移植和启动,降低用户初期部署成本。APS Compiler内嵌的时序驱动引擎,通过大范围TDM ratio自动优化求解,面对10亿门以上设计也能自动化快速实现更优性能。

全新版的UV APS同时还提供了寄存器回读和深度调试等多样化调试手段,同时提供了面向多种行业应用的原型验证子卡及快速定制服务,支持PCIe Gen5、DDR5、HBM2e等高性能接口速率适配,支持虚拟原型混合验证等一系列适配多种典型应用的解决方案,应对原型验证的各种复杂场景需求。

“另外一些客户在做原型验证之前,并不是所有RTL代码都是准备好的,有可能一部分准备好,一部分还没有。这时候可以一部分跑在原型验证系统服务器上,另一部分用硬件模型来替代做Hybrid(联合仿真和验证)。”孙晓阳说到,“这样可以实现验证左移,不一定等到所有代码都实现完了再开始验证工作,可以更早地开始验证和软件开发,缩短产品上市时间。”

除了验证,封装等应用也非常重要,所以合见工软也在PCB和封装领域做了布局。UniVista Integrator(UVI)增强版完善了先进封装设计在IC、Package、PCB设计协同的Sign-off功能,支持全面的系统互连一致性检查(System-Level LVS)。据称,合见工软在仿真生产设计环境所得准确率、覆盖率均达100%,该版本将检查效率提高了96倍,从上一版检查600,000管脚8分钟提升至5秒钟;同时,在图形显示性能、效果与精度上都有大幅提升。EDMPro则是基于规则的库管理签核工具。

结语

除了工具以外,现在的芯片大量使用了IP。典型的SoC会有ISP、NPU、GPU、CPU等等,还有外围各种高速接口、低速接口、Memory等等。所以合见工软除了EDA工具,也在积极布局IP领域。今年5月,合见工软收购北京诺芮集成电路设计有限公司,就是其IP产品线的战略布局之一,目前做了以太网控制器、PCIe等等IP产品;Memory方面也做了DDR等解决方案;另外半导体工艺的演进,也催生了Chiplet这种新的封装方式,UCIe接口协议就是用于支持Chiplet异构封装的。

据孙晓阳介绍,合见工软这些IP相关产品从两年半前已经陆续针对一些客户做了部署,也得到了认可。

不过,近期国内EDA行业最受瞩目的还是合见工软与华大九天联合发布的全国产化完整数模混合信号设计仿真解决方案。一颗芯片中除了数字部分,还有模拟部分,最典型的例子就是手机芯片,除了数字部分的CPU,还有模拟的基带芯片和天线RF部分。

“通常来讲,现在的芯片大多是‘大A(Analog)小D(Digital)’,也有场景是‘大D小A’。”谈到和华大九天的合作,孙晓阳表示,“华大九天做高速高精度并行晶体管级电路模拟仿真(Empyrean ALPS),我们做高性能数字仿真(UVS),共同在客户端打通接口。在两者结合的过程中,最主要解决的是仿真精度的问题,所以通过这个模型,来构建两者之间的桥梁。”

最后孙晓阳指出,合见工软的愿景就是在EDA产业覆盖从芯片、系统到应用层次,所以也希望能够团结拥有更多的人才,一起来打造成熟的国内EDA解决方案和生态。

技术咨询

技术咨询 代买器件

代买器件 商务客服

商务客服 研发客服

研发客服